Filtro de Saída (KD PCM): mudanças entre as edições

Sem resumo de edição |

m Filtro de Saída (KD PCM) movido para Filtro de Saída (KD PCM) |

| (Uma revisão intermediária pelo mesmo usuário não está sendo mostrada) | |

(Sem diferença)

| |

Edição atual tal como às 07h18min de 16 de novembro de 2006

1 Descrição

O módulo em questão é responsável pela filtragem das componentes freqüênciais altas que são geradas no processo de decodificação PCM. Ele tem como característica a atenuação de freqüências acima de 3400Hz, como determina o diagrama de bode da ITU-T.

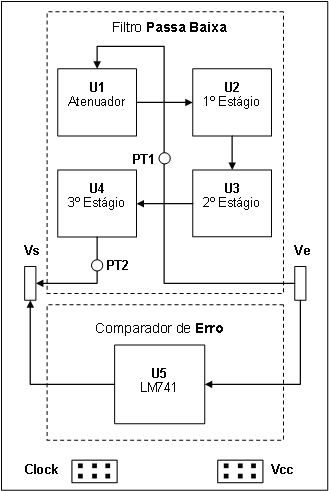

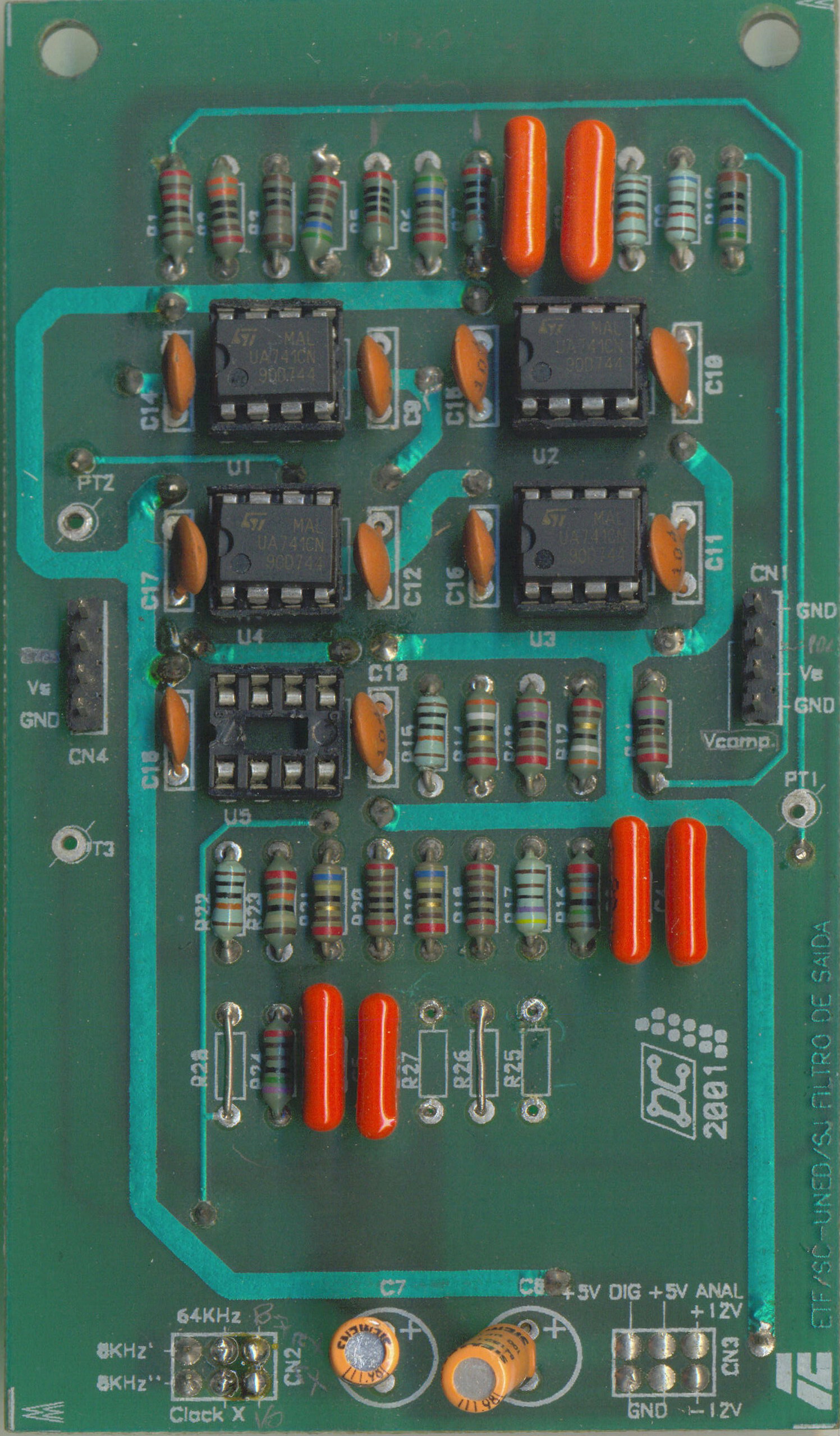

O circuito de Filtragem do módulo Filtro de Saída é exatamente igual ao circuito Filtro Passa Baixa de 6ª Ordem do módulo Filtro de Entrada. O módulo também possui anexada a placa um estágio Comparador de Erro, que seria utilizado para comparar o sinal de entrada com o de saída.

2 Foto e Diagrama

O circuito pode ser dividido em dois blocos independentes, o primeiro é um Filtro Passa Baixa de 2ª Ordem, composto por um Amplificador Operacional e um de Filtro RC (Resistor + Capacitor), e o segundo é um circuito Comparador de Erro, constituído por um Amp-Op configurado como “comparador de tensão”.

|

|