Mudanças entre as edições de "Como evitar o uso da lógica combinacional no reset síncrono"

Ir para navegação

Ir para pesquisar

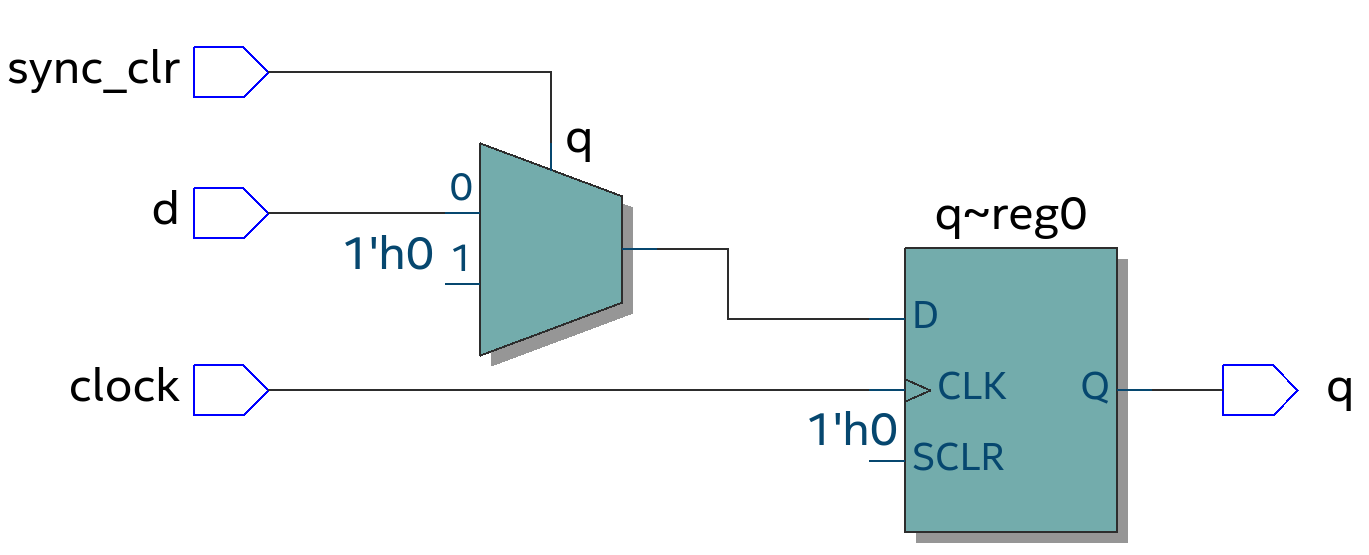

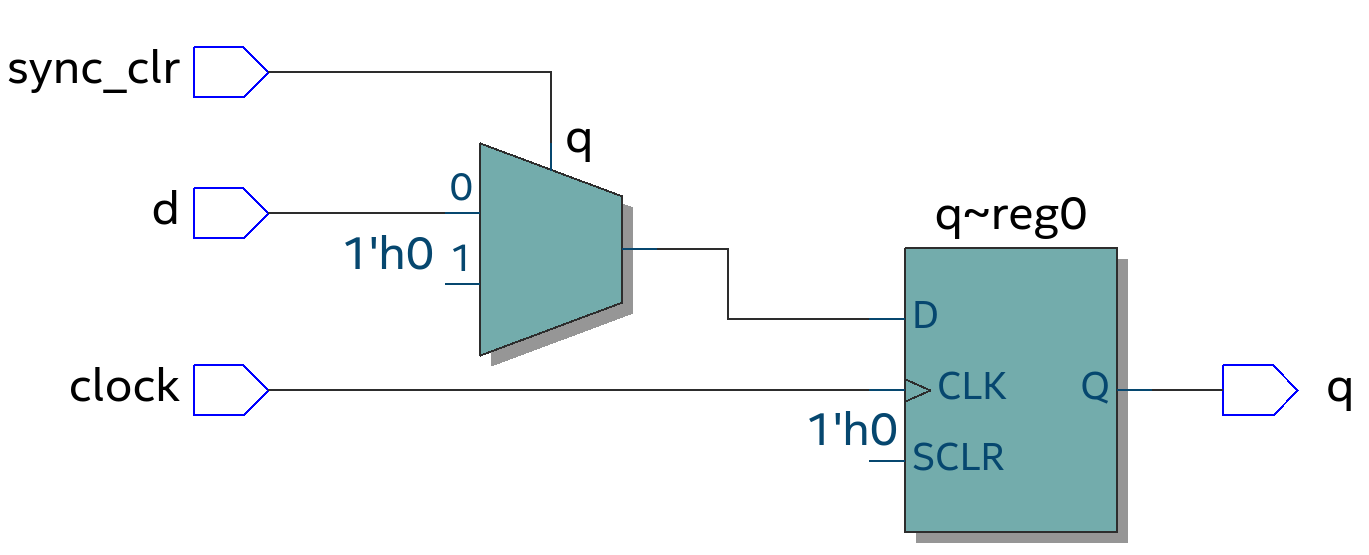

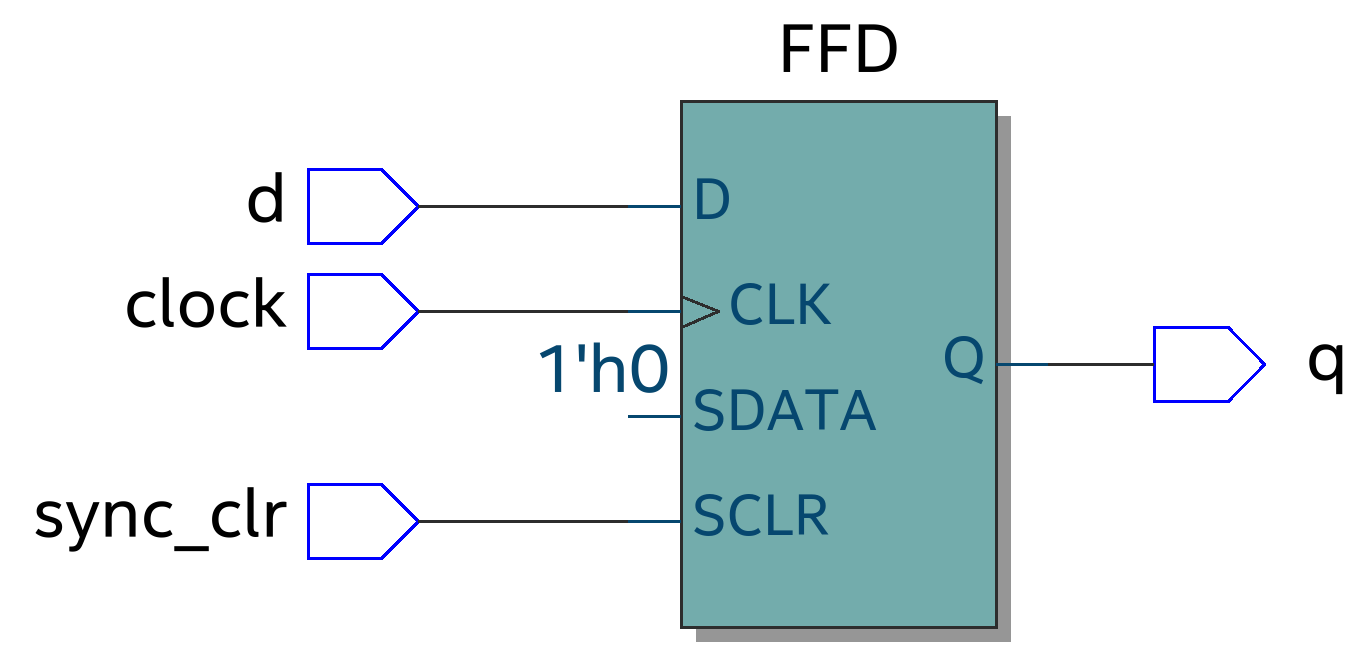

Figura 1 - RTL do flip-flop D com reset síncrono

Fonte: Elaborado pelo autor.

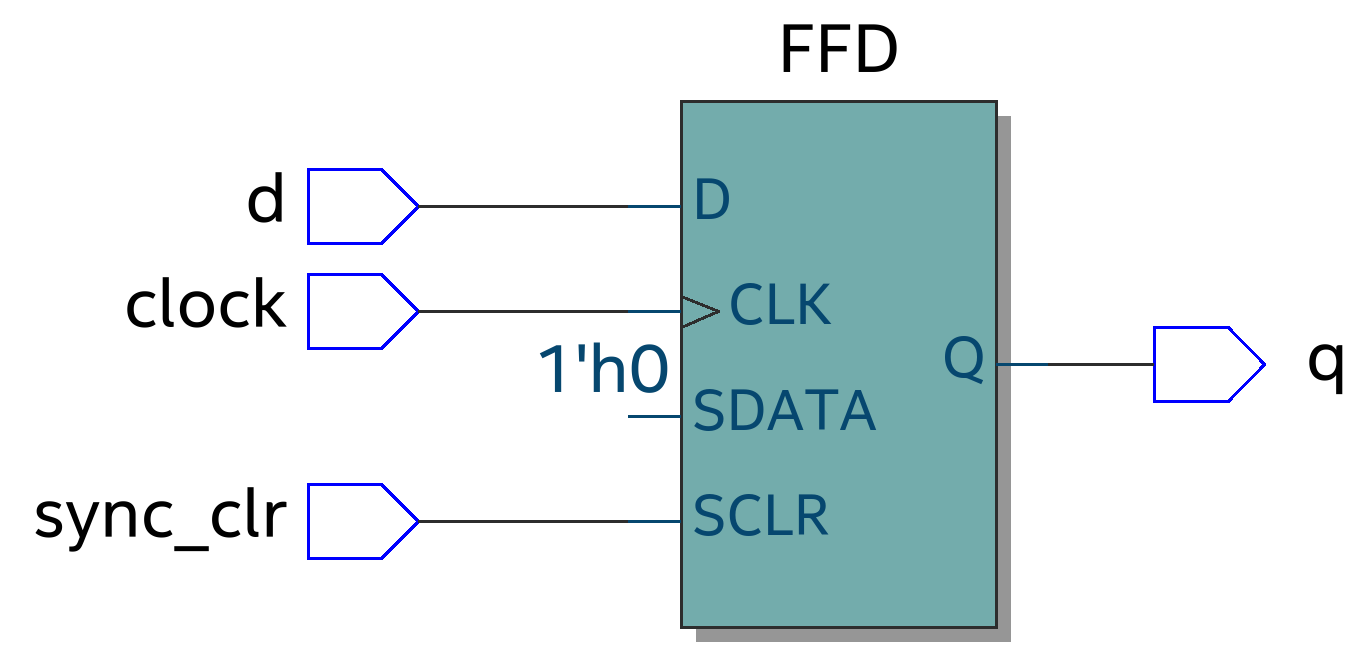

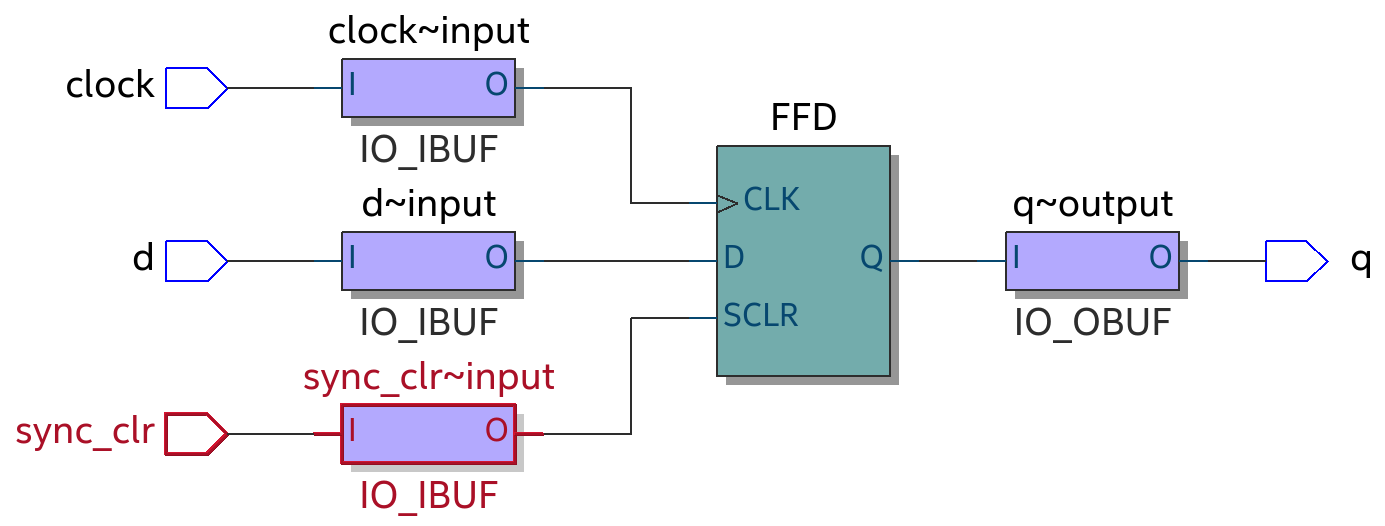

Figura 2 - RTL de Flip-flop D com reset síncrono (usando o componente DFFEAS)

Fonte: Elaborado pelo autor.

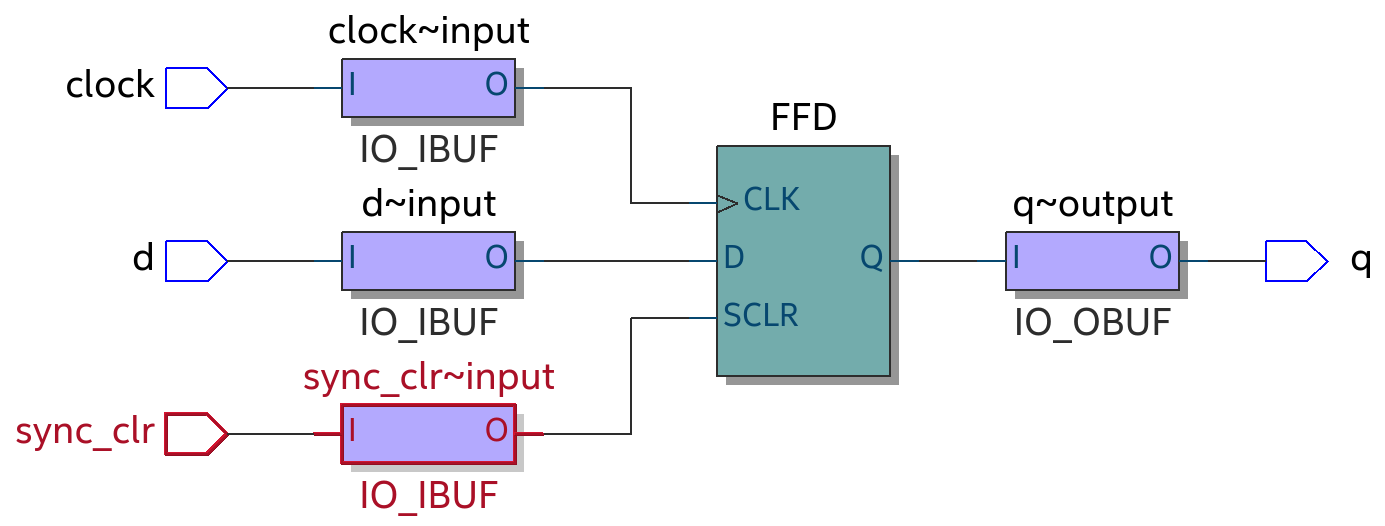

Figura 3 - Technology Map do flip-flop D com reset síncrono (usando o componente DFFEAS)

Fonte: Elaborado pelo autor.

| (Uma revisão intermediária pelo mesmo usuário não está sendo mostrada) | |||

| Linha 1: | Linha 1: | ||

| − | ; | + | ;Usando lógica combinacional no clear sincrono: |

Um código em VHDL genérico resultará na maioria das vezes na adição de um circuito combinacional para a entrada clear sincrono. | Um código em VHDL genérico resultará na maioria das vezes na adição de um circuito combinacional para a entrada clear sincrono. | ||

| − | {{fig|1|RTL do | + | {{fig|1|RTL do flip-flop D com reset síncrono| FF_D_RST_SINC.png| 800 px | }} |

;evitando a lógica combinacional no clear sincrono | ;evitando a lógica combinacional no clear sincrono | ||

Para evitar o uso do circuito combinacional para a entrada CLEAR_SYNC no flip_flop D é necessário utilizar a ''Low-Level Primitives'' '''DFFEAS''' | Para evitar o uso do circuito combinacional para a entrada CLEAR_SYNC no flip_flop D é necessário utilizar a ''Low-Level Primitives'' '''DFFEAS''' | ||

| − | {{fig| | + | {{fig|2|RTL de Flip-flop D com reset síncrono (usando o componente DFFEAS) | FF_D_SCLR.png| 400 px | }} |

| − | {{fig| | + | {{fig|3|Technology Map do flip-flop D com reset síncrono (usando o componente DFFEAS)| TM_FF_D_SCLR.png| 800 px | }} |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

Edição atual tal como às 14h53min de 18 de outubro de 2023

- Usando lógica combinacional no clear sincrono

Um código em VHDL genérico resultará na maioria das vezes na adição de um circuito combinacional para a entrada clear sincrono.

Figura 1 - RTL do flip-flop D com reset síncrono

- evitando a lógica combinacional no clear sincrono

Para evitar o uso do circuito combinacional para a entrada CLEAR_SYNC no flip_flop D é necessário utilizar a Low-Level Primitives DFFEAS

Figura 2 - RTL de Flip-flop D com reset síncrono (usando o componente DFFEAS)

Figura 3 - Technology Map do flip-flop D com reset síncrono (usando o componente DFFEAS)

library ieee;

use ieee.std_logic_1164.all;

entity FF_D is

port

(

clock : in STD_LOGIC;

sync_clr : in STD_LOGIC;

d : in STD_LOGIC;

q : out STD_LOGIC := '0');

end entity;

architecture ifsc of FF_D is

component DFFEAS

port

(

d : in STD_LOGIC;

clk : in STD_LOGIC;

clrn : in STD_LOGIC;

prn : in STD_LOGIC;

ena : in STD_LOGIC;

asdata : in STD_LOGIC;

aload : in STD_LOGIC;

sclr : in STD_LOGIC;

sload : in STD_LOGIC;

q : out STD_LOGIC);

end component;

begin

FFD : DFFEAS

port map

(

d => d,

clk => clock,

clrn => '1',

prn => '1',

ena => '1',

asdata => '0',

aload => '0',

sclr => sync_clr,

sload => '0',

q => q);

end architecture;

- Ler

- Designing with Low-Level Primitives User Guide pag.2–28 - Altera Corporation 2007