EDI018702 2019 2 AULA04: mudanças entre as edições

| (3 revisões intermediárias por 2 usuários não estão sendo mostradas) | |||

| Linha 61: | Linha 61: | ||

## Fazer a ligação das Saídas Q e Q\ aos LEDs; | ## Fazer a ligação das Saídas Q e Q\ aos LEDs; | ||

#Testar a tabela verdade. | #Testar a tabela verdade. | ||

==Procedimento== | ==Procedimento== | ||

| Linha 124: | Linha 96: | ||

<center> | <center> | ||

Figura 4 - Esquemático do CI 7408 - Portas AND. | Figura 4 - Esquemático do CI 7408 - Portas AND. | ||

</center> | </center> | ||

=Relatório= | =Relatório= | ||

O relatório deverá ser entregue até o dia da primeira avaliação. As equipes que não terminaram as duas partes do experimento, | O relatório deverá ser entregue até o dia da primeira avaliação (10/09/2019). As equipes que não terminaram as duas partes do experimento, poderão fazer o relatório da parte 1 e relatar o que aconteceu com a parte 2. | ||

| Linha 145: | Linha 107: | ||

;Critérios avaliativos: | ;Critérios avaliativos: | ||

::Prática (montagem/equipe): | ::Prática (montagem/equipe): 4 | ||

::Circuito completo (todos): | ::Circuito completo (todos): 3 | ||

::Resultados e discussões : | ::Resultados e discussões : 3 | ||

::'''Resultado''': 10 | ::'''Resultado''': 10 | ||

Edição atual tal como às 19h16min de 3 de setembro de 2019

1 Laboratório 1

O primeiro experimento da turma de Digital 2 da Engenharia vai ser realizado na LabMIC (sala 104) pela tarde entre 13h30min e 15h20min com a Turma 1 e entre 15h40min às 17h30min com a Turma 2. O experimento está dividido em duas etapas, sendo que na primeira parte você vai testar o funcionamento de um Latch RS controlado feito a partir das portas lógicas AND (E) e NOR (NOU) comprovando a tabela verdade. Na segunda etapa você vai testar o funcionamento dos flip-flops tipo D na configuração mestre-escravo, comprovando a teoria envolvida.

1.1 Parte I - Latch RS

- Objetivo

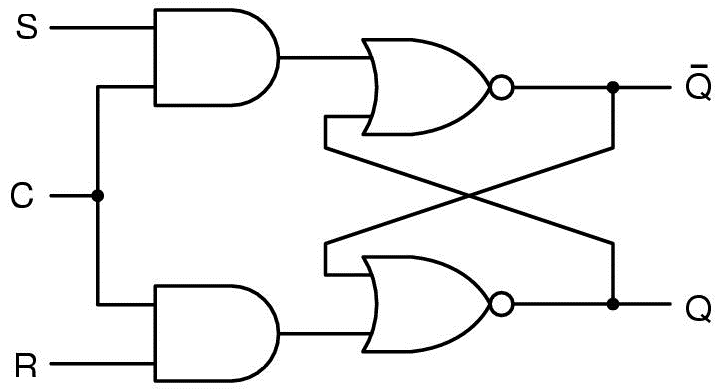

Testar o funcionamento de um circuito latch RS controlado, feito a partir das portas lógicas AND (E) e NOR (NOU) como mostra a Figura 1.

Figura 1 - Latch RS controlado.

| C | R | S | Q |

|---|---|---|---|

| 0 | X | X | Qa |

| 1 | 0 | 0 | Qa |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | proibido |

[*]Qa: saída do estado anterior.

1.2 Procedimento

- Formar até 10 equipes com 2 alunos;

- Desenhar as ligações utilizando o esquemático dos CIs;

- Montar o circuito na banca digital, os CIs devem ficar com o chanfro voltado para cima;

- Fazer a ligação de VCC e GND;

- Fazer a ligação entre as portas lógicas dos circuitos integrados;

- Fazer a ligação de R, S e C com chaves seletoras;

- Fazer a ligação das Saídas Q e Q\ aos LEDs;

- Testar a tabela verdade.

1.3 Procedimento

- Mesmas equipes;

- Desenhar as ligações utilizando o esquemático dos CIs;

- Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima;

- Fazer a ligação de VCC e GND

- Fazer a ligação de PRE e CLR nas chaves seletoras.

- Fazer a ligação entre as FF passando pela inversora

- Fazer a ligação de D e Clock com chaves seletoras

- Fazer a ligação das Saídas Qm e Qs aos LEDs

- Construir a tabela verdade para Qm e Qs a partir da simulação dos pulsos de clock (ligar e desligar a chave).

- Ligar o clock a uma frequência de 1Hz (se estiver disponível) e ver o que acontece.

2 Material Utilizado

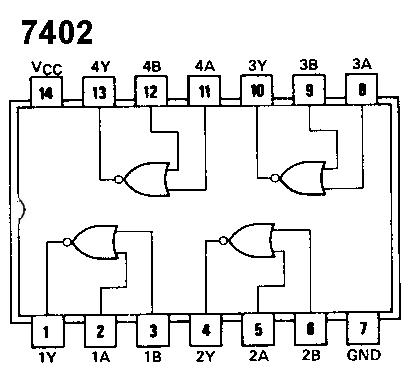

- CI 7402 (NOR) (Figura 3)

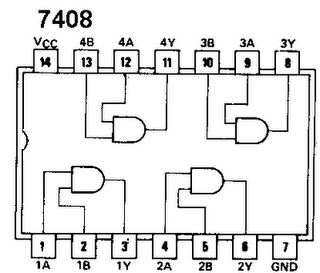

- CI 7408 (AND) (Figura 4)

- CI 7404 (INV) (Figura 5)

- CI 7474 (FF tipo D) (Figura 6)

- fios diversos

- bancada digital

- alicates

3 Esquemáticos dos CIs

Figura 3 - Esquemático do CI 7402 - Portas NOR.

Figura 4 - Esquemático do CI 7408 - Portas AND.

4 Relatório

O relatório deverá ser entregue até o dia da primeira avaliação (10/09/2019). As equipes que não terminaram as duas partes do experimento, poderão fazer o relatório da parte 1 e relatar o que aconteceu com a parte 2.

4.1 Relatório Simplificado

- Critérios avaliativos

- Prática (montagem/equipe): 4

- Circuito completo (todos): 3

- Resultados e discussões : 3

- Resultado: 10