Mudanças entre as edições de "DIG222802 AULA02"

| Linha 112: | Linha 112: | ||

Figura 2 - Flip-flop tipo D na configuração mestre–escravo. | Figura 2 - Flip-flop tipo D na configuração mestre–escravo. | ||

</center> | </center> | ||

| + | |||

| + | ==Tabela Verdade== | ||

| + | |||

| + | {| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

| + | ! style="background:#4069e1; width: 20px;" | D | ||

| + | ! style="background:#4069e1; width: 20px;" | Q | ||

| + | ! style="background:#4069e1; width: 20px;" | Q\ | ||

| + | |- | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | |} | ||

==Material Utilizado== | ==Material Utilizado== | ||

Edição das 11h32min de 5 de abril de 2016

Apresentação

Circuitos Sequencias

Síncrono

Exercício de Fixação

Assíncrono

Latches

RS

Latch D

Laboratório 1

O primeiro experimento da turma de Digital 2 da Engenharia vai ser realizado na LabELETRO entre 16h às 17h45min. Está dividido em duas etapas: A primeira trata-se de testar o funcionamento de um latch RS controlado feito a partir das portas lógicas AND (E) e NOR (NOU) comprovando a tabela verdade. A segunda etapa é a de testar o funcionamento dos flip-flops D na configuração mestre-escravo também comprovando a tabela verdade.

Parte I

- Objetivo

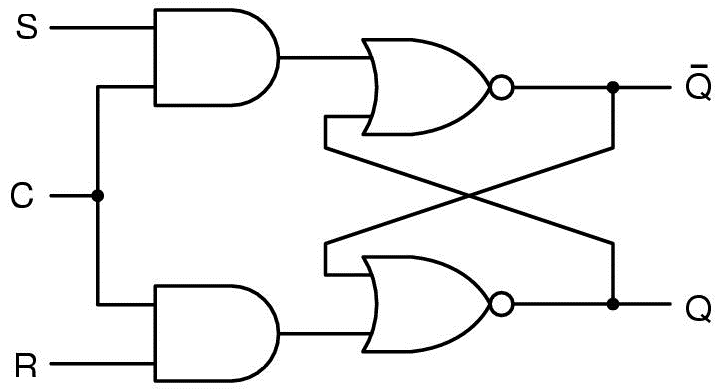

Testar o funcionamento de um circuito latch RS controlado, feito a partir das portas lógicas AND (E) e NOR (NOU) como mostra a Figura 1.

Figura 1 - Latch RS controlado.

Tabela Verdade

| C | R | S | Q |

|---|---|---|---|

| 0 | X | X | Qa |

| 1 | 0 | 0 | Qa |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | proibido |

- Qa: saída do estado anterior.

Procedimento

- Formar as 8 equipes com 2 ou 3 integrantes;

- Desenhar as ligações já utilizando o esquemático dos CIs;

- Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima;

- Fazer a ligação de VCC e GND

- Fazer a ligação entre as portas lógicas dos circuitos integrados

- Fazer a ligação de R, S e C com chaves seletoras

- Fazer a ligação das Saídas Q e Q\ aos LEDs

- Testar a tabela verdade.

Parte II

- Objetivo

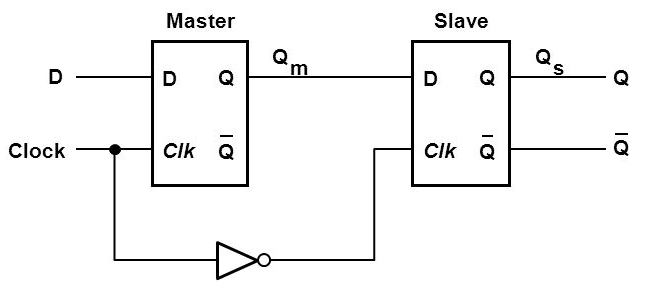

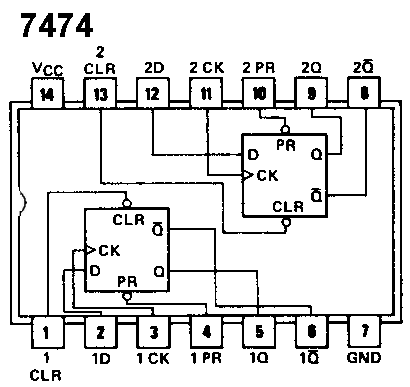

- Testar o funcionamento de um Flip-flop D na configuração mestre–escravo a partir do CI 7474 e uma porta inversora. O circuito a ser montado pode ser visto na Figura 2.

Figura 2 - Flip-flop tipo D na configuração mestre–escravo.

Tabela Verdade

| D | Q | Q\ |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 1 | 0 |

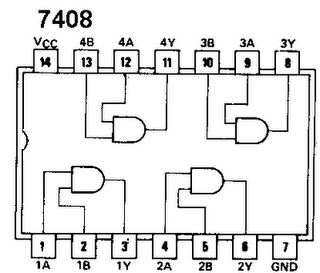

Material Utilizado

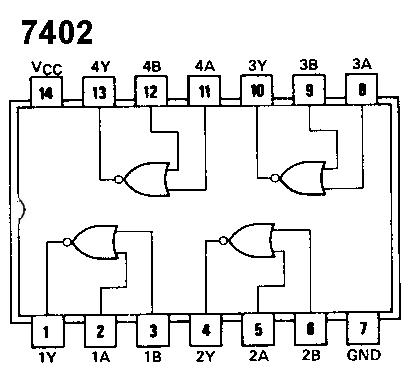

- CI 7402 (NOR)

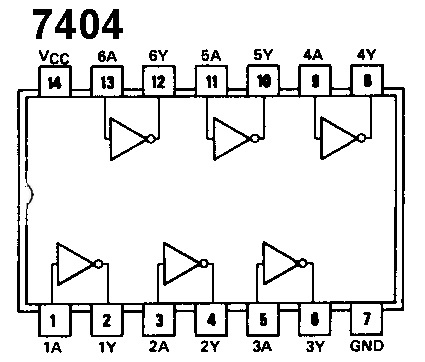

- CI 7404 (INV)

- CI 7408 (AND)

- CI 7474 (FF tipo D)

- fios diversos

- bancada digital

Circuitos

Figura 3 - Esquemático do CI 7402 - Portas NOR.

Figura 4 - Esquemático do CI 7404 - Portas Inversoras.

Figura 5 - Esquemático do CI 7408 - Portas AND.

Figura 6 - Esquemático do CI 7474 - Dois FF tipo D.

Equipes

Os alunos serão divididos em 8 equipes com 2 ou 3 integrantes. Foi disponibilizado diagrama no quadro com a montagem dos circuitos.

Referências

[1] http://www.inf.ufsc.br/~guntzel/isd/isd4.pdf

[2] TOCCI, Ronald J.; WIDMER N. S.; GREGOGRY L. M. Sistemas digitais: princípios e aplicações. São Paulo: Prentice Hall, 2003.

[3] http://www.cburch.com/logisim/docs/2.7/pt/html/libs/mem/flipflops.html

| << | <> | >> |

|---|