Criando formas de ondas no Modelsim

Video motivational para apreender FPGA, VHDL Microsoft's Bing* Intelligent Search with Intel® FPGAs

- Código de 4 Flip-Flop D

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY n_flip_flop IS

GENERIC (N : natural := 4);

PORT (d : IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0));

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE ifsc OF n_flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= (others => '0');

ELSIF rising_edge(clk) THEN

q <= d;

END IF;

END PROCESS;

END;

- Simulação com QSIM

Uma vez compilado o código acima no Quartus, é possível fazer a simulação funcional e com timing usando o simulador QSIM. O resultado obtido é mostrado a seguir. Para realizar a simulação é necessário inserir graficamente os sinais de entrada clk, rst e d.

Figura 1 - Simulação Funcional de 4 Flip-Flop D 100ns

Figura 2 - Simulação Temporal de 4 Flip-Flop D 100ns

Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças.

IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possível verificar se o circuito atende as restrições de tempo.

- Para definir as restrições de tempo do clock por exemplo, pode ser adicionado um arquivo .sdc ao projeto definindo a frequência do clock esperada através da seguinte linha:

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

- Simulação funcional usando o Modelsim

Usando o Modelsim é também possível realizar a simulação gerando os sinais passo a passo com os comandos force. No entanto, também é possível gerar antecipadamente todos os sinais de entrada antecipadamente usando os comandos wave create e wave modify:

- PASSO 1a: Abra o Modelsim

/opt/altera/13.0sp1/modelsim_ae/bin/vsim

- PASSO 1b: Resete o Layout do Modelsim (caso tenha feito alguma modificação e não saiba como retornar ao original) (Layout > Reset).

- PASSO 1c: Mude para a pasta onde está o projeto, usando a barra de menu (File > Change Directory... [Escolha a pasta]. Ou via linha de comando na janela de transcript.

cd /home/nome_usuario/nome_pasta/...

- PASSO 1d: Confira se está na pasta correta

pwd ls

- PASSO 1e: Compile o arquivo vhd do projeto. (Compile > Compile... selecione [n_Flip_Flop.vhd] e clique em [Compile]). Responda a [Create Library?] com [Yes]. Em seguida clique em [Done]. Ou

vlib work vcom -work work n_flip_flop.vhd

- PASSO 1f: Inicie a simulação (Simulation > Start Simulation... na aba [Design] selecione a Entity [n_Flip_Flop] no Package work e clique em [OK]. Ou

vsim work.n_flip_flop

- PASSO 2a: Inicie a criação dos sinais de entrada da Entity. Clique_direito sobre o nome da Entity na janela Library, e em seguida selecione [Create Wave]. Ou

wave create -pattern none -portmode in -language vhdl -range N 1 /n_flip_flop/d wave create -pattern none -portmode in -language vhdl /n_flip_flop/clk wave create -pattern none -portmode in -language vhdl /n_flip_flop/rst wave create -pattern none -portmode out -language vhdl -range 1 N /n_flip_flop/q

Será aberta uma janela [Wave] na qual irão ser mostrados as 3 portas de entrada da Entity e a porta de saída. Clique sobre o sinal da porta de saída e [Delete], pois esse sinal não será editado. Aproveite para arrastar com o mouse os sinais na janela Wave para ficarem na seguinte ordem: rst, clk, d.

- PASSO 2b: Crie o sinal de rst como um pulso de valor '1' entre 20 e 30 ns.

Clique_direito sobre o sinal rst e selecione [Edit > Create/Modify Waveform] e escolha [Patterns = Constant], [Start Time = 0] [End Time = 1000] [Time Unit = ps] e clique em [Next], [Value = 0] e clique em [Finish]. Ou

wave modify -driver freeze -pattern constant -value 0 -starttime 0ps -endtime 1000ps Edit:/n_flip_flop/rst

Clique_direito sobre o sinal rst e selecione [Edit > Create/Modify Waveform] e escolha [Patterns = Constant], [Start Time = 20] [End Time = 30] [Time Unit = ps] e clique em [Next], [Value = 1] e clique em [Finish]. Ou

wave modify -driver freeze -pattern constant -value 1 -starttime 20ps -endtime 30ps Edit:/n_flip_flop/rst

- PASSO 2c: Crie o sinal de clk com um período de 100ps, iniciando em alto.

Clique_direito sobre o sinal clk e selecione [Edit > Create/Modify Waveform] e escolha [Patterns = Clock], [Start Time = 0] [End Time = 1000] [Time Unit = ps] e clique em [Next], [Initial Value = 1], [Clock Period = 100ps], [Duty Cycle = 50] e clique em [Finish]. Ou

wave modify -driver freeze -pattern clock -initialvalue 1 -period 100ps -dutycycle 50 -starttime 0ps -endtime 1000ps Edit:/n_flip_flop/clk

- PASSO 2d: Crie o sinal de d como sendo uma contagem entre "0000" e "1111"

Clique_direito sobre o sinal d e selecione [Edit > Create/Modify Waveform] e escolha [Patterns = Counter], [Start Time = 0] [End Time = 1000] [Time Unit = ps] e clique em [Next], [Start Value = 0000], [End Value = 1111], [Time Period = 120ps], [Counter Type = Range], [Count Direction = Up], [Step Count = 1], [Repeat = Forever] e clique em [Finish]. Ou

wave modify -driver freeze -pattern counter -startvalue 0000 -endvalue 1111 -type Range -direction Up -period 120ps -step 1 -repeat forever -range 4 1 -starttime 0ps -endtime 1000ps Edit:/n_flip_flop/d

- PASSO 2e: Insira o sinal de saída q na janela Wave.

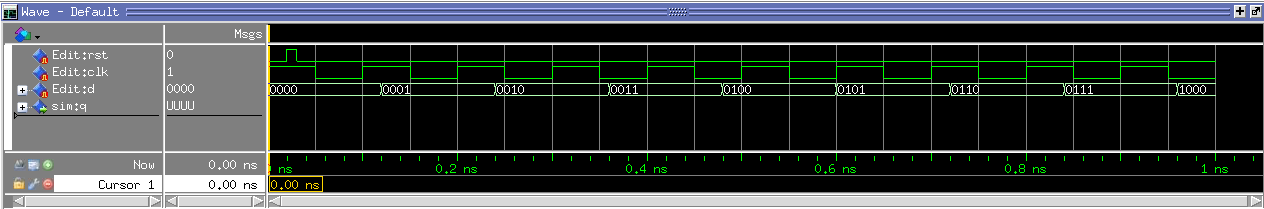

Clique sobre o sinal q na janela Objects e solte-o na janela Wave. Ao final desses passos a janela Wave deverá estar conforme mostrado abaixo:

Figura 2.8 - Edição do Waveform de 4 FF 1000ns no Modelsim

- PASSO 3: Realize a simulação de 1000 ps

- Opção 1: Clique 10 vezes sobre o icone [Run] ou [F9]

- Opção 2: Digite 10 vezes o comando run na janela Transcript (cada run dura o tempo indicado ao lado esquerdo do icone [Run]

- Opção 3: Digite o comando run 1000 ps

- Opção 4: Digite o comando run -all (será executado o tempo necessario para concluir os sinais que foram desenhados.

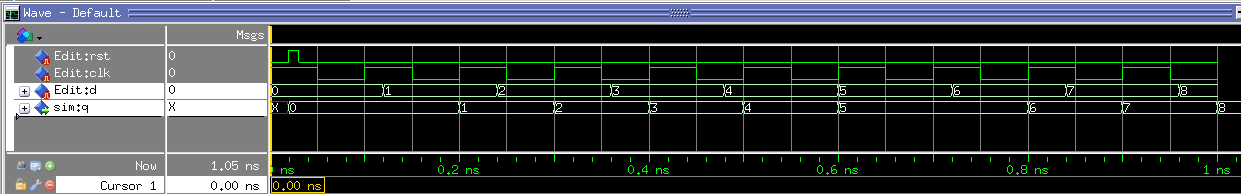

- PASSO 4: Análise da simulação

Selecione com o shift_clique_esquerdo do mouse os sinas d e q (barramentos de 4 bits) e em seguida clique_direito e selecione [radix > unsigned]. A janela Wave deverá estar conforme mostrado abaixo:

Figura 3 - Simulação funcional de 4 FF 1000ns no Modelsim

- Note que a saída q está com (Forcing Unknown - (X em vermelho) entre 0 e 20 ps. Isso ocorre pois antes de aplicar o RESET o Flip Flop tem valor desconhecido. Por isso é sempre importante aplicar um RESET logo ao iniciar a simulação de um circuito sequencial.

- Note que as mudanças na saída q ocorrem sempre na transição de subida do sinal do CLOCK. Mudanças que ocorrem na entrada do sinal d não afetam a saída.

- Experimente mudar o sinal de entrada d com períodos diferentes (e.g. 60ps) e repita a simulação.

- Inclua um pequeno pulso de RESET na instante 530ps.

- PASSO 5: Criação de um teste bench com arquivo .do

Use os comandos da janela de transcript para criar um arquivo tb_FF.do que permite repetir de forma automatica o teste realizado.

################################

# FILE : tb_FF.do

# AUTOR: Marcos Moecke

# DATA : 14 de agosto de 2019

################################

#criacao da library work

vlib work

#compilacao da entity nome.vhd (nao necessita ser compilado no quartus II)

vcom -work work n_flip_flop.vhd

#simulacao na entity nome.vhd

vsim work.n_flip_flop

#edicao do sinal rst

wave create -pattern none -portmode in -language vhdl /n_flip_flop/rst

wave modify -driver freeze -pattern constant -value 0 -starttime 0ps -endtime 1000ps Edit:/n_flip_flop/rst

wave modify -driver freeze -pattern constant -value 1 -starttime 20ps -endtime 30ps Edit:/n_flip_flop/rst

#edicao do sinal clock

wave create -pattern none -portmode in -language vhdl /n_flip_flop/clk

wave modify -driver freeze -pattern clock -initialvalue 1 -period 100ps -dutycycle 50 -starttime 0ps -endtime 1000ps Edit:/n_flip_flop/clk

#edicao do sinal d

wave create -pattern none -portmode in -language vhdl -range N 1 /n_flip_flop/d

wave modify -driver freeze -pattern counter -startvalue 0000 -endvalue 1111 -type Range -direction Up -period 120ps -step 1 -repeat forever -range 4 1 -starttime 0ps -endtime 1000ps Edit:/n_flip_flop/d

#inclusao do sinal de saida q (como BINARY)

add wave -position end sim:/n_flip_flop/q

#inclusao do sinal de saida q (como UNSIGNED)

add wave -position end -radix hexadecimal sim:/n_flip_flop/q

#execucao da simulacao inteira

run -all

#reinicio do tempo e simulacao

restart

#execucao da simulacao por 1000 ps

run 1000 ps

- Para conhecer melhor o MODELSIM GRAPHICAL WAVEFORM EDITOR, consulte o INTRODUCTION TO SIMULATION OF VHDL DESIGNS USING MODELSIM GRAPHICAL WAVEFORM EDITOR