Mudanças entre as edições de "DLP29007-Engtelecom(2017-1) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

| Linha 1: | Linha 1: | ||

| − | + | {{DivulgueEngtelecom}} | |

| − | + | ==Unidade 1== | |

| − | |||

| − | |||

;Aula 6 (15 Mar) - Marcos: | ;Aula 6 (15 Mar) - Marcos: | ||

* Processo de Síntese do código VDHL | * Processo de Síntese do código VDHL | ||

| Linha 23: | Linha 21: | ||

::Ver também os slides [http://docente.ifsc.edu.br/arliones.hoeller/dlp2/slides/dlp29007-lecture02-synthesis.pdf Unidade 2: Processo de Síntese do código VDHL] | ::Ver também os slides [http://docente.ifsc.edu.br/arliones.hoeller/dlp2/slides/dlp29007-lecture02-synthesis.pdf Unidade 2: Processo de Síntese do código VDHL] | ||

| − | + | ==Unidade 3== | |

;Aula 10 e 11 (28 e 29 Mar) - Marcos: | ;Aula 10 e 11 (28 e 29 Mar) - Marcos: | ||

* Eficiência de Circuitos Combinacionais | * Eficiência de Circuitos Combinacionais | ||

| Linha 52: | Linha 50: | ||

::*Compare seus resultados com o dos colegas que escolheram outras regiões do chip. | ::*Compare seus resultados com o dos colegas que escolheram outras regiões do chip. | ||

| − | + | ==Unidade 4== | |

;Aula 13 (11 Abr) - Marcos: | ;Aula 13 (11 Abr) - Marcos: | ||

* Eficiência de Circuitos Sequenciais | * Eficiência de Circuitos Sequenciais | ||

| Linha 276: | Linha 274: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | ==Unidade 8== | |

;Aula 24 (13 jun): | ;Aula 24 (13 jun): | ||

*Projeto Hierárquico | *Projeto Hierárquico | ||

| Linha 308: | Linha 306: | ||

::*Exemplo L14.16 (up_or_down) X L14.17 (up_and_down) X L14.20 (up + down) | ::*Exemplo L14.16 (up_or_down) X L14.17 (up_and_down) X L14.20 (up + down) | ||

::Ver pag. 499 a 543 de <ref name="PONG2006a" /> | ::Ver pag. 499 a 543 de <ref name="PONG2006a" /> | ||

| + | |||

| + | ==Referências Bibliográficas:== | ||

| + | <references/> | ||

| + | |||

| + | {{ENGTELECO}} | ||

Edição das 13h24min de 22 de agosto de 2017

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

Unidade 1

- Aula 6 (15 Mar) - Marcos

- Processo de Síntese do código VDHL

- Limitações dos softwares de EDA: Computabilidade, Complexidade Computacional

- Realização dos operadores VHDL: simplificações para operando constante

- Realização dos tipos de dados: Alta impedância 'Z' -> buffer tri-state;

- Realização dos tipos de dados: uso de don't care '-'

- Ver pag. 125 a 137 de [1]

- Aula 7 (21 Mar) - Marcos

- Processo de Síntese do código VDHL: Analise das temporizações:

- Tempos de propagação, caminho crítico, caminho falso,

- Síntese com restrições temporais,

- Perigos/Armadilhas (Glitches estáticos e dinâmicos, circuitos sensíveis ao atraso)

- Ver pag. 137 a 162 de [1]

- Ver também os slides Unidade 2: Processo de Síntese do código VDHL

Unidade 3

- Aula 10 e 11 (28 e 29 Mar) - Marcos

- Eficiência de Circuitos Combinacionais

- Compartilhamento de Operadores (Ex: 7.2.1, 7.2.2, 7.2.3, 7.2.4)

- Compartilhamento de funcionalidades (Ex: L7.1, L7.2, L7.3, L7.4, L7.5)

- Análise da área (Elementos Lógicos) x tempo de propagação.

- Questões relacionadas com o Leiaute do circuito

- Exemplos de circuitos XOR; (Ex:L7.15 - 7.18 )

- Exemplos de Deslocador (shifter) (Ex: )

- Exemplos de Multiplicadores (Ex: )

- Ver pag. 163 a 211 de [1]

- Ver também os slides Unidade 3: Eficiência de Circuitos Combinacionais

- Aula 12 (4 Abr) - Marcos

- Eficiência de Circuitos Combinacionais

- Comparação de circuitos somadores de M entradas de N bits. Comparar a implementação em árvore x cadeia. Experimente utilizando tipos Integer e/ou (un)signed. Utilize como base os circuitos dos Exercícios 7.15 e 7.18 [1], nos quais são mostradas implementações de portas XOR. O objetivo desse tópico é realizar medições de tempo, e mudar o desempenho do projeto seja mudando o código ou usando LogicLock ou restrições de tempo.

- Exercício: Verificar os tempos de propagação do caminho crítico nos somadores implementados usando FPGA da familia Ciclone e Ciclone IV E, Considerando um circuito com 8 entradas de 12 bits.

- Sem usar LogicLock anote os resultados. Observe a disposição dos elementos lógicos no Chip Planner.

- Usando o LogicLock, selecione uma região qualquer do chip para implementar o circuito, e faça a compilação do circuito. Use regiões na Vertical, na Horizontal e Retangular e anote os resultados.

- Anote em um tabela o número de Elementos lógicos (Totais|Normais|Aritméticos), o tempo de propagação do caminho crítico, indicando a origem e destino dele. Desconsidere os dois primeiros e dois últimos tempos indicados no Path Report, pois são referentes a entrada do sinal e saída dos sinais até a região de interesse no FPGA.

- Sem usar LogicLock, insira um arquivo de restrição SDC com a restrição (set_max_delay -from a* -to y* T), onde T é o atraso maximo entre as entradas a* até as saídas y*. Procure obter tempos de atraso menores que os anteriores.

- Experimente aumentar os tempos de atraso usando (set_min_delay -from a* -to y* T).

- Compare seus resultados com o dos colegas que escolheram outras regiões do chip.

Unidade 4

- Aula 13 (11 Abr) - Marcos

- Eficiência de Circuitos Sequenciais

- Tipos de Sincronismo em circuitos (globalmente síncronos, localmente síncronos, assíncronos)

- Circuitos síncronos (Modelo, vantagens e tipos)

- Descrição dos elementos básicos de memória (Latch D, Flip Flop D, Registros)

- Projetos síncronos.

| Modelo em VHDL de projeto síncrono |

|---|

-- Declaração das bibliotecas e pacotes a serem utilizados

library ieee;

use ieee.std_logic_1164.all;

entity nome_entidade is

-- Declaração dos valores GENERIC

generic(

___: Natural := ___;

...

);

-- Declaração das portas de entradas e saída

port(

-- Declaração dos sinais de clock e reset assincrono

clk, reset: in std_logic;

-- Declaração das demais portas de entradas isoladas e barramentos

___: in std_logic;

___: in std_logic_vector(__ downto 0);

...

-- Declaração das portas de saídas isoladas e barramentos

___: out std_logic;

___: out std_logic_vector(__ downto 0);

...

);

end entity;

architecture nome_architetura of nome_entidade is

-- Declaração das entradas e saídas dos registros

signal ___reg: std_logic_vector(___ downto 0);

signal ___next: std_logic_vector(___ downto 0);

-- Declaração dos demais sinais internos

...

begin

-- Descrição da lógica sequencial registro

process(clk,reset)

begin

if (reset='1') then

___reg <= (others=>'0');

...

elsif (clk'event and clk='1') then

___reg <= ___next;

...

end if;

end process;

-- Descrição da lógica combinacional de próximo estado

...

...

-- Descrição da lógica combinacional dos circuitos de saída

...

...

end architecture;

|

- Exemplo de FF D com enable;

- Exemplo de FF T;

- Exemplos de registrador de deslocamento;

- Exemplos de contador modulo m;

- Ver pag. 213 a 239 de [1]

- Eficiência de Circuitos Sequenciais

- Analise Temporal

- Violação do tempo de Setup; Frequencia máxima do clock;

- Temporização relacionadas as saídas.

- Porque não usar VARIABLE em circuitos sequenciais.

- Ver pag. 239 a 255 de [1]

- Ver também os slides Unidade 4: Eficiência de Circuitos Sequenciais

- Ver TimeQuest Clock Analysis

- Aula 14 (12 Abr) - Marcos

- Eficiência de Circuitos Sequenciais

- Praticas deficientes de projeto e soluções:

- Mal uso do RESET assincrono => Use CLEAR síncrono;

--Por exemplo em um contador de 0 a 9 use um CLEAR síncrono

r_next <= (others => '0') when r_reg = 9 else r_reg + 1;

- Mal uso de portas no CLOCK => Use o ENABLE do FF;

--Em um contador

r_next <= r_reg + 1 when ena = '1' else r_reg;

- Mal uso de CLOCK derivados => Use o ENABLE para habilitar o CLOCK durante uma borda de subida;

-- Não use multiplos clocks

elsif (clk'event and clk='1') then

...

elsif (sclk'event and sclk='1') then

...

elsif (mclk'event and mclk='1') then

...

-- Use um único clock com vários enables.

elsif (clk'event and clk='1') then

...

s_next <= (others=>'0') when (s_reg=59 and s_en='1') else

s_reg + 1 when s_en='1' else

s_reg;

...

m_next <= (others=>'0') when (m_reg=59 and m_en='1') else

m_reg + 1 when m_en='1' else

m_reg;

- Contadores

- Contador Gray

0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000 0000 ...

- Contador em Anel

0001 0010 0100 1000 0001 ...

- Contador Binário

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 0000 ...

- Contador Decimal

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 0000 ...

- LFSR (Linear Feedback Shift Register) [1]

0001 1000 0100 0010 1001 1100 0110 1011 0101 1010 1101 1110 1111 0111 0011 0001 ...

- Ver pag. 257 a 274 de [1]

- Ver também os slides Lecture 05: Design of Sequential Circuits: Practice

- Aula 15 (18 Abr) - Marcos

- Eficiência de Circuitos Sequenciais

- Modulação por largura de pulso (PWM)

- Uso de um registrador de saída para evitar os erros devido a glitches.

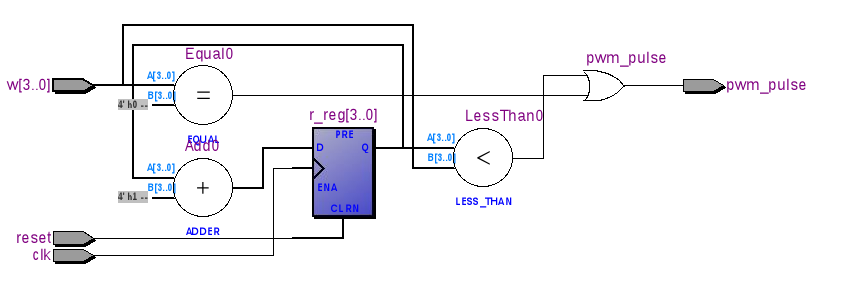

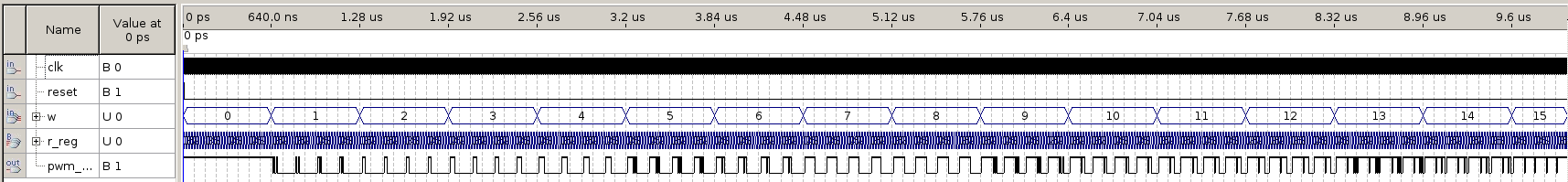

Figura 4.1 - PWM sem buffer de saída - tem gliches na saída.

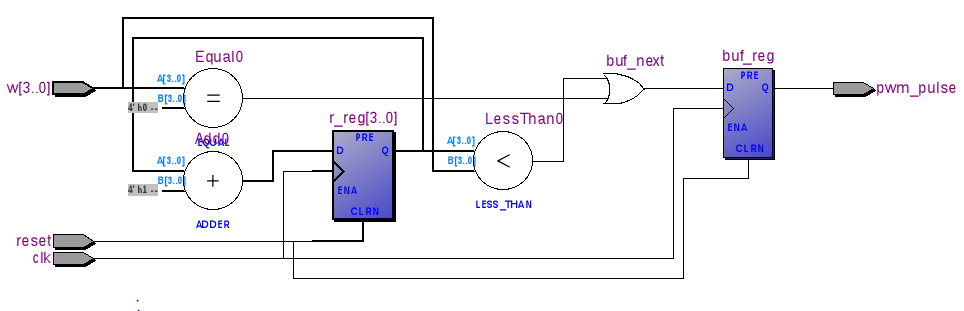

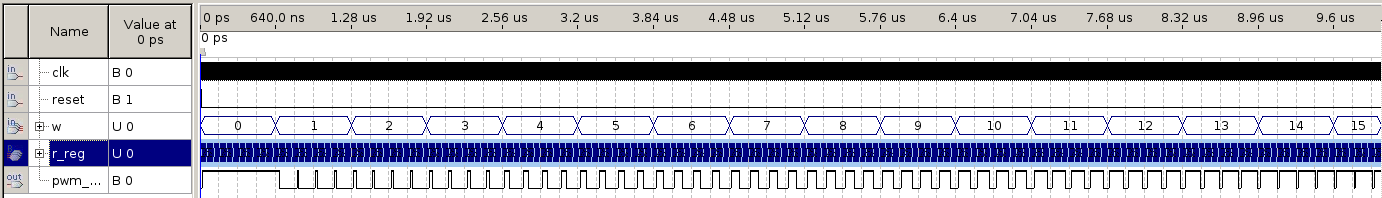

Figura 4.2 - PWM com buffer de saída - não tem gliches na saída.

- Uso de registradores como armazenamento temporário - Vetor de registradores.

- FIFO (First In First Out) baseada em vetor de registradores.

- Circuito de controle de FIFO - sinais full (cheia) e empty (vazia)

- Implementação com contador binário ampliado ou com FFs de estado.

- Controle de FIFO com contadores não binários (Gray, LFSR, contador em anel)

- Ver pag. 275 a 293de [1]

- Ver também os slides Lecture 05: Design of Sequential Circuits: Practice

- Aula 16 (18 Abr) - Marcos

- Aula 17 (25 Abr) - Marcos

- Eficiência de Circuitos Sequenciais

- Uso de Pipeline

- Aula 18 (26 Abr) - Marcos

- Eficiência de Circuitos Sequenciais

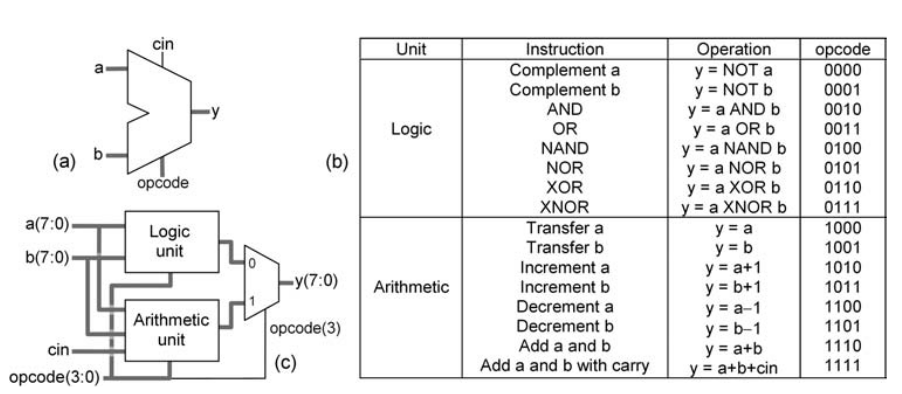

- Exemplo de uso compartilhamento de operadores, funcionalidades e pipeline. Projeto de ALU

- Ver pag. 127 a 129 de [2]

Figura 1 - Unidade de Lógica e Aritmética :: [2]

Figura 1 - Unidade de Lógica e Aritmética :: [2]

- Considerando as funcionalidades da ALU mostrada acima e o código sugerido pelo autor mostrado abaixo:

- 1) Para o circuito original determine o número de elementos lógicos, o atraso máximo e a máxima taxa de operação do sistema (fmax = 1/delay_max).

- 2) Modifique o circuito de modo que o operador de soma e a subtraçao seja compartilhado utilizando um único somador

- 3) Para o circuito modificado determine o número de elementos lógicos, o atraso máximo e a máxima taxa de operação do sistema (fmax = 1/delay_max).

- 4) Utilize a técnica de "pipeline", inserindo registradores do fluxo de processamento para obter uma maior taxa de operação do sistema.

- 5) Para o circuito modificado determine o número de elementos lógicos e máxima taxa de operação do sistema (fmax).

- DICA utilize o componente LPM_ADD_SUB da Altera variando a latencia do circuito.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY alu IS

GENERIC (N: INTEGER := 8); --word bits

PORT (

a, b: IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

cin: IN STD_LOGIC;

opcode: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

y: OUT STD_LOGIC_VECTOR(N-1 DOWNTO 0));

END ENTITY;

ARCHITECTURE alu OF alu IS

SIGNAL a_sig, b_sig: SIGNED(N-1 DOWNTO 0);

SIGNAL y_sig: SIGNED(N-1 DOWNTO 0);

SIGNAL y_unsig: STD_LOGIC_VECTOR(N-1 DOWNTO 0);

SIGNAL small_int: INTEGER RANGE 0 TO 1;

BEGIN

------Logic unit:--------------

WITH opcode(2 DOWNTO 0) SELECT

y_unsig <= NOT a WHEN "000",

NOT b WHEN "001",

a AND b WHEN "010",

a OR b WHEN "011",

a NAND b WHEN "100",

a NOR b WHEN "101",

a XOR b WHEN "110",

a XNOR b WHEN OTHERS;

------Arithmetic unit:---------

a_sig <= SIGNED(a);

b_sig <= SIGNED(b);

small_int <= 1 WHEN cin='1' ELSE 0;

WITH opcode(2 DOWNTO 0) SELECT

y_sig <= a_sig WHEN "000",

b_sig WHEN "001",

a_sig + 1 WHEN "010",

b_sig + 1 WHEN "011",

a_sig - 1 WHEN "100",

b_sig - 1 WHEN "101",

a_sig + b_sig WHEN "110",

a_sig + b_sig + small_int WHEN OTHERS;

------Mux:---------------------

WITH opcode(3) SELECT

y <= y_unsig WHEN '0',

STD_LOGIC_VECTOR(y_sig) WHEN OTHERS;

END ARCHITECTURE;

Unidade 8

- Aula 24 (13 jun)

- Projeto Hierárquico

- Ver pag. 473 a 498 de [1]

- Aula 25 (20 jun)

- Projeto Parametrizado

- Tipos de parâmetros (tamanho e características)

- Especificando parâmetros de tamanho (GENERIC, atributos de ARRAYs, ARRAYs não restringidos)

- Exemplos L14.1 (GENERIC), L14.2 (atributos de ARRAYs), L14.4 e L14.5 (ARRAYs não restringidos)

- Uso de agregados (L14.7)

a = (a'range => '1')

- Especificando parâmetros de características (IF GENERATE com GENERIC, CONFIGURATION)

gen_label: if <boolean_exp> generate

-- expressões concorrentes

end generate;

- A <boolean_exp> deve ser estática, ou seja deve ter um valor TRUE ou FALSE na compilação, não podendo ser dependente de alguma entrada.

- O IF GENERATE não tem o ELSE.

- O GENERIC utilizado deve ser INTEGER.

- Exemplo L14.16 (up_or_down) X L14.17 (up_and_down) X L14.20 (up + down)

- Ver pag. 499 a 543 de [1]

Referências Bibliográficas: