Usuário:Kamila.r

Use no projeto está pagina para as edições enquanto não devem ser visiveis para o público.

Bolsistas:Modernização das aulas de Laboratório de Circuitos Lógicos

Para publicar utilizaremos a página Modernização das aulas de Laboratório de Circuitos Lógicos

Diário do Bolsista

Semana 1-2

- 02mai2013

- Ler a tela de ajuda da wiki. Praticar pequenas edições na wiki nesta Área de rascunho.

- 07mai2013;

- Discussão sobre as etapas do projeto. Planejamento. Esclarecimento de dúvidas.

- Assistir as aulas de CIL29003 (para rever a disciplina sob outro enfoque).

- Agendada um reunião semanal nas terças-feiras 9h40-11h30.

- Definido o local de trabalho.

- Ler PEDRONI, Volnei A. Eletrônica Digital Moderna e VHDL: Princípios Digitais, Eletrônica Digital, Projeto Digital, Microeletrônica e VHDL. 1 ed. [S.l.]:Elsevier, 2010. 648 p. ISBN 978-8535234657. (Cap 18)

- 08maio2013;

- Iniciando os estudos sobre Dispositivos Lógicos Programáveis (PEDRONI, Volnei A.) cáp 18.

- Ler página CIL-EngTel (página).

- 09maio2013;

- Término da leitura do capítulo referente a Dispositivos Lógicos Programáveis.

- Início da pesquisa na internet sobre FPGAs e CPLDs (estrutura e funcionamento).

- Aula de CIL, no laboratório (Registrador de Deslocamento - BDF e QSIM).

- Procurar dimensionar as dificuldades e tempos envolvidos neste tipo de aula. --Marcos Moecke 10h51min de 17 de maio de 2013 (BRT)

- 10maio2013;

- Início da pesquisa sobre as melhores faculdades de tecnologia do mundo (com foco em eletrônica), projetos e afins.

- Vídeos sobre programação, teste e aplicação produtos ALTERA (YouTube).

Semana 3

- 13maio2013;

- Leitura de tópicos importantes do capítulo 13 da seguinte bibliografia: TOCCI, Ronald J.; WIDMER, Neal S.; MOSS, Gregory L. Sistemas digitais: Princípios e Aplicações. 10 ed. [S.l.]:Pearson Prentic Hall, 2007.

- Obs.: Resumo no final do capítulo é claro e objetivo, para futuras dúvidas sobre a arquitetura dos DLPs, consultá-lo.

- 14maio2013;

- Ver as opções existentes no projeto FPGA para todos, modulos periféricos

- Ver o funcionamento de um display de sete segmentos. (ver Pedroni p.235 a diferença entre Catodo comum e Anodo comum).

- Contactar o aluno Ernani da 3ª fase da engtelecom (também com o aluno Gustavo/Profa Deise). Quais módulos estão disponíveis.

- 15maio2013;

- Aula de CIL.

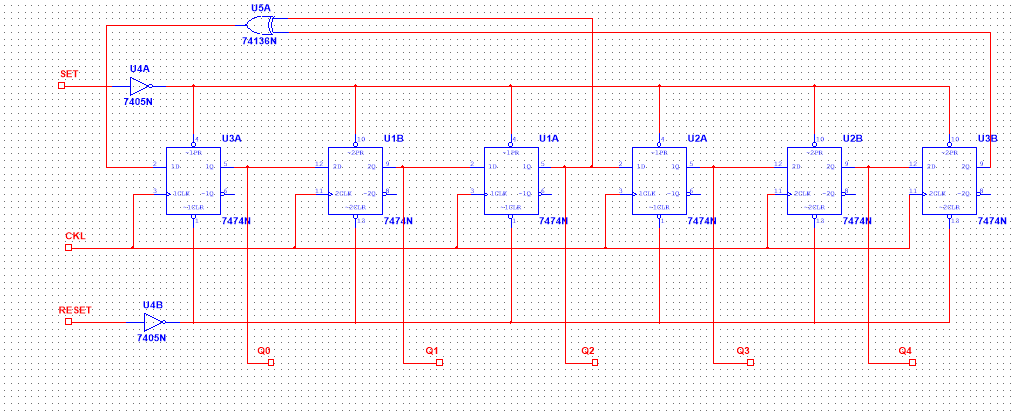

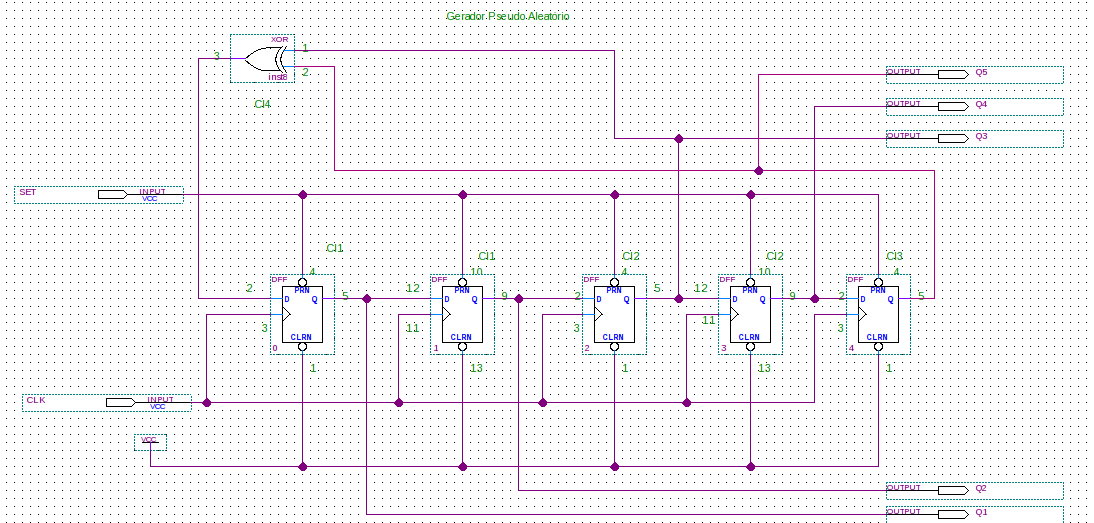

- Exercício de aula: fazer um gerador de sequência pseudoaleatória com 5 FF.

- 16maio2013;

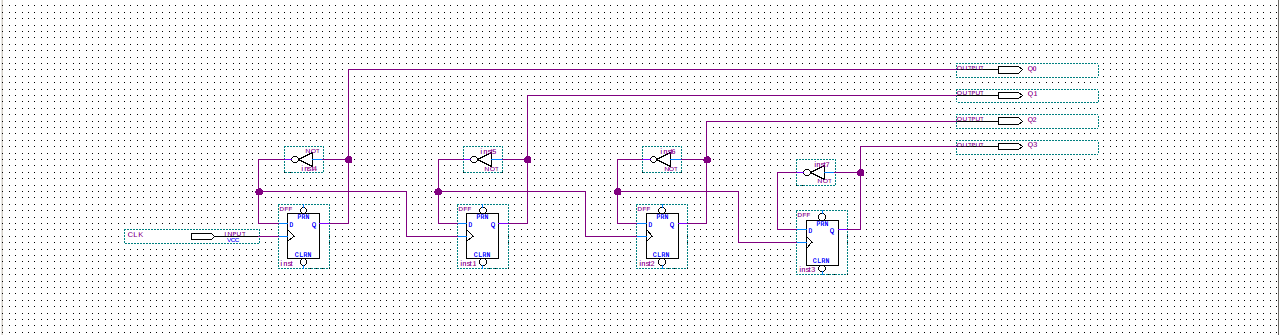

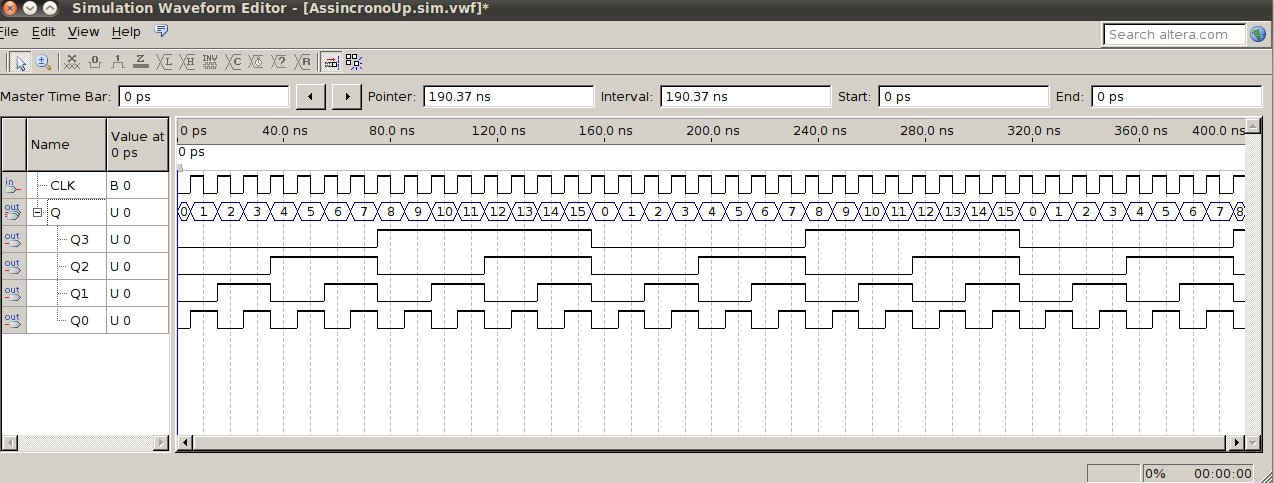

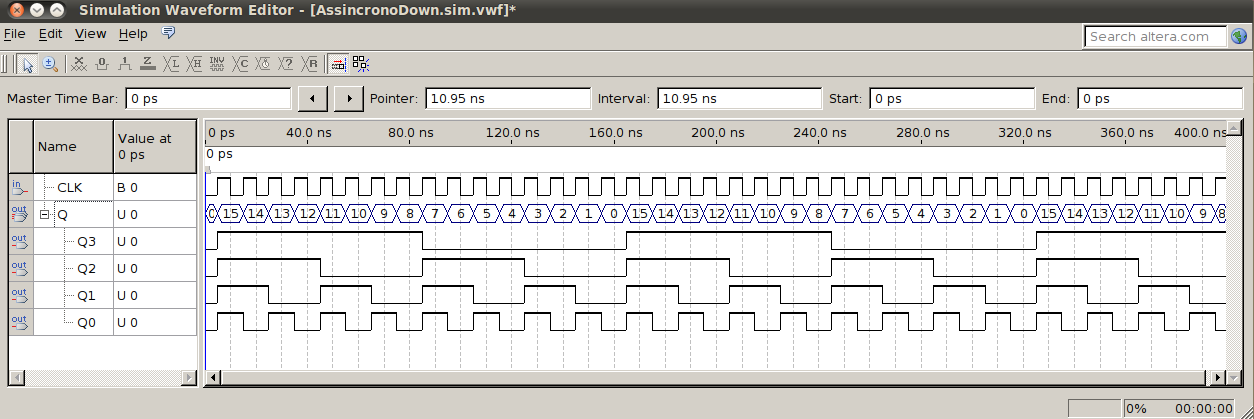

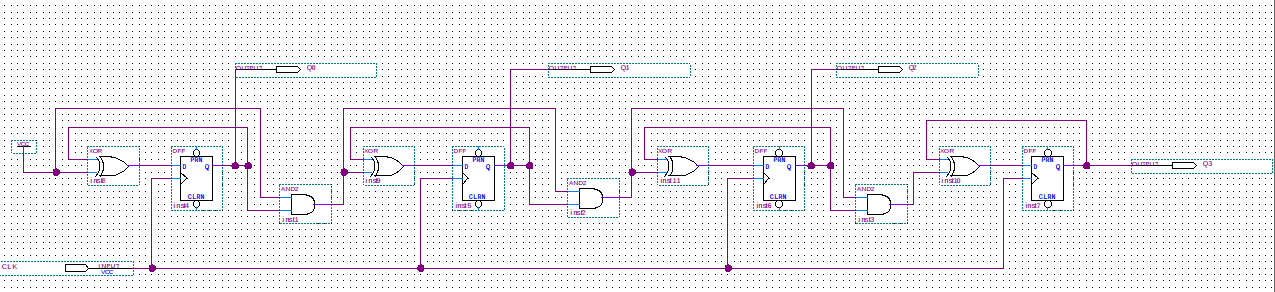

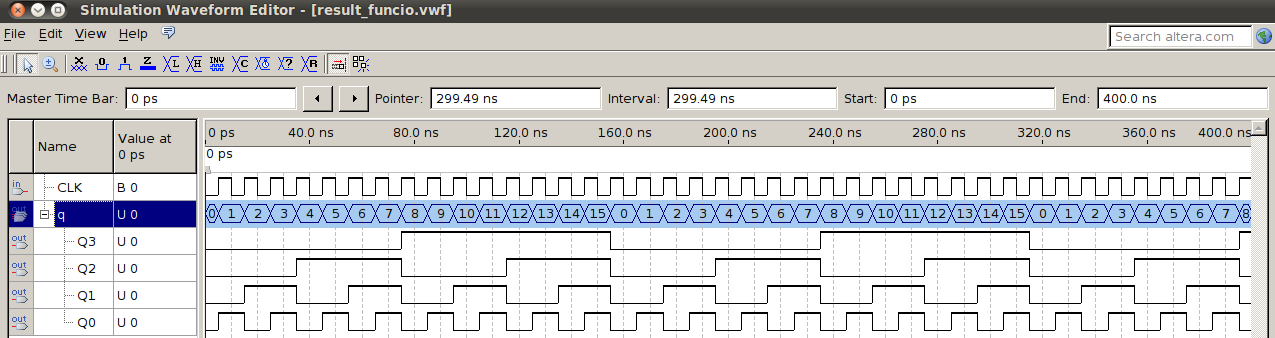

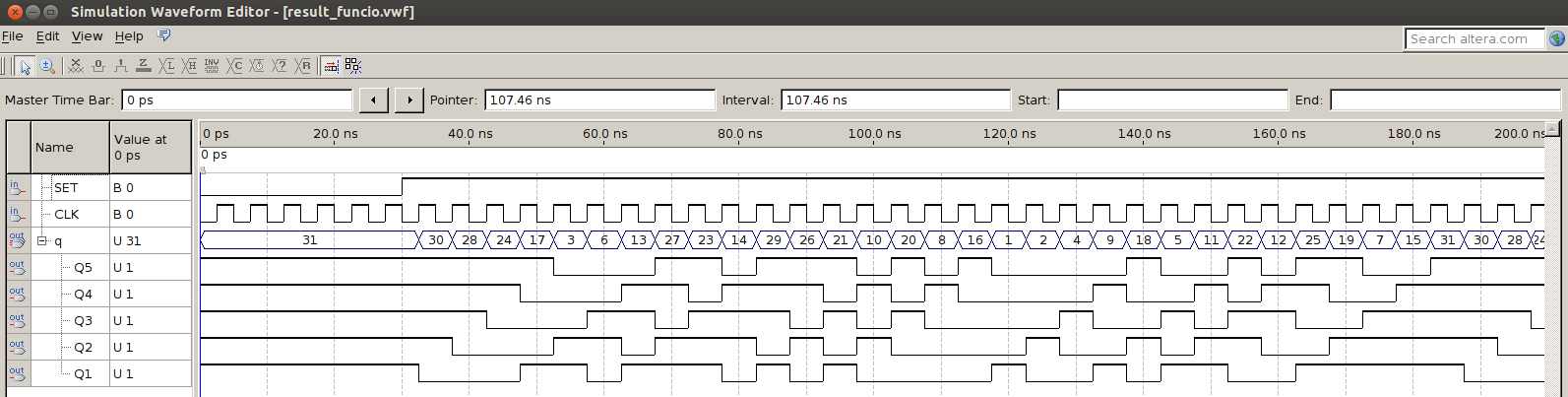

- Implementar o contador Síncrono (0-15), Assíncrono crescente (0-15) e decrescente(15-0), Gerador de sequencia pseudoaleatória (5 bits). Simular no QSIM, funcional e temporal. Perceber as diferenças.

- Verificar como o simulador permite agrupar bits, com diferentes interpretações (radix), usar binário e unsigned decimal.

- Capturar a tela dos sinais de entrada e saída e colar abaixo de cada circuito.

- Primeiro teste: Gerador de sequência pseudo aleatória

- Registrar o tempo que demora para fazer a montagem. Testes funcionais e temporais.

- Note que neste caso (Gerador de sequencia pseudoaleatória) temos a montagem de um projeto, no qual o aluno precisa decidir quais devem ser as conexões, ligações e componentes a serem usados. O tempo de projeto e implementação será maior que no caso de uma simples implementação (Registrador de Deslocamento - BDF e QSIM), no qual todas as ligações já estão previamente definidas. Tente dimensionar as dificuldades e tempo nos dois casos. 1) Implementação; 2) Projeto e implementação. --Marcos Moecke 10h51min de 17 de maio de 2013 (BRT)

Semana 4

- 20maio2013;

- A implementação do exercício feito em laboratório RegDeslocamento foi simples de ser feita, com exceção do erro que apresentou o Qsim

- Tempo estipulado: 10 minutos.

- Já no Gerador de sequência pseudoaleatória, foi adicionada na última porta XOR uma saída Y(houve uma tentativa de ligação das 4 portas q0, q1, q2, e q3 numa única saída, mas não foi identificada a porta que deveria ser usada), com isso foi retirado a ligação da saída XOR do D.

- Tempo estipulado: 30 minutos para a tentativa de projeto e implementação. (Tempo de estimativa deverá ser maior por não ter sido testado no Qsim por conta do seguinte erro "Bad opinion readonly: must be group, owner, or permissions").

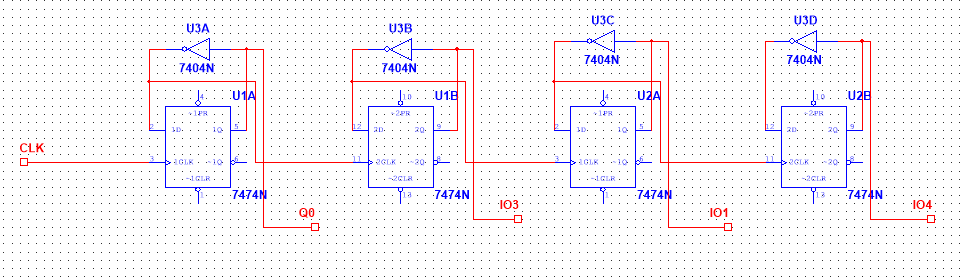

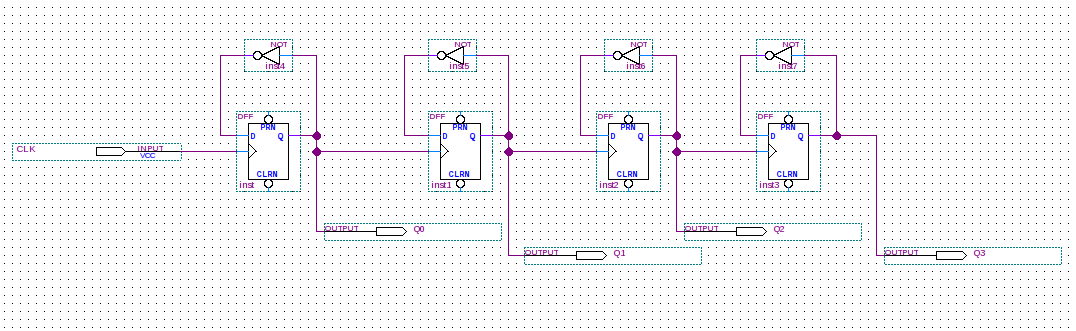

- Projeto e implementação do contador assíncrono crescente

Obs.:O clock é ligado a saída (Q'), apresentei essa solução já que não encontrei uma porta(dff, etc) que houvesse duas saídas Q e Q'

- 22maio2013;

- Aula de CIL.

- Contador Assíncrono Decrescente:

- 23maio2013;

- Seguir o tutorial inicial de CIL29003 Uso do software Quartus e QSIM para ensino de Circuitos Lógicos

- Contador Síncrono precisa de duas entradas para a primeira porta AND para compilar. Aguardo orientações.

- Aula de CIL.

- 24maio2013;

- Teste dos contadores e registradores no Qsim.

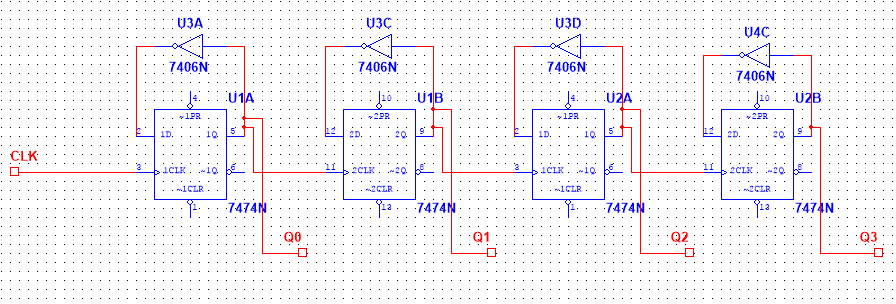

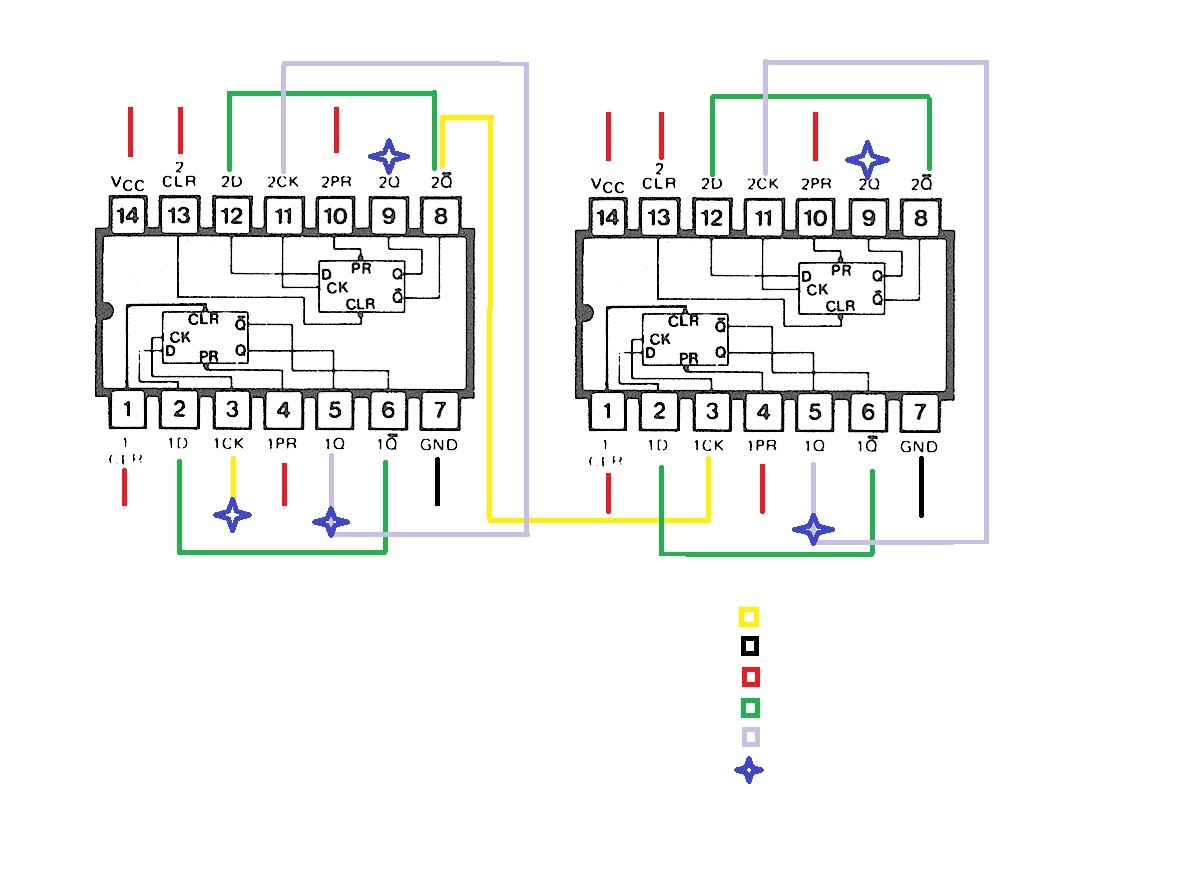

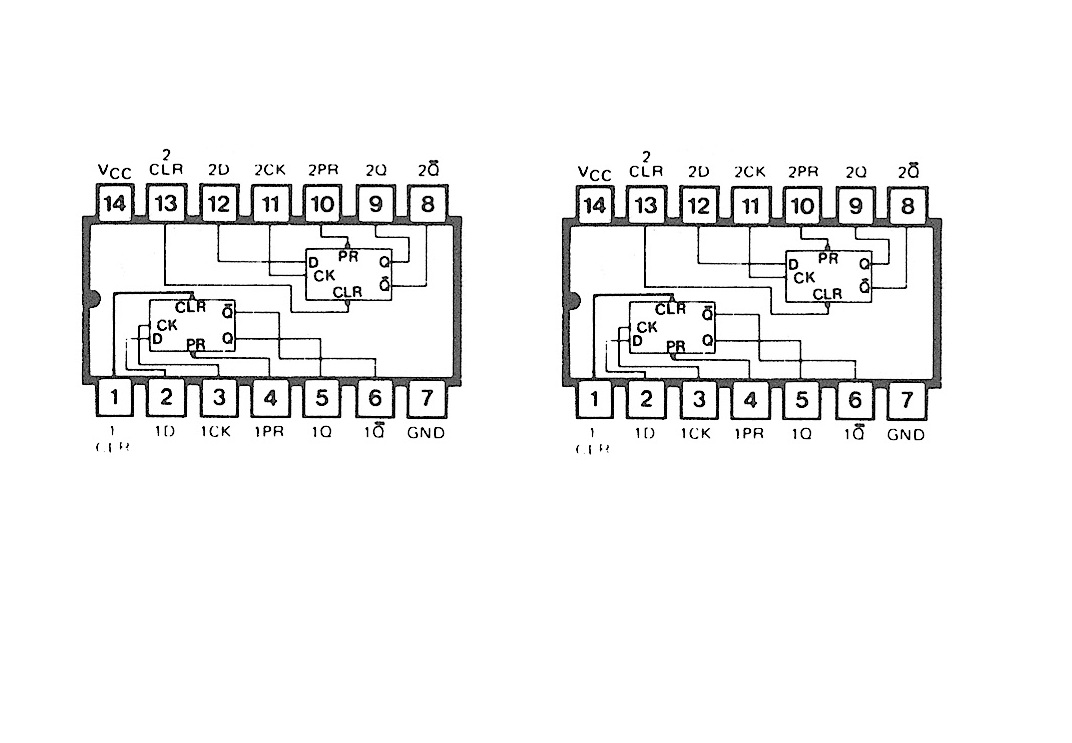

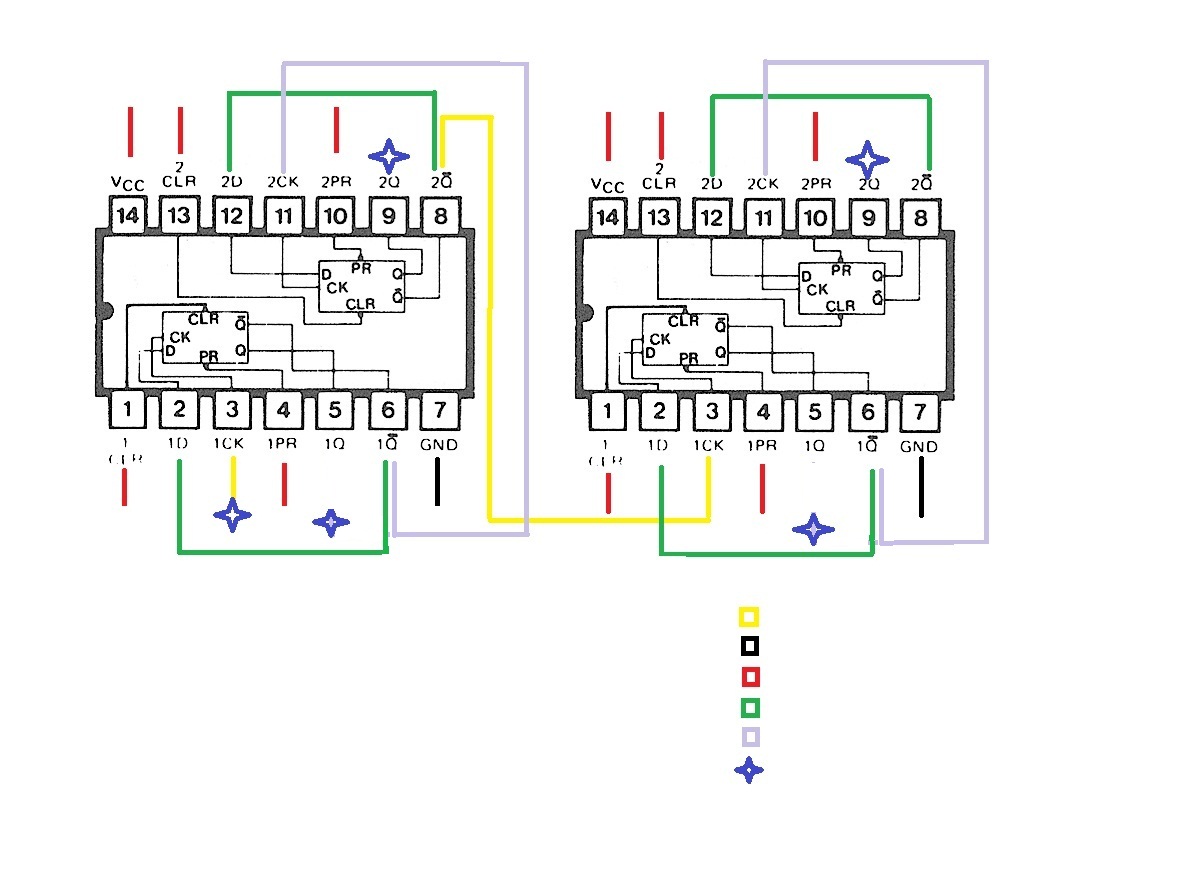

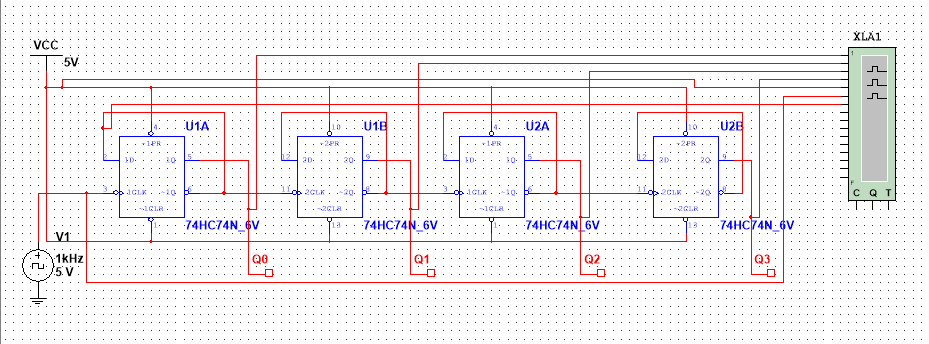

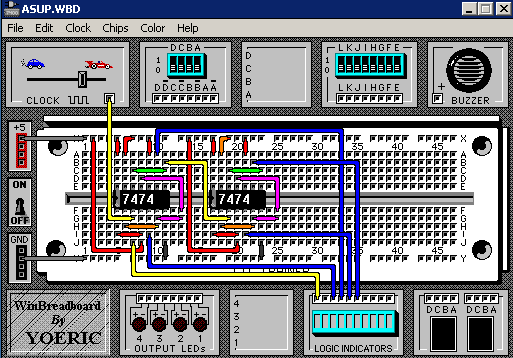

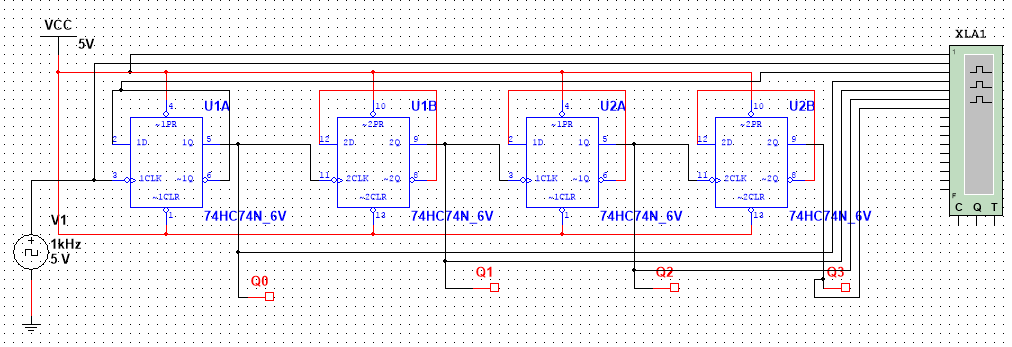

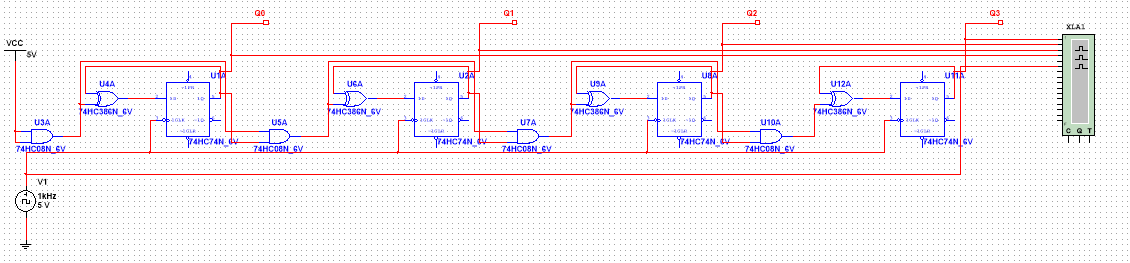

- Implementação do contador assíncrono crescente com CIs (7474), no QuartusII

- Obs.: Na simulação do Qsim, as saídas Q2 e Q4 saem zeradas.

Semana 5

- 27maio2013;

- Terminada a implementação de todos os projetos no QuartusII, juntamente com os testes de simulação no QSIM, com exceção do contador síncrono, ainda não finalizado por erros apresentados na saídas Q2 e Q4 no Qsim.

- Obs.: Para quem não conhece o QuartusII seguir o tutorial é fundamental para a compreensão, sendo ele claro e objetivo, assim ficando muito simples o entendimento sobre o funcionamento e os passos a serem seguidos para a implementação de um projeto.

- 28maio2013;

- Finalização do contador síncrono, com as saídas já corrigidas.

- Planejamento.

- 29maio2013;

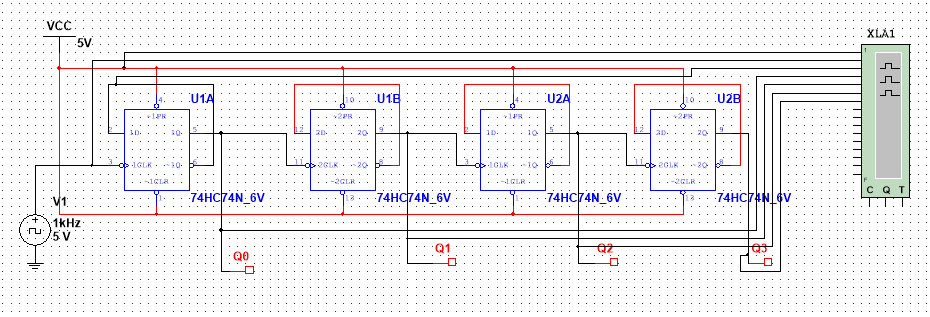

- Implementação esquemática no MultiSim dos contadores e do gerador de função.

- Assíncrono Decrescente

- Gerador de sequencia pseudoaleatória

- Erro com a máquina virtual(não foi instalada no usuário "Kamila")

- Obs.:As implementações foram salvas em BrOffice. Todas estão na máquina MATLAB.

Semana 6

- 03junho2013;

- Instalação do Windows XP na máquina virtual do usuário "Kamila".

- Erro na implementação do contador síncrono

- Obs.: Não é possível conectar um fio a outro.

- 04junho2013;

- Continuação da implementação dos contadores no Multisim.

- Aula de CIL.

- 05junho2013;

- Problemas ao salvar os projetos no OFFICE, contadores tiveram que ser refeito algumas vezes por perda.

- Começo da implementação do esquemático com as formas de ondas.

- 06junho2013;

- Continuação da implementação.

- Aula de CIL.

- 07junho2013;

- Erro com as formas de ondas apresentadas na simulação

- Contador síncrono

- Contador assíncrono crescente

- Contador assíncrono decrescente

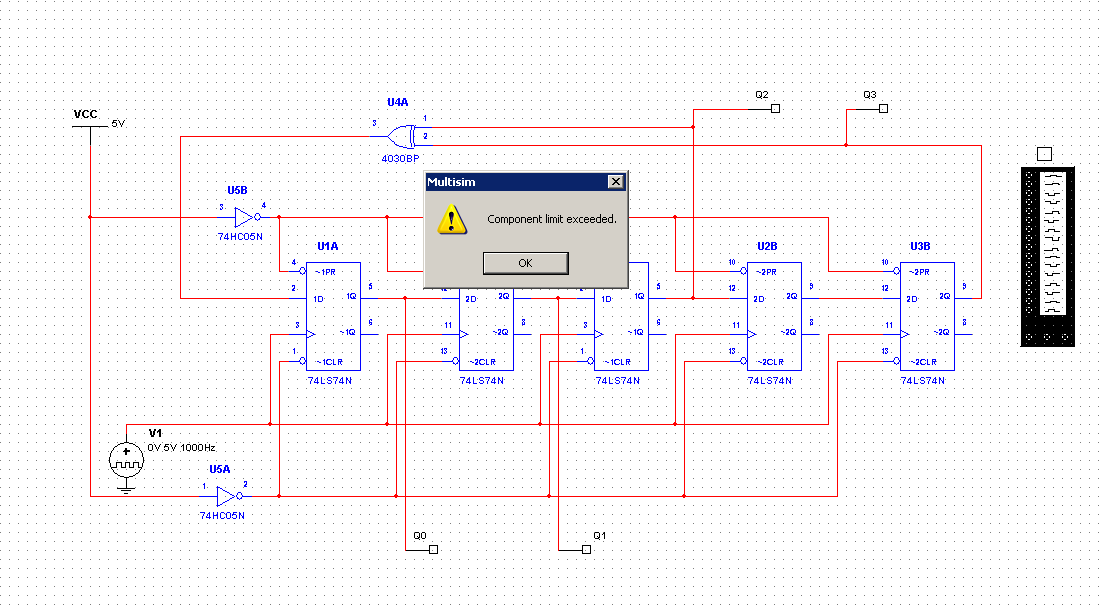

- O gerador de função apresentou um erro de "limitação de componentes":

Semana 7

- 12junho2013;

- Erro ao abrir MultiSim, versão estudante

- 13junho2013;

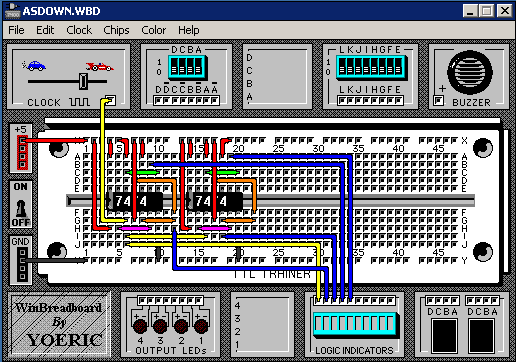

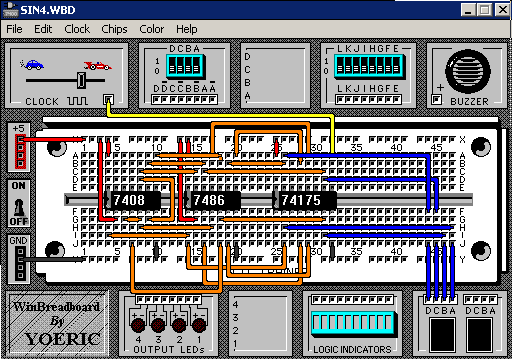

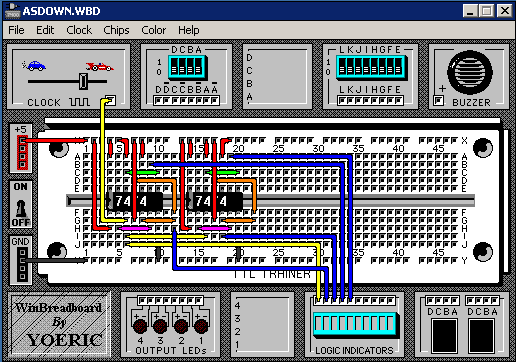

- Implementação do esquemático dos contadores no protoboard virtual. Assíncrono decrescente e gerador de sequência pseudo-aleatória.

- Aula de CIL. Vídeo com a turma da engenharia (MIT).

- 14junho2013;

- Reimplementação dos contadores no MultiSim versão estudante.

Semana 8

- 17junho2013;

- Implementação:

- Contadores assíncrono decrescente em TTL e Cmos.

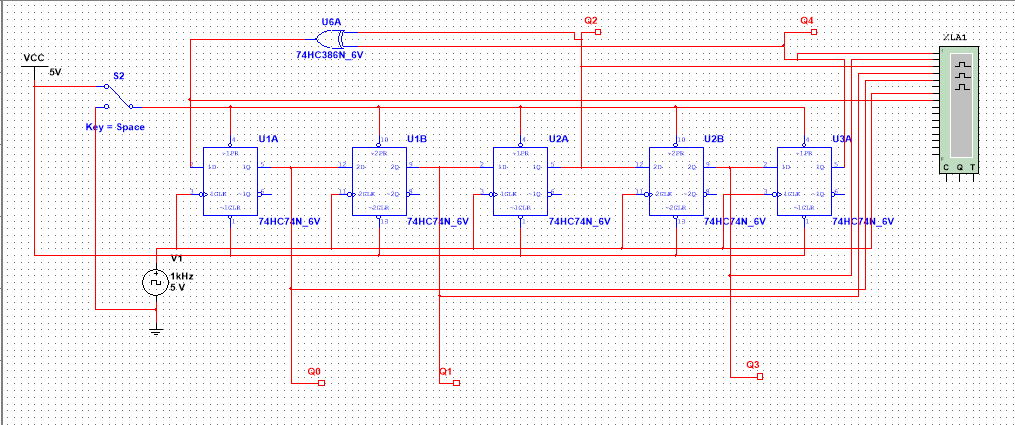

- Gerador de sequência pseudoaleatória em TTL.

- Contador assíncrono crescente em TTL.

- 18junho2013;

- Aula de CIL

- Finalização dos contadores descritos no dia anterior.

- 19junho2013;

- Contador assíncrono decrescente em TTL:

- Contador assíncrono decrescente em Cmos:

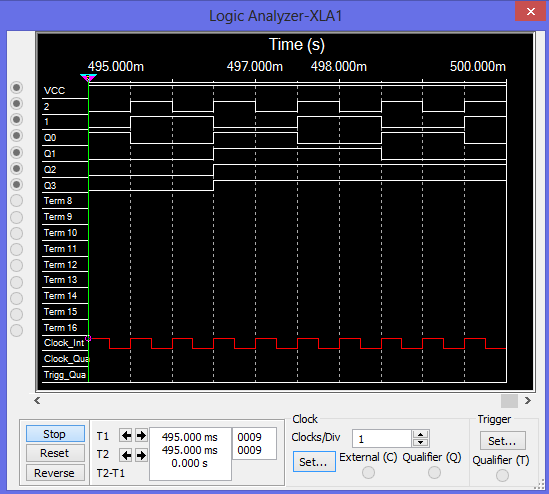

- Análise lógica do contador assíncrono decrescente:

- Contador assíncrono decrescente no protoboard virtual:

- Obs.:Não estou conseguindo analisar, pois está apresentando um erro que ainda não encontrei. Esse ficou uma gracinha hein?!

- Gerador de sequência pseudoaleatória em TTL:

- Contador assíncrono crescente em TTL:

Semana 9

- 24junho2013;

- Término das implementações na nova versão do MultiSim, faltantando apenas o contador síncrono.

- 25junho2013;

- Aula de CIL.

- Reunião.

- 26junho2013;

- Término das implementações dos contadores síncronos que estavam falando no MultiSim.

- Implementação do contador assíncrono crescente no protoboard virtual funcionando corretamente.

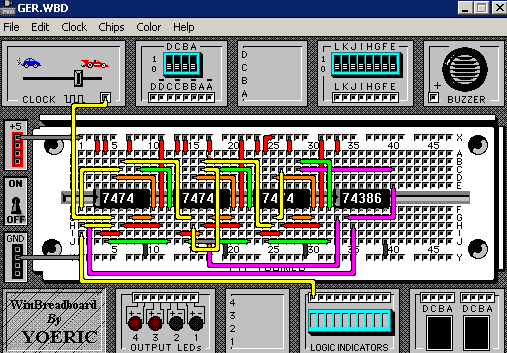

- 27junho2013;

- Protoboard virtual do contador assíncrono crescente.

- Começo da implementação do contador síncrono no protoboard virtual.

- Aula de CIL.

Semana 10

- 01jul2013;

- Término da implementação do gerador de sequência pseudoaleatória, que precisava da chave para funcionar corretamente.

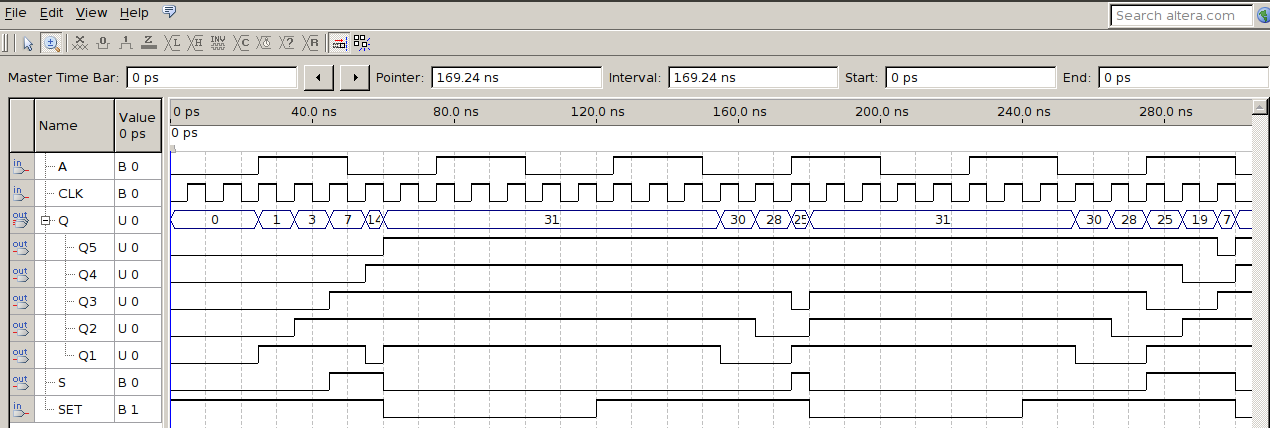

- Formas de onda no simulador

- Implementação do contador assíncrono crescente no protoboard real

- 02jul2013;

- Aula de CIL.

- Reunião

- 03jul2013;

- Implementação do gerador de sequência pseudo aleatória no protoboard virtual.

- 05jul2013;

- Organização das imagens na página da wiki, criando um sublink com todas os teste já realizados, inclindo links externos para o youtube com o funcionamento dos contadores até então prontos.

- Continuação das implementações no protoboard virtual, com os novos CIs escolhidos.

Semana 11

- 09julho2013;

- Aula CIL

- Concluindo edições dos contadores na wiki.

- Dúvidas no clock do gerador de sequência pseudo aleatória: Os pinos 3 e 11 são ligados em um único clock, onde deve ocorrer essa conexão?

- 10julho2013;

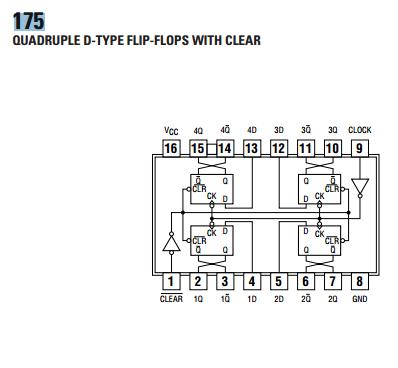

- Início da implementação do contador síncrono no protoboard virtual, utilizando CI 74175.

- Consultas em Guia de Bolso

- 11julho2013;

- Para a finalização do gerador de função é necessário organizar o clock.

- Dúvidas sobre o CI utilizado no contador síncrono, que possui pinagem muito diferente do CI 7474 implementado no Quartus e Qsim.

- 12julho2013

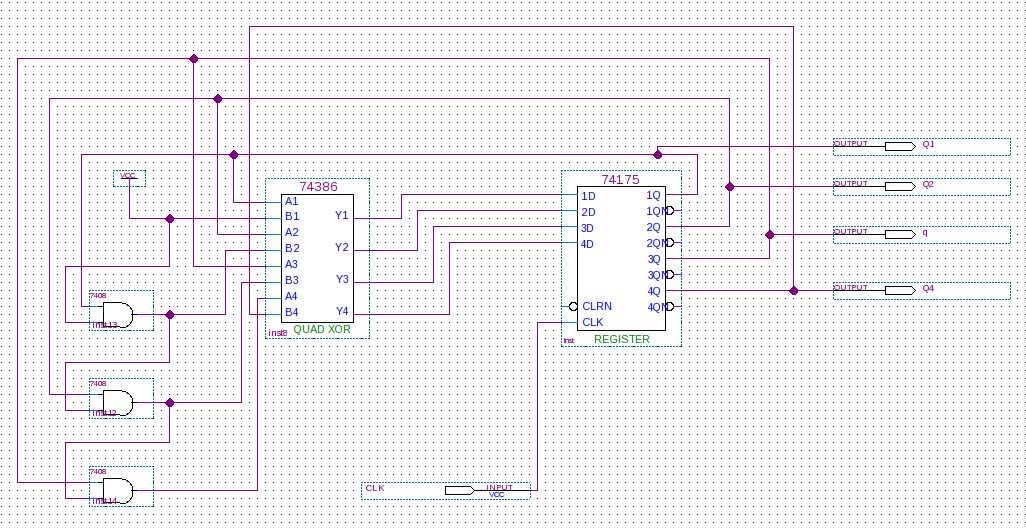

- Implementação do contador síncrono novamente no Quartus, mas agora com o CI 74175.

- Quartus:

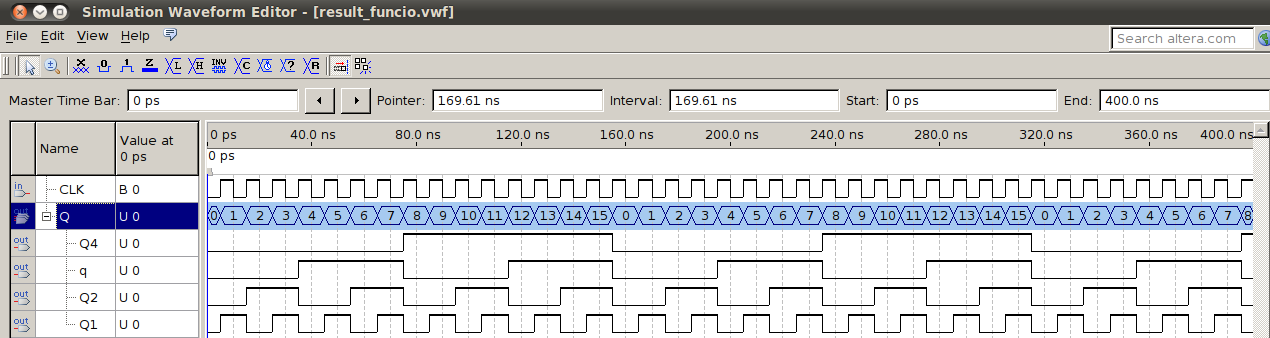

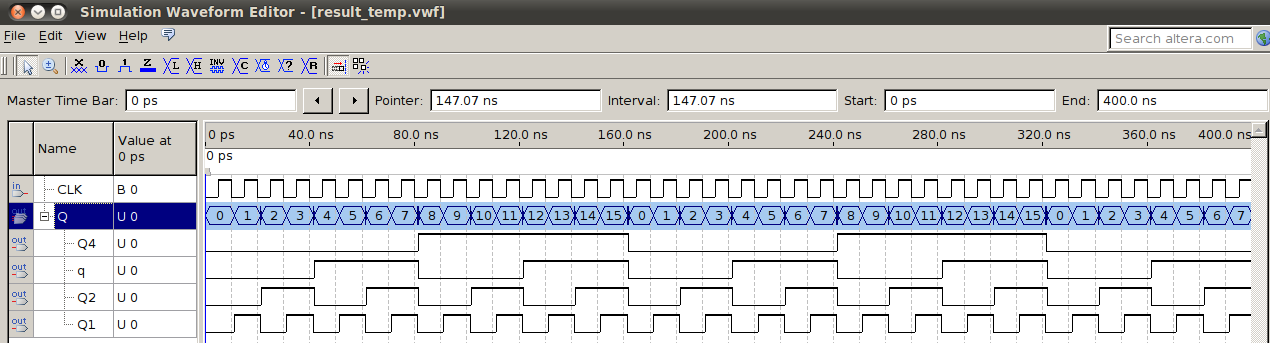

- Qsim funcional:

- Qsim temporal:

Semana 12

- 15julho2013;

- Continuação das implementações do contador síncrono e gerador de sequência no protoboard virtual.

- Contador síncrono implementado com o CI 74175, com a seguinte pinagem:

- Correção da versão do contador síncrono no Quartus CI 74175, tirando a primeira entrada e colocando apenas um VCC. Testes no Qsim refeitos. Correção postada nas imagens do dia 12Julho.

- Correção da versão do contador síncrono no Quartus do 7474, imagens já postadas.

- Obs.: Versão do MultiSim Estudante expirou.

- 16Julho2013;

- Aula CIL.

- Reunião.

- 17Julho2013;

- Com a pinagem feita nos CIs a finalização do contador síncrono foi facilitada no protoboard virtual. Já postado no link dos contadores.

- Concluindo o gerador de sequência com a pinagem.

- 18Julho2013;

- Conferido a pinagem com a montagem do gerador de sequência pseudo-aleatória. Montagem correta, porém não funciona como o esperado.

- Correção de algumas modificações do gerador de sequência pseudo-aleatória no Quartus e simulação no Qsim. Já postadas no link dos contadores.

- Aula de CIL.

- 19Julho2013;

- Implementação do contador síncrono no protoboard real.

- Não encontrado no almoxarifado de Tele o CI 74386. Impossibilitando a conclusão da implementação.

- Tempo envolvido na escolha dos componentes:

- Componentes necessários: Fios, CI 74LS175, CI 74386(não disponível), CI 74LS08, alicates e plataforma com protoboard.

Semana 13

- 22julho2013;

- Reimplementando o contador síncrono no protoboard virtual com o CI 7486, pois não há disponibilidade do CI 74386.

- Implementação no protoboard real finalizada. Tempo estimado: 1 hora.

- 23julho2013;

- Aula de CIL.

- Publicado na wiki o vídeo do funcionamento do contador síncrono.

- Não foi possível carregar a nova versão do protoboard virtual com o CI 7486, apresentado um erro na hora do envio da imagem.

- 25julho2013;

- Tentando implementar o gerador no protoboard real

- Wiki permanece com erro no download de imagens

- 26julho2013;

- Erro da wiki resolvido

- Contador síncrono no protoboard virtual utilizando o CI disponível no Almoxarifado (7486)

- Refazendo a implementação do gerador de sequência. O que já está com as ligações feitas e conferidas não funcionam corretamente. Obs.: Já foram trocados os CIs para testar se eles estavam queimados e nada mudou.

Semana 14

- 29julho2013;

- Apesar de conferido, refeito, e testado diversas vezes, o gerador continua com um erro e não funciona corretamente.

- 30julho2013;

- Refazendo o gerador de sequência no Quartus, agora com o D numa entrada qualquer e com o CI 7486 apenas ligado em uma saída.

- Teste

- Refazer o gerador de sequência no protoboard virtual de acordo com a nova versão do Quartus.

- Obs.: Clock e entrada ligados a uma chave.

Semana 15

- 19Agosto2013;

- Refazendo alguns testes com o gerador de sequência pseudoaleatória. É necessário que o teste no Qsim apresente um loop, após gerar uma sequência.

- Iniciando a elaboração do questionário que será apresentado aos professores da área de Eletrônica do Campus, além de alunos que já tiveram a matéria. Ambos terão questionários direcionados. O objetivo deste, é analisar as necessidades básicas e a melhor maneira que professores conduzem as matérias relacionadas com Eletrônica. E também a melhor maneira que os alunos absorvem os métodos apresentados.

- 20Agosto2013;

- Definido como vai ser conduzido os teste feito com alunos de Telecom.

- Haverá a preparação de um roteiro com um dos contadores já feitos e a partir deles um questionário avaliando as dificuldades ou facilidades encontradas em cada método de avaliação.

- Passo 1: Alunos terão em mãos o esquemático(com pinagem) do contador e tentarão implementá-lo no protoboard real

- Passo 2: Será montado primeiramente no MultiSim(obs.:versão não disponível no momento) e depois a implementação no protoboard virtual

- Passo 3: Projeto será montado no Quartus e depois montado na placa.

- Apresentar esse questionário para professores de Eletrônica do Campus, mostrar resultados e pedir a avaliação deles, juntamente com perguntas sobre a experiência dos mesmos com a matéria, a maneira com que eles conduzem e acham que o aluno absorve melhor a matéria.

- Registrar o tempo envolvido em cada um dos experimentos.

- Questionário e entrevista com professores atuais e ex-professores das disciplinas de Circuitos Lógicos e Eletrônica Digital, verificando as atuais deficiências encontradas nas aulas de laboratório;

- Quando foi professor?

- Bibliografia utilizada?

- Usava laboratório? Como eram as aulas?

- Deficiências que vê no ensino prático?

- Sugestões de melhoria?

- 21Agosto2013;

- Conferir os projetos e selecionar um deles para a iniciação das etapas.

- Problema com o software MultiSim versão Estudante. (É necessário para conferir os contadores, além de que ele faz parte do roteiro dos testes)

- Refazer os esquemáticos e fixar bem as etapas. (Obs.:fazer roteiro próprio de etapas dos Software para eventual consulta)

- Conferir materiais necessários(alicates, fios, placas, CIs, etc)

- Depois de refeito os esquemáticos, fazer a PINAGEM do contador para implementação no protoboard real(1° passo)

- 22Agosto2013;

- Contador assíncrono crescente selecionado.

- O esquemático será feito com um CI comercial SN74LS74AN[1]

- Fazer pinagem para o Passo 1 e imprimir

- O questionário será divido em partes, cada sessão de teste terá perguntas referente a eles.

- Estipular tempo que será necessário para os testes e agendar com os alunos que participarão

- Questionário alunos;

- Qual o nível de dificuldade desta etapa?

- Qual o nível de dificuldade na montagem do contador?

- Qual o nível de entendimento sobre o contador?

- 23Agosto2013;

- PINAGEM;

- Versão sem pinagem;

Semana 16

- 26Agosto2013;

- Para explicar as etapas do contador assíncrono crescente, analisar e resumir o livro do Pedroni referente a esse assunto.

- Refazendo o esquemático no Quartus para relembrar os tópicos e fazendo um Roteiro do mesmo.

- 27Agosto2013;

- Faltando fazer o roteiro do MultiSim que não está disponível no momento.

- Roteiro Quartus finalizado.

- Escolhidos alunos que participarão dos teste:

- Natália Vieira Miranda - 8 fase Técnico-Integrado Telecom

- Vinicuis Kachniacz - 4 fase Tecnólogo Telecom

- Leonan Saraiva - 4 fase Eng Telecom

- Matuzalém Muller - 3 fase Eng Telecom

- Mathias Silva - 3 fase Eng Telecom

- 28Agosto2013;

- Refeito o esquemático no protoboard real, e encontrado um erro na pinagem.

- Corrigir a Pinagem nos CI's.

- Definido que a versão utilizada nos teste será o MultiSim Demo. Detalhe: A versão não permite ser salva, então é necessário que ele seja "colado especial" num documento LibreOffice.

- Revisar o projeto.

- Versão do Quartus será feita com o CI comercial, mas para a inciação da implementação será necessária a versão em dff imprimida.

- 29Agosto2013;

- Pinagem corrigida:

Semana 17

- 02Setembro2013;

- Editando imagens para a utilização nos teste (incluindo resumo do livro Pedroni que menciona o contador, e imagens do Quartus com a versão do contador em DFF).

- Refazer o contador no Quartus com CI comercial.

- Obs.: No MultiSim é necessário que não haja confusão, nem mistura de componentes CMOS e TTL. No contador será utilizado o CI 74LS74N.

- Obs.: Para eventuais dúvidas Uso do software Quartus e QSIM para ensino de Circuitos Lógicos

- 03Setembro2013;

- Criando formulário no Gmail.

- Definida a maneira como o questionário deve ser feito.

- Faltando tutorial sobre o MultiSim versão demo, refazer e selecionar as partes mais importantes e fundamentais.

- 05Setembro2013;

- Fazer a pinagem no Quartus do teste 3.

- Refazer o projeto no MultiSim versão demo, mas colocando as saídas no display. Ver se é possível fazer a análise de ondas como no outro modelo.

Semana 18

- 09Setembro2013;

- Refazer a pinagem da primeira etapa do teste(pinagem muito facilitada).

- Revisado o projeto no MultiSim.

- 10Setembro2013;

- Refeito projeto no MultiSim, mas houve um erro de repetição no display >>> Problema resolvido com uma frequência de 10Hz, num ciclo de 20.

- Prévia do formulário:

- Formulário Alunos

- 11Setembro2013;

- Obs.: Wiki não está carregando novas imagens.

- Formulário dos professores serão mais teóricos comparado com o dos alunos

- Formulário Professores

- 12Setembro2013;

- Depois de refeito o esquemático do contador no MultiSim, remontá-lo no protoboard virtual

- Não há problema com a quantidade de componentes com essa versão do MultiSim. Mesmo com a implementação dele com display.

- Fazer roteiro do MultiSim (DEMO: fazer comparações e ver se há diferença entre o funcionamento com o MultiSim versão Estudante, onde o projeto foi incialmente criado e protoboard virtual)

- 13Setembro2013;

- PLANEJAMENTO: Resumo das etapas já realizadas e as que ainda faltam ser feitas

- Etapa 1: Esquemático com pinagem refeito e corrigido (Faltando apenas imprimir nova versão)

- Etapa 2: Será utilizada a versão do MultiSim demo (funcionamento com o display e a quantidade de componentes também já foi testada)

- Protoboard virtual: também será utilizado na versão demo (testado)

- Obs.: Não é necessário fazer pinagem para montar no protoboard virtual nesse esquemático pois ele já é automático no MultiSim.

- Falta imprimir o esquemático do MultiSim

- Etapa 3: Projeto já foi refeito no Quartus, com tutorial para eventuais dúvidas no segmento da montagem do circuito. Além disso, já foi testado também no Qsim, sendo refeita as etapas de criação das entradas, com resultados corretos.

- As imagens do projeto já foram imprimidas, sendo elas: projeto com CI comercial, projeto com a informação contida dentro dele e as ligações feitas e também o projeto feito com DFF (esse será utilizado como base para o início da implementação)

- Faltando apenas a preparação para a implementação do projeto na placa

- Questionários:

- O módulo de como os questionários serão feitos já foi analisado. Já foi criado um arquivo com contendo algumas perguntas. Porém, faltam discussões mais aprofundadas sobre o teor das perguntas que serão questionadas aos alunos e profs, com o intuito de não perder o enfoque da pesquisa.

Semana 19

- 23Setembro2013;

- Fazendo estudo teórico sobre os contadores para a inicialização das explicações nos testes.

- Pedroni e Internet

- Principais características dos contadores assíncronos:

- (1) Os FF não possuem as entradas clock em comum;

- (2) São arranjados de forma que a entrada clock do flip-flop de ordem n seja a saída do flip-flop de ordem n-1;

- (3) Possuem saída binária sequencial; e

- (4) O bit mais significativo da contagem (MSB) está sempre no último flip-flop, considerando como primeiro flip-flop o que recebe os pulsos de clock.

Implementações dos contadores

Contador Assíncrono Crescente

- Quartus:

- QSim Funcional:

- MultiSim:

- Protoboard virtual:

- Funcionamento no protoboard real:

Contador Assíncrono Decrescente

- Quartus:

- QSim funcional:

- MultiSim:

- Protoboard virtual:

- Funcionamento no protoboard real:

Contador assíncrono decrescente

Contador Síncrono

Aqui também precisa corrigir --Marcos Moecke 10h26min de 15 de julho de 2013 (BRT)

- Quartus:

- QSim funcional:

- MultiSim:

- Protoboard virtual:

- Funcionamento no protoboard real:

Gerador de Sequência Pseudoaleatória

- Quartus:

- QSim funcional:

- MultiSim:

- Protoboard virtual:

- Funcionamento no protoboard real:

XXXX