Mudanças entre as edições de "Uso do ambiente EDA - QUARTUS Prime para programação em VHDL"

Ir para navegação

Ir para pesquisar

| Linha 1: | Linha 1: | ||

| − | + | ==PASSO 0== | |

[[Acesso ao IFSC-CLOUD (NUVEM) | Acesse a nuvem do IFSC]] usando um terminal via ssh: | [[Acesso ao IFSC-CLOUD (NUVEM) | Acesse a nuvem do IFSC]] usando um terminal via ssh: | ||

USER=LOGIN_SIGAA | USER=LOGIN_SIGAA | ||

| Linha 6: | Linha 6: | ||

LOGIN_SIGAA@quartus.sj.ifsc.edu.br's password: | LOGIN_SIGAA@quartus.sj.ifsc.edu.br's password: | ||

| − | + | ==PASSO 1== | |

Abra o Quartus Prime digitando no terminal | Abra o Quartus Prime digitando no terminal | ||

quartus20.1.sh | quartus20.1.sh | ||

Em seguida abra um arquivo para inserir o código VHDL. No menu superior selecione '''[File > New > Design Files: VHDL File]''' e '''[OK]''' | Em seguida abra um arquivo para inserir o código VHDL. No menu superior selecione '''[File > New > Design Files: VHDL File]''' e '''[OK]''' | ||

| − | + | ==PASSO 2== | |

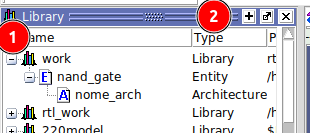

*Copie o código VHDL acima para o espaço de edição e salve o arquivo com o nome da '''entity''': ''nand_gate.vhd'', em um pasta exclusiva para este projeto. | *Copie o código VHDL acima para o espaço de edição e salve o arquivo com o nome da '''entity''': ''nand_gate.vhd'', em um pasta exclusiva para este projeto. | ||

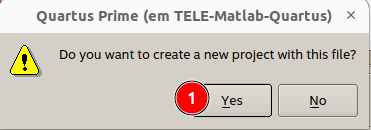

*Ao ser perguntado se deseja criar um novo projeto, responda '''[Yes]''' [[Arquivo:Quartus CreateProject.png| 200px]] | *Ao ser perguntado se deseja criar um novo projeto, responda '''[Yes]''' [[Arquivo:Quartus CreateProject.png| 200px]] | ||

| Linha 34: | Linha 34: | ||

:*Note na tela '''Summary''' os dados do projeto e clique '''[Finish]''' | :*Note na tela '''Summary''' os dados do projeto e clique '''[Finish]''' | ||

| − | + | ==PASSO 3== | |

Realize a '''Analysis & Synthesis''' ['''Processing > Start > Start Analysis & Synthesis'''], ou use um dos botões que o professor mostrou em aula. | Realize a '''Analysis & Synthesis''' ['''Processing > Start > Start Analysis & Synthesis'''], ou use um dos botões que o professor mostrou em aula. | ||

:*Analise o '''Compilation Report'''. | :*Analise o '''Compilation Report'''. | ||

| Linha 42: | Linha 42: | ||

4) Algum outro dado está diferente de zero? Quais? ___________________________ | 4) Algum outro dado está diferente de zero? Quais? ___________________________ | ||

| − | + | ==PASSO 4== | |

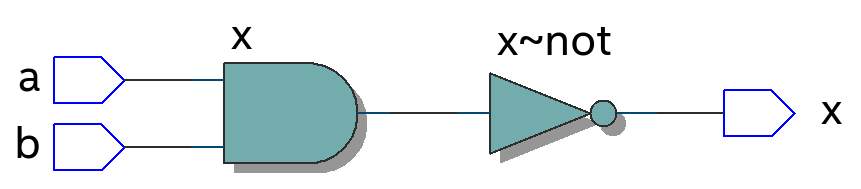

*Use o [[RTL Viewer]] para ver a descrição RTL do circuito. Selecione '''[Tools > Netlist Vieweres > RTL Viewer]'''. | *Use o [[RTL Viewer]] para ver a descrição RTL do circuito. Selecione '''[Tools > Netlist Vieweres > RTL Viewer]'''. | ||

:[[Arquivo:Quartus_RTL_nand_gate.png| 400px]] | :[[Arquivo:Quartus_RTL_nand_gate.png| 400px]] | ||

| Linha 53: | Linha 53: | ||

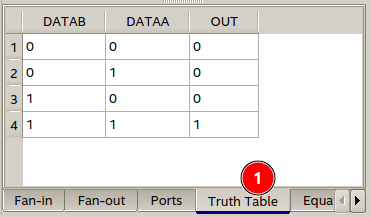

*Note que a tabela verdade mostrada corresponde novamente a uma porta AND. | *Note que a tabela verdade mostrada corresponde novamente a uma porta AND. | ||

| − | + | ==PASSO 5== | |

*Modifique a descrição do circuito para implementar o circuito da função Y = (A.B)' + C.D'B', salve como um novo arquivo '''Ckt2.vhd''' e de o mesmo nome '''ckt2''' para a entity. | *Modifique a descrição do circuito para implementar o circuito da função Y = (A.B)' + C.D'B', salve como um novo arquivo '''Ckt2.vhd''' e de o mesmo nome '''ckt2''' para a entity. | ||

| − | + | ==PASSO 6== | |

*Simulação do circuito usando o simulador ModelSim | *Simulação do circuito usando o simulador ModelSim | ||

*Se você já havia fechado o Quartus ou trocou de projeto, reabra o projeto '''nand_gate'''. Clique em '''[File > Open Project]''' e selecione a pasta onde salvou o projeto. Depois clique sobre o arquivo '''nand_gate.qpf'''. Note que abrir um projeto é diferente de abrir um arquivo, pois todos os arquivos de configuração estão associados a esse .qpf. | *Se você já havia fechado o Quartus ou trocou de projeto, reabra o projeto '''nand_gate'''. Clique em '''[File > Open Project]''' e selecione a pasta onde salvou o projeto. Depois clique sobre o arquivo '''nand_gate.qpf'''. Note que abrir um projeto é diferente de abrir um arquivo, pois todos os arquivos de configuração estão associados a esse .qpf. | ||

Edição das 09h00min de 20 de fevereiro de 2024

PASSO 0

Acesse a nuvem do IFSC usando um terminal via ssh:

USER=LOGIN_SIGAA ssh $USER@quartus.sj.ifsc.edu.br -XC

Insira a senha do SIGAA

LOGIN_SIGAA@quartus.sj.ifsc.edu.br's password:

PASSO 1

Abra o Quartus Prime digitando no terminal

quartus20.1.sh

Em seguida abra um arquivo para inserir o código VHDL. No menu superior selecione [File > New > Design Files: VHDL File] e [OK]

PASSO 2

- Copie o código VHDL acima para o espaço de edição e salve o arquivo com o nome da entity: nand_gate.vhd, em um pasta exclusiva para este projeto.

- Ao ser perguntado se deseja criar um novo projeto, responda [Yes]

- Os próximos passos podem ser realizados da seguinte forma:

- Na tela Introduction [Next >]

- Na tela Directory, Name, Top-Level Entity

- Anote onde o projeto será salvo.

/home/USER/PASTA_DO_PROJETO/

- Se quiser, troque a pasta clicando sobre os [...] e selecionando/criando a pasta onde o projeto será salvo.

- Recomendamos que no início você salve cada projeto em uma pasta separada.

- Note o nome do projeto. Se quiser pode mudá-lo

nand_gate

- Note o nome da top-level design entity

nand_gate

- Em seguida clique em [Next >]

- Na tela Project Type clique em [Next >]

- Na tela Add Filesclique em [Next >], pois note que seu arquivo "nand_gate.vhd" já está na lista dos arquivos do projeto.

- Na tela Family, Device & Board Settings, escolha a Family = [Cyclone IV E] e o Device = [EP4CE6E22A7] e clique em [Next >]

- Na tela EDA Tool Setting [Next >]

- Note na tela Summary os dados do projeto e clique [Finish]

PASSO 3

Realize a Analysis & Synthesis [Processing > Start > Start Analysis & Synthesis], ou use um dos botões que o professor mostrou em aula.

- Analise o Compilation Report.

1) Qual é a Top-level Entity? ___________________________ 2) Quantos elementos lógicos foram utilizados? ___________________________ 3) Quantos pinos foram utilizados? ___________________________ 4) Algum outro dado está diferente de zero? Quais? ___________________________

PASSO 4

- Use o RTL Viewer para ver a descrição RTL do circuito. Selecione [Tools > Netlist Vieweres > RTL Viewer].

- Analise o Diagrama RTL, e note que ele representa a implementação de uma porta AND seguida de um NOT.

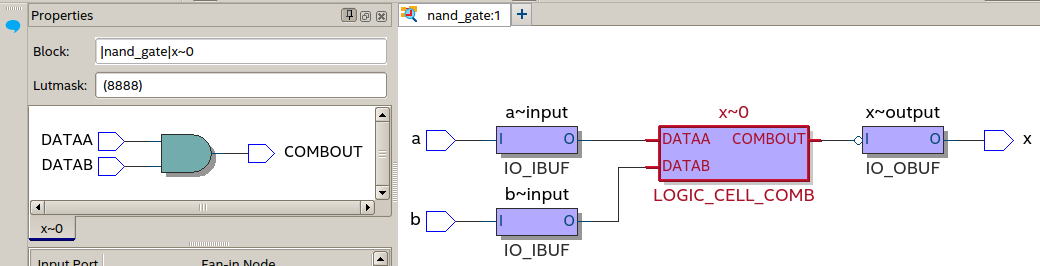

- Use o Technology Map Viewer para ver a como o circuito foi mapeado para os elementos lógicos disponíveis no dispositivo FPGA selecionado. Selecione [Tools > Netlist Vieweres > Technology Map Viewer (Post-Mapping)]. Ao abrir, clique direito sobre o símbolo LOGIC_CELL_COMB e selecione Properties para visualizar o que está implementado.

- Analise o Technolgy Map, e busque perceber que ele representa a mesma implementação de uma porta AND seguida de um NOT (onde está o NOT?).

- Lembre-se que apenas um circuito equivalente é mostrado, pois na prática essa célula contém uma LUT, o que corresponde a implementar diretamente a tabela verdade.

- Note que a tabela verdade mostrada corresponde novamente a uma porta AND.

PASSO 5

- Modifique a descrição do circuito para implementar o circuito da função Y = (A.B)' + C.D'B', salve como um novo arquivo Ckt2.vhd e de o mesmo nome ckt2 para a entity.

PASSO 6

- Simulação do circuito usando o simulador ModelSim

- Se você já havia fechado o Quartus ou trocou de projeto, reabra o projeto nand_gate. Clique em [File > Open Project] e selecione a pasta onde salvou o projeto. Depois clique sobre o arquivo nand_gate.qpf. Note que abrir um projeto é diferente de abrir um arquivo, pois todos os arquivos de configuração estão associados a esse .qpf.

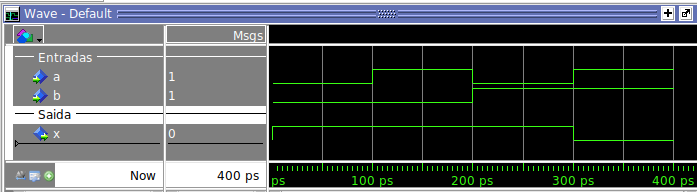

- Após ter feito a Analysis & Synthesis, abra o simulador RTL do Modelsim [Tools > Run Simulation Tool > RTL Simulation].

- Note que o ModelSim deverá abrir já com o seu projeto pronto para ser simulado.

# Errors: 0, Warnings: 0

- De um clique duplo sobre o nome da architecture. Isso faz com que essa arquitetura seja disponibilizada para simulação. Agora no painel Objects estão disponíveis os sinais de entrada (a, b) e o sinal de saída (x).

- Abra o painel Wave, [View > Wave]

- Segurando a tecla [Ctrl] selecione com o mouse os sinais que deseja visualizar (a, b, x), e arraste os sinais para o painel Wave.

- Execute a simulação por 100 ps. Digite no painel de Transcript o comando run ou run 100 ou run 100ps. Outra opção é clicar sobre o icone run

, ou ainda [Simulate > Run > Run 100].

, ou ainda [Simulate > Run > Run 100]. - Analise se essa simulação feita corresponde ao circuito proposto.

a = 0, b = 0 => x = 1.

- Para mudar o valor da entrada, clique direito sobre a linha da entrada (a ou b) e selecione [Force...], para definir o novo valor. Por exemplo: Value = 1;

- Obtenha a tabela verdade completa do circuito e confira se é identica a mostrada abaixo:

- Salve os comandos dados para obter esse resultado. clique sobre o painel Transcript e em seguida clique em [File > Save Transcript As...] nand_gate.do.