Mudanças entre as edições de "TCC-BrunoAntonio TCC Bruno"

| Linha 1: | Linha 1: | ||

| + | =Descrição do sistema= | ||

| + | O sistema inicialmente proposto é mostrado na figura abaixo. O sistema é composto por uma base de dados um computador e um leitor e tags RFID. | ||

| + | |||

| + | O computador (RaspbarryPI) esta conectado a uma base dados, na qual estão armazenadas as informações sore o atleta, e o leitor através de uma conexão UART. O leitor é composto por dois SoC (System on Chip) nrf51 sendo que um funciona como receptor em quanto outro funciona com transmissor, o leitor tem como objetivo fazer a comunicação entre o computador e as tags. O atleta tem uma tag no braço e uma na perna, a tag quando em modo de transmissão envia um numero de identificação e quando em modo de recepção a mesma pode ser reprogramada inserindo novas informações. | ||

| + | |||

| + | =Tag= | ||

| + | |||

=Esboço do Sistema= | =Esboço do Sistema= | ||

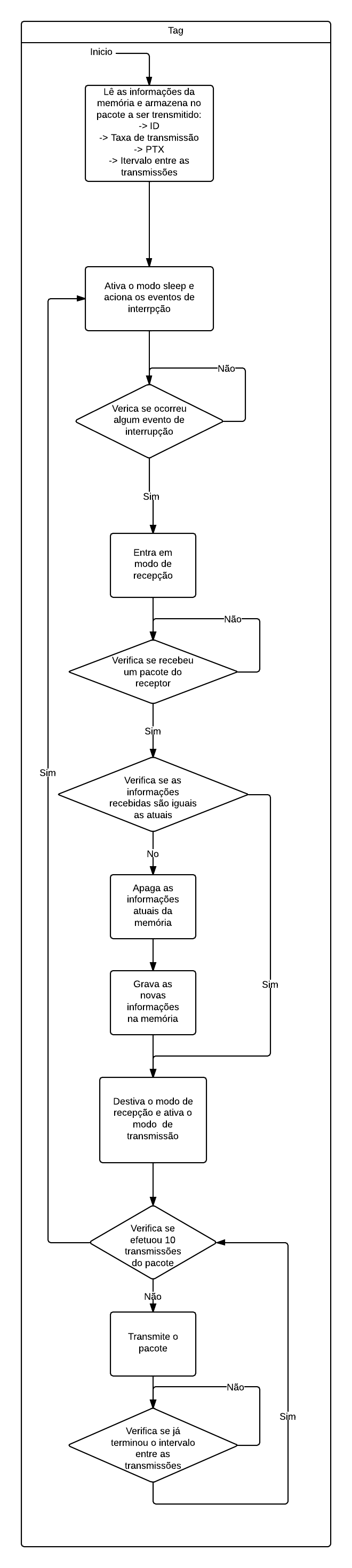

A imagem abaixo mostra o fluxograma do funcionamento inicialmente pensado para a tag no sistema. | A imagem abaixo mostra o fluxograma do funcionamento inicialmente pensado para a tag no sistema. | ||

[[Arquivo:Fluxograma_Sistema_Natação_NRF51.png]] | [[Arquivo:Fluxograma_Sistema_Natação_NRF51.png]] | ||

| − | |||

=Memória Flash= | =Memória Flash= | ||

Edição das 16h53min de 15 de abril de 2014

Descrição do sistema

O sistema inicialmente proposto é mostrado na figura abaixo. O sistema é composto por uma base de dados um computador e um leitor e tags RFID.

O computador (RaspbarryPI) esta conectado a uma base dados, na qual estão armazenadas as informações sore o atleta, e o leitor através de uma conexão UART. O leitor é composto por dois SoC (System on Chip) nrf51 sendo que um funciona como receptor em quanto outro funciona com transmissor, o leitor tem como objetivo fazer a comunicação entre o computador e as tags. O atleta tem uma tag no braço e uma na perna, a tag quando em modo de transmissão envia um numero de identificação e quando em modo de recepção a mesma pode ser reprogramada inserindo novas informações.

Tag

Esboço do Sistema

A imagem abaixo mostra o fluxograma do funcionamento inicialmente pensado para a tag no sistema.

Memória Flash

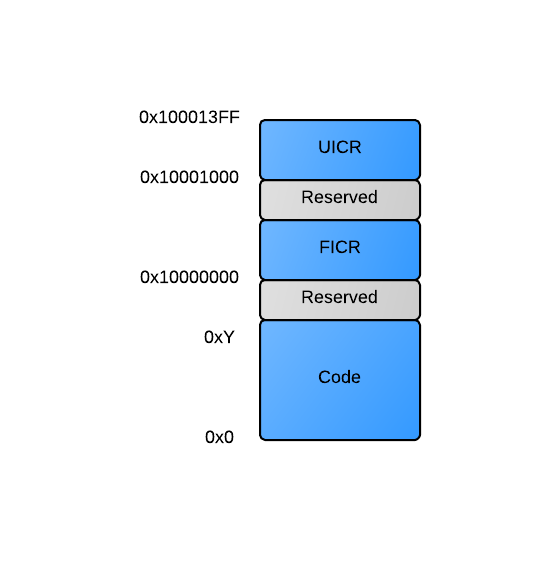

Como pode se visto através da imagem abaixo a memória flash do NRF51 é dividida basicamente em três partes:

Code: É a área reservada para o código porém pode ser utilizada pelo usuário para gravar informações.

FICR: Possui as configurações e informações dos registradores. Essa área vem programada de fabrica e não pode ser apagada.

UICR: Essa área é utilizada para gravar informações de configuração do usuário. Entre as configurações que podem ser feitas pelo usuário estão a definição do tamanho máximo da code region 0 e proteção para evitar a leitura da memória.

O tamanho máximo da área de código é Y onde: Y = tamanho_máximo_da_memória_flash - 1. Tendo como exemplo a placa PCA1000 do kit de desenvolvimento cujo o tamanho da memória flash é de 256 KB ou 0x40000 logo o ultimo endereço disponível para gravar na flash é 0x3FFFF. A área de código é dividida em paginas e único meio de apagar uma informação na área de código é apagar a pagina onde se encontra a informação e para isso é utilizado o primeiro endereço da pagina. Cada pagina possuí 1 KB logo se tivermos um dispositivo com 256 KB de memória flash ele terá 256 paginas, para se encontrar o primeiro endereço de uma determinada pagina basta seguir a seguinte equação: endereço = (nº_da_pagina - 1) * 1024.

Sleep Modes

System OFF

É o modo de economia de energia mai eficiente que o NRF51 pode entrar. Neste modo o processamento é reduzido ao minimo e todas as atividades sendo executadas são finalizadas. Os únicos mecanismos funcionando nesse modo são o de wake-up e o reset. O dispositivo pode sair desse estado através de um sinal DETECT gerado pelo GPIO, um sinal ANADETECT gerado pelo módulo LCOMP, ou um reset. Quando o dispositivo sai desse modo é gerado um reset.

System ON

Nesse a CPU e os periféricos selecionados podem ser induzidos a um estado aonde eles estão ativos e mais ou menos responsivos dependendo do sub modo de energia selecionado. Nesse modo a CPU pode tanto estar ativa quanto em modo sleep. A CPU pode entrar em modo sleep através das instruções WFI ou WFE. Quando selecionado o WFI a cpu voltara a ser ativada quando houver uma requisição de interrupção do NVIC. Quando WFE for selecionado a CPU voltara a ser ativada quando houver qualquer requisição de interrupção. O System ON possui dois sub modos de energia, são eles:

Costant Latency

Esse modo irá manter a latência de wake-up da CPU e a resposta da task PPI constante e minima. O consumo de energia no entanto irá aumentar.

Low Power

Esse é o sub-modo padrão do System ON e é mais eficiente e econômico que o Constant Latency, porém a latência da CPU e a resposta da PPI task são variáveis.