Simulação Funcional usando o ModelSim

Ir para navegação

Ir para pesquisar

Figura 1 - EDA Tools Options

Fonte: Elaborado pelo autor.

Figura 2 - EDA Tools Settings

Fonte: Elaborado pelo autor.

Essa página descreve os passos a serem realizados para a simulação funcional no ModelSim de um circuito implementado no Quartus Prime.

Antes de acessar o simulador, o circuito deve estar descrito em VHDL, e o Quartus Prime configurado corretamente.

- Passo 1

Digite o seguinte código VHDL ou seu próprio código e após salvar o projeto faça a Analysis & Synthesis [Crtl+k].

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity bin2bcd is

port (

A : in std_logic_vector (6 downto 0);

sd, su : out std_logic_vector (3 downto 0)

);

end entity;

architecture ifsc_v1 of bin2bcd is

signal A_uns : unsigned (6 downto 0);

signal sd_uns, su_uns : unsigned (6 downto 0);

begin

sd <= std_logic_vector(resize(sd_uns, 4));

su <= std_logic_vector(resize(su_uns, 4));

sd_uns <= A_uns/10;

su_uns <= A_uns rem 10;

A_uns <= unsigned(A);

end architecture;

- Passo 1

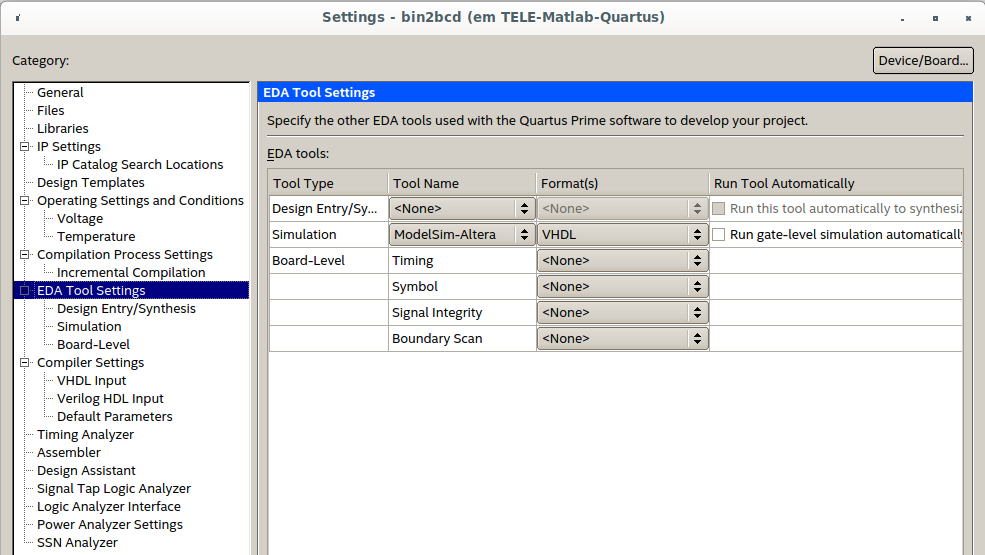

Verifique se o caminho para o ModelSim está correto [Tools > Options > General > EDA Tools Options]. O campo Modelsim-Altera deve estar com

/opt/intelFPGA/20.1/modelsim_ae/linuxaloem

Figura 1 - EDA Tools Options

- Passo 2

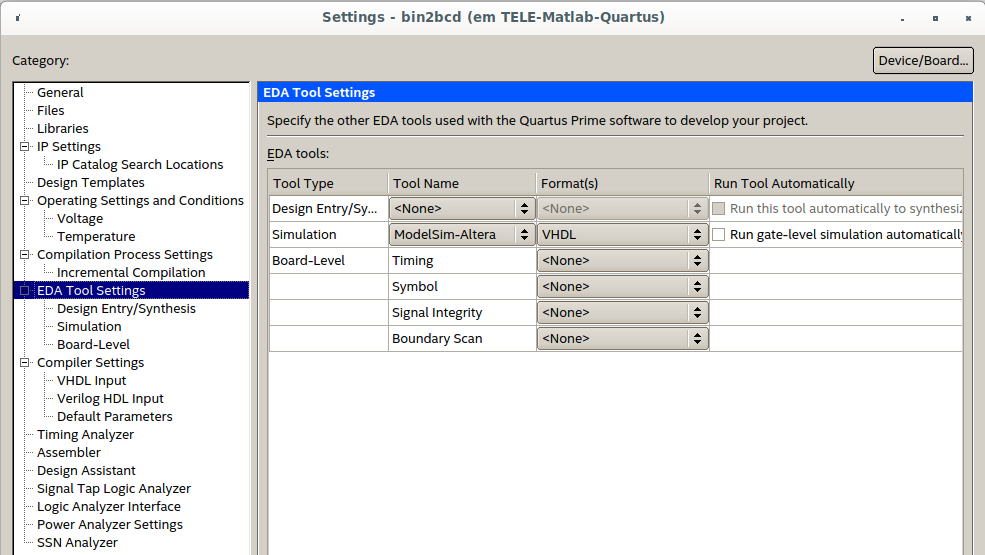

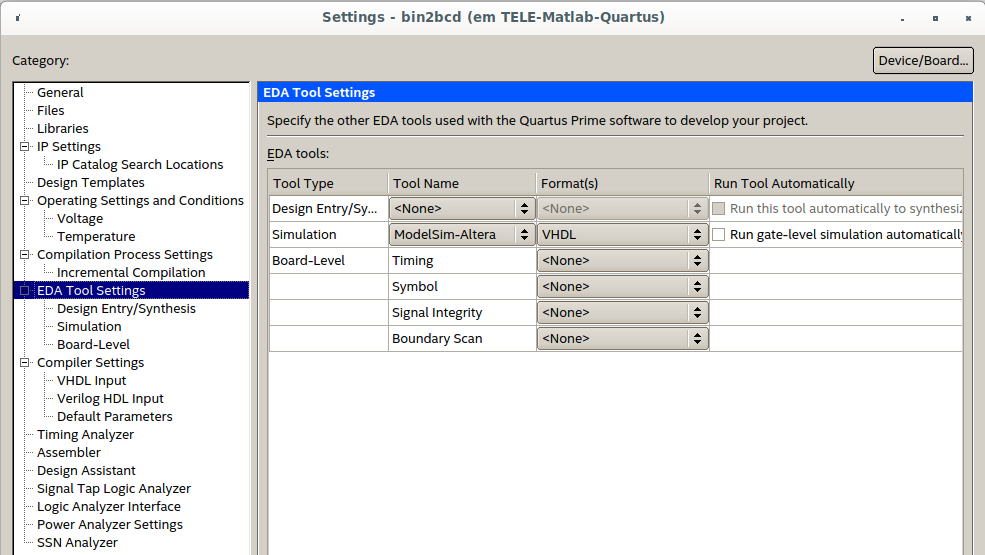

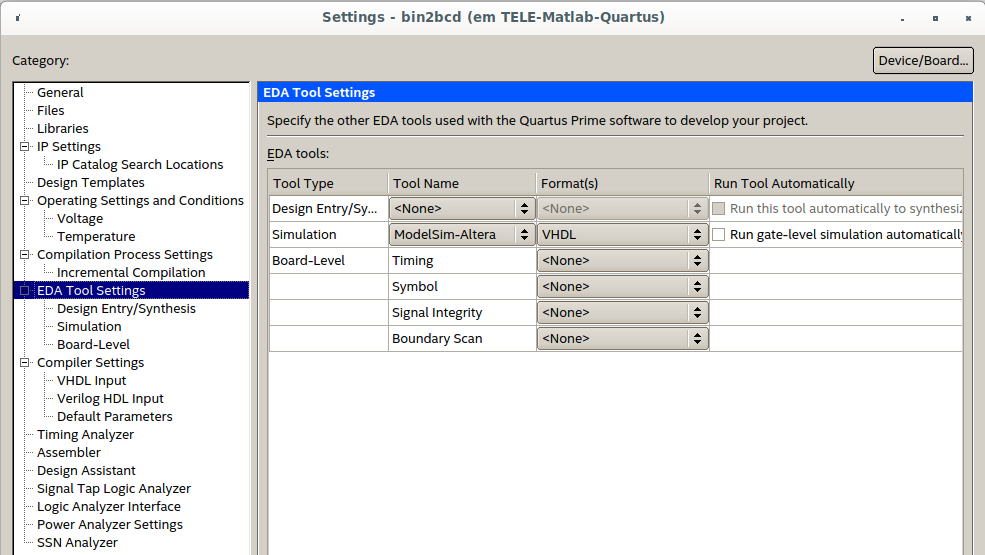

Verifique se o formato do arquivo de simulação no ModelSim está correto [Assigments > Settings.. > General > EDA Tools Settings ]. O campo Formats da linha Simulation deve estar com

VHDL

Figura 2 - EDA Tools Settings

- Passo 3