Mudanças entre as edições de "Oficina NCO e Filtros digitais"

| Linha 76: | Linha 76: | ||

Clicando no botão [[Imagem:PJI29008-SignalTap-botao2.png]], o ''SignalTap'' inicia a captação de informações. Os sinais senoidais precisam ainda ser configurados de acordo com o tipo de dado. Pare a captação e clique com o botão direito em cada um, e em '''Bus Display Format''', selecione '''Signed Line Chart'''. Na barra superior da ferramenta, clique com o botão direito e escolha '''Time Units'''. Digite o valor '''50''' e selecione '''MHz''' no menu. Clique na barra superior e arraste a barra temporal para fechar um período da onda mais lenta. Repare que ela possui ''1 us'', equivalente à uma onda de ''1 MHz''. | Clicando no botão [[Imagem:PJI29008-SignalTap-botao2.png]], o ''SignalTap'' inicia a captação de informações. Os sinais senoidais precisam ainda ser configurados de acordo com o tipo de dado. Pare a captação e clique com o botão direito em cada um, e em '''Bus Display Format''', selecione '''Signed Line Chart'''. Na barra superior da ferramenta, clique com o botão direito e escolha '''Time Units'''. Digite o valor '''50''' e selecione '''MHz''' no menu. Clique na barra superior e arraste a barra temporal para fechar um período da onda mais lenta. Repare que ela possui ''1 us'', equivalente à uma onda de ''1 MHz''. | ||

| − | [[Imagem:PJI29008-OficinaSignalTap1.png|thumb|Sinais senoidais visualizados no SignalTap II| | + | [[Imagem:PJI29008-OficinaSignalTap1.png|thumb|Sinais senoidais visualizados no SignalTap II|900px|center]] |

<br style="clear:both;"> | <br style="clear:both;"> | ||

Edição das 11h44min de 15 de março de 2017

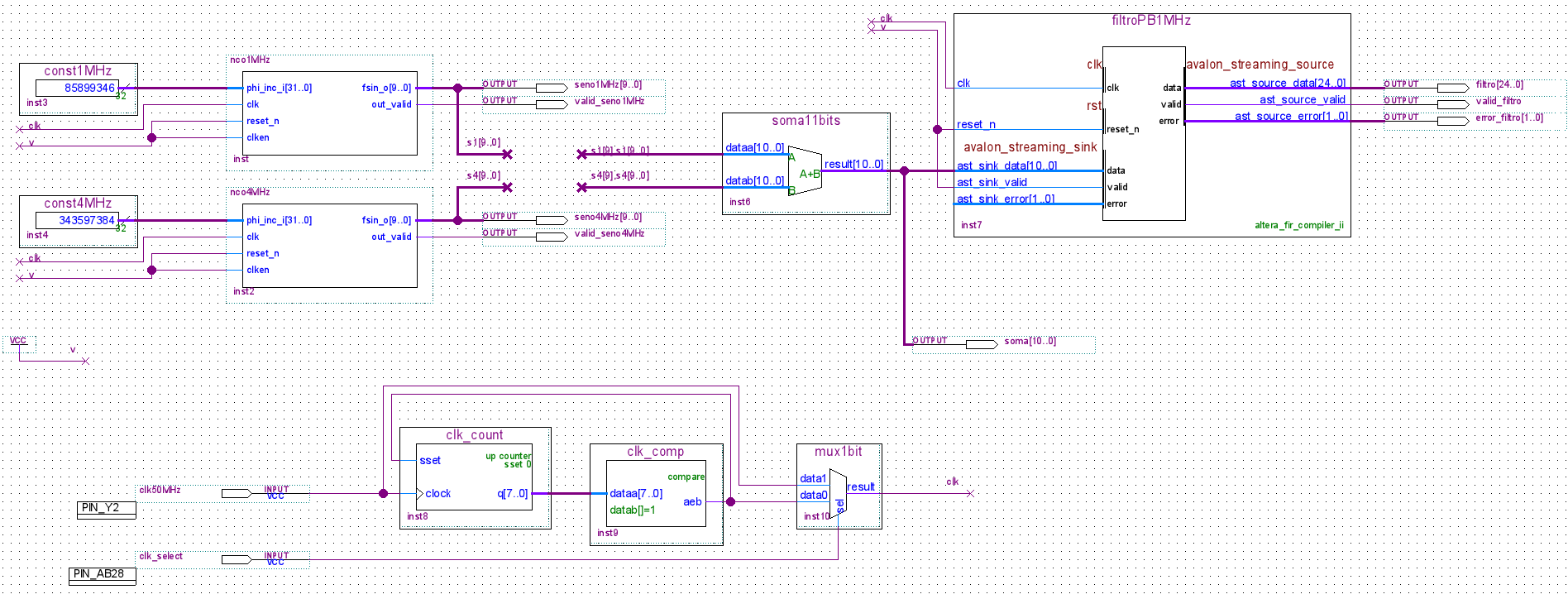

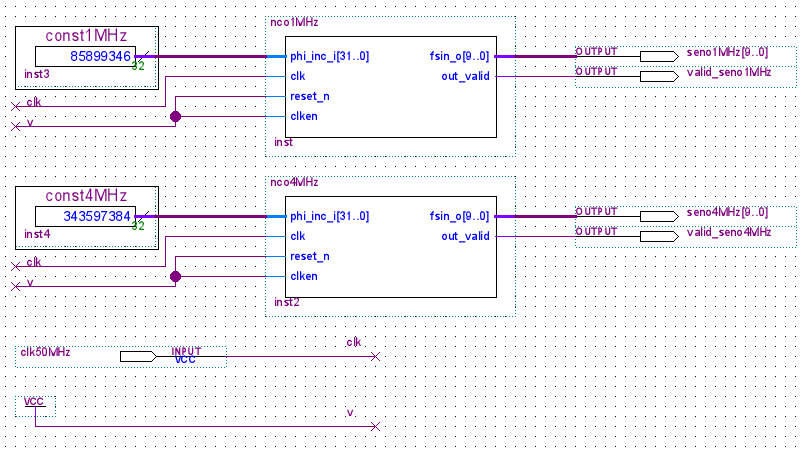

Esta página traz um roteiro para a geração de sinais senoidais e a construção de filtros digitais em FPGAs Altera, usando o Quartus II. O sistema criado (figura abaixo) gera sinais senoidais de 1 MHz e 4 MHz, soma os dois sinais e realiza uma filtragem passa baixas, visando manter apenas o sinal de 1 MHz. Está prevista a construção de um multiplexador e de um divisor de clock. Todos os blocos utilizaram a ferramenta nativa do Quartus II, o MegaWizard Plug-In Manager. O sistema foi desenvolvido no kit didático Altera DE2-115, com um FPGA Cyclone IV EP4CE115F29C7.

- Crie um projeto e adicione um arquivo do tipo Block Diagram/Schematic File

Geração dos sinais senoidais

Nesta seção, dois sinais senoidais serão criados, um de 1 MHz e outro de 4 MHz

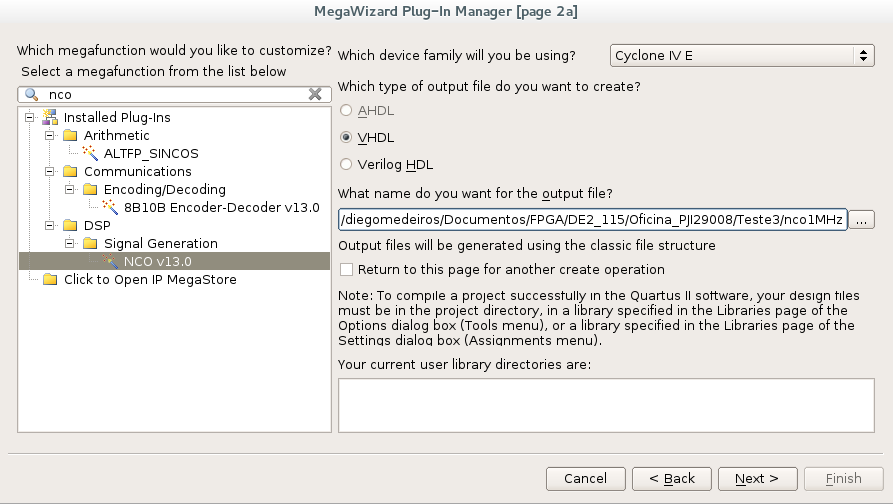

- Abrir o MegaWizard Plug-In Manager (Menu Tools)

- Página 1: Selecionar Create a new custom megafunction variation

- Página 2: Escrever na lupa nco, escolher a pasta para os arquivos e incluir um nome (sugestão: nco1MHz e nco4MHz)

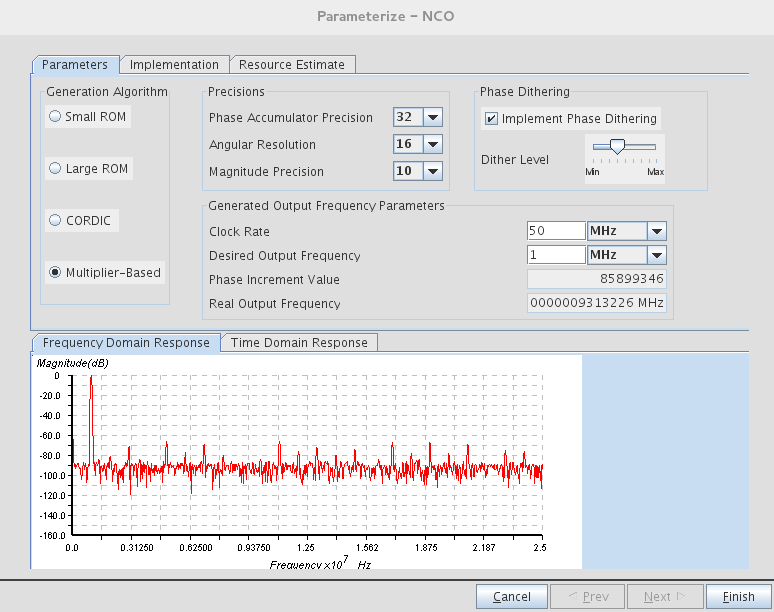

- Na janela do NCO, clique em Step1: Parameterize

- Em Magnitude Precision, escolha o número de bits por amostra desejado para o sinal senoidal (sugestão: 10)

- Em Clock Rate, escolha o clock da placa (no caso, 50 MHz). Digite o valor e tecle ENTER

- Em Desired Output Frequency, escolha a frequência desejada para o sinal senoidal (1 MHz). Digite o valor e tecle ENTER

- Anote o valor disponibilizado em Phase Increment Value (Para 1MHz, 85899346). Você pode dar dois cliques no valor e usar o CTRL+C para copiar. Esse número pode ser encontrado também através da equação:

- onde as siglas se referem às iniciais dos parâmetros

- No canto superior direito da aba Implementation, marque a opção Single Output

- Clique em Finish para encerrar a parametrização

- Clique em Generate para gerar o bloco

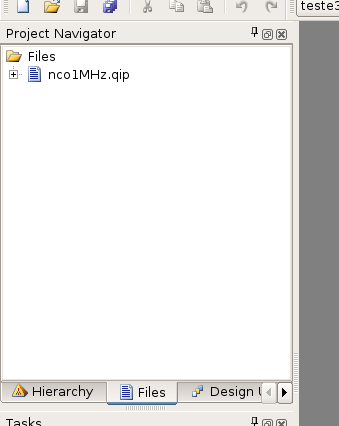

- Quando o processamento encerrar, clique em Exit e selecione Yes quando questionado sobre adicionar o arquivo gerado ao projeto

- De volta à janela padrão do Quartus II repare que o arquivo nco1MHz.qip foi adicionado ao projeto

O mesmo procedimento deve ser feito para o NCO de 4 MHz (Phase Increment Value 343597384)

Com os dois NCOs criados, adicione-o ao projeto. Repare que ele possui entradas de clock, um reset ativo baixo (repare no "_n" no nome da entrada), um enable e uma entrada de 32 bits chamada phi_inc_i[31..0]. É através dessa entrada que o NCO é controlado, e a constante Phase Increment Value deve ser passada. Para isso, use um outro MegaWizard, o LPM_CONSTANT. Ao fazer sua configuração, use o nome const1MHz e const4MHz. Sua parametrização é simples, com o número de bits da constante (32, para estar de acordo com o esperado pelo NCO), e o seu valor em decimal (85899346 e 343597384). Na página Summary, marque todos os tipos de arquivo disponíveis.

Adicione os componentes ao projeto e realize as ligações como abaixo:

Compile o projeto, e no Pin Planner (menu Assignments), configure apenas a porta clk50MHz, no Location PIN_Y2

Configurando o SignalTap para visualização dos sinais gerados

- Adicione um arquivo novo ao projeto, e no tipo do arquivo, selecione SignalTap II Logic Analyzer File

- Na aba Setup, dê um duplo-clique na área em branco

- Se ainda não estiver selecionado, clique no botão

para abrir a seção de mais opções

para abrir a seção de mais opções - Em Filter, selecione SignalTap II: pre-synthesis

- Clique no botão List

- Na janela Nodes Found, selecione os sinais (use CTRL):

- seno1MHz

- seno4MHz

- valid_seno1MHz

- valid_seno4MHz

- Jogue para a direita com o botão >

- Clique em OK

- Se ainda não estiver selecionado, clique no botão

- Na janela Signal Configuration, seção Clock, clique no botão ... e use o mesmo procedimento para encontrar o sinal clk50MHz

- Salve o arquivo com o nome stp2.stp

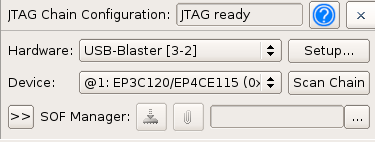

Compile o projeto e faça a programação da placa. Abra o arquivo stp2.stp. Caso necessário, faça a configuração correta da JTAG, podendo usar o botão Scan Chain.

Clicando no botão ![]() , o SignalTap inicia a captação de informações. Os sinais senoidais precisam ainda ser configurados de acordo com o tipo de dado. Pare a captação e clique com o botão direito em cada um, e em Bus Display Format, selecione Signed Line Chart. Na barra superior da ferramenta, clique com o botão direito e escolha Time Units. Digite o valor 50 e selecione MHz no menu. Clique na barra superior e arraste a barra temporal para fechar um período da onda mais lenta. Repare que ela possui 1 us, equivalente à uma onda de 1 MHz.

, o SignalTap inicia a captação de informações. Os sinais senoidais precisam ainda ser configurados de acordo com o tipo de dado. Pare a captação e clique com o botão direito em cada um, e em Bus Display Format, selecione Signed Line Chart. Na barra superior da ferramenta, clique com o botão direito e escolha Time Units. Digite o valor 50 e selecione MHz no menu. Clique na barra superior e arraste a barra temporal para fechar um período da onda mais lenta. Repare que ela possui 1 us, equivalente à uma onda de 1 MHz.