Mudanças entre as edições de "Medição de tempos de propagação em circuitos combinacionais - Quartus II"

| Linha 2: | Linha 2: | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | |||

library ieee; | library ieee; | ||

use ieee.std_logic_1164.all; | use ieee.std_logic_1164.all; | ||

| Linha 8: | Linha 7: | ||

entity hamming_distance is | entity hamming_distance is | ||

generic ( | generic ( | ||

| − | N: natural := | + | N: natural := 25; |

M: natural := 5); -- M = ceil(log2(N)) | M: natural := 5); -- M = ceil(log2(N)) | ||

port( | port( | ||

| Linha 31: | Linha 30: | ||

y <= std_logic_vector(sum); | y <= std_logic_vector(sum); | ||

end architecture; | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | |||

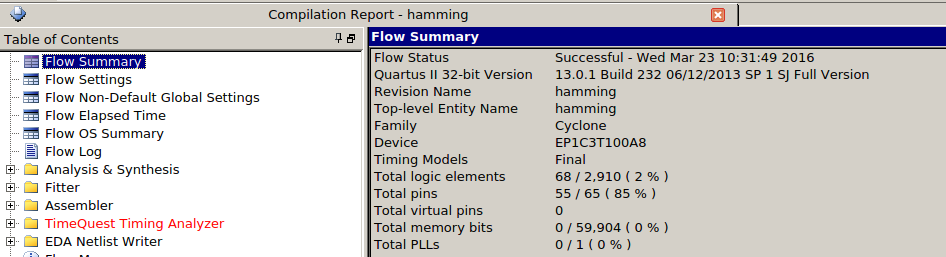

| + | Na sequência abaixo, foi utilizado o Quartus II 32-bit Version 13.0.1 Build 232, compilando o circuito para o dispositivo FPGA da ALTERA '''EP1C3T100A8''' da familia '''Cyclone'''. A escolha dessa família e versão do Quartus se deve ao fato de as novas versões 14.0 em diante não serem mais compatíveis com a família '''Cyclone''' básica. Em função de termos uma menor quantidade de célula, os resultados mostrados abaixo são melhor visualizados neste dispositivo do que em dispositivos maiores. Note que eventualmente ao utilizar vetores de entrada maiores, o compilador pode acusar falta de pinos para mapear todas as portas do circuito. Neste caso utilize dispositivos com maior número de de pinos. | ||

| + | |||

| + | Para realizar a verificações abaixo descritas, inicialmente crie um projeto com o código VHDL do circuito '''hamming_distance''' e realize a compilação ('''Processing > Start Compilation'''). | ||

| + | ==Área ocupada no FPGA pelo circuito== | ||

| + | Verifique o número de Elementos lógicos utilizados pelo circuito. No caso mostrado abaixo estão sendo utilizados 68 elementos lógicos entre os 2910 disponíveis. Também são utilizados 55 dos 65 pinos de I/O disponíveis. | ||

| − | + | [[Arquivo:LogicalElements_HammingDistance.png | 600 px]] | |

| + | |||

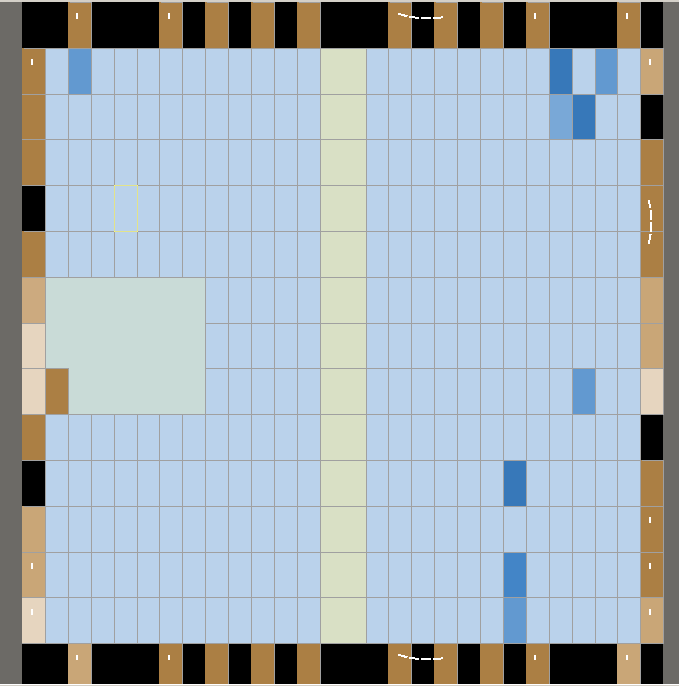

| + | Observe a disposição desses elementos no '''Chip Planner''' ('''Tools > Chip Planner'''). Note que como nenhuma restrição de tempo foi inserida, os elementos lógicos utilizados estão espalhado no dispositivo. Note que a intensidade da cor azul indica a taxa de ocupação. | ||

| + | |||

| + | [[Arquivo:ChipPlanner_HammingDistance.png | 600 px]] | ||

==Tempo de Propagação entre entrada e saída== | ==Tempo de Propagação entre entrada e saída== | ||

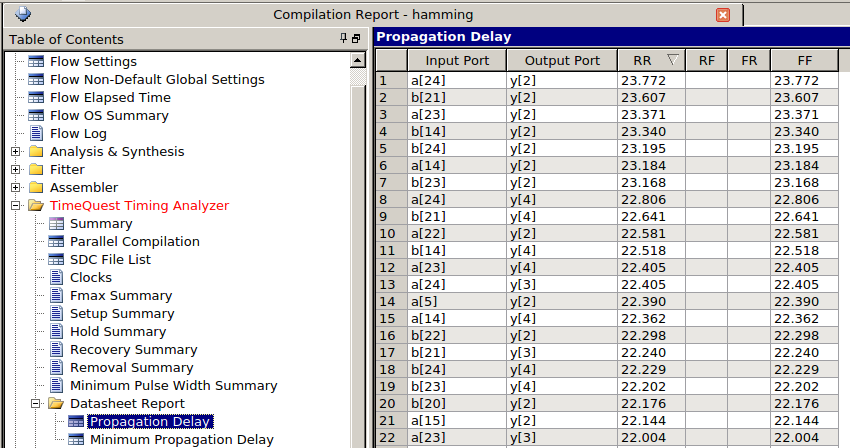

| − | Para | + | Para determinar os tempos de propagação entre cada bit de entrada e os bits de saída analise o "Compilation Report" ('''Processing > Compilation Report > TimeQuest Timing Analyzer >Datasheet Report > Propagation Delay'''). |

| + | |||

| + | Para encontrar o caminho crítico ("Critical Path") do circuito ordene os tempos de propagação do maior para menor. No exemplo da figura abaixo o caminho crítico é entre a entrada a[24] e saída y[2], com tempo de propagação de 23,772 ns. | ||

| + | |||

| + | [[Arquivo:CriticalPath_HammingDistance.png | Tempos de Propagação |600 px]] | ||

| + | |||

| + | |||

| − | + | ==Visualização dos tempos de propagação no Chip Planner== | |

| + | Para visualizar os tempos de | ||

Edição das 10h45min de 23 de março de 2016

O circuito abaixo realiza o cálculo da distância de Hamming entre dois sinais. O hardware está descrito em VHDL de forma genérica para permitir o estudo dos diferentes tempo de propagação e área do chip ocupado pelo circuito conforme as restrições de tempo impostas. Os valores de N e M definem respectivamente o tamanho dos vetor de entrada a e b e do vetor de saída y. A distância de Hamming é fornecida através de um número binário sem sinal. Note que M = ceil(log2(N)), ou seja para N = 8 bits => M = 4 bits, pois o número 8 é representado como "1000".

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity hamming_distance is

generic (

N: natural := 25;

M: natural := 5); -- M = ceil(log2(N))

port(

a, b : in std_logic_vector (N-1 downto 0);

y : out std_logic_vector (M-1 downto 0));

end entity;

architecture ifsc_arch_gen of hamming_distance is

signal diff: unsigned (N-1 downto 0);

signal sum: unsigned (M-1 downto 0);

begin

diff <= unsigned(a xor b);

process (diff)

variable tmp : integer range 0 to N;

begin

tmp := 0;

for i in diff'range loop

tmp := tmp + to_integer(unsigned'('0' & diff(i)));

end loop;

sum <= to_unsigned(tmp,M);

end process;

y <= std_logic_vector(sum);

end architecture;

Na sequência abaixo, foi utilizado o Quartus II 32-bit Version 13.0.1 Build 232, compilando o circuito para o dispositivo FPGA da ALTERA EP1C3T100A8 da familia Cyclone. A escolha dessa família e versão do Quartus se deve ao fato de as novas versões 14.0 em diante não serem mais compatíveis com a família Cyclone básica. Em função de termos uma menor quantidade de célula, os resultados mostrados abaixo são melhor visualizados neste dispositivo do que em dispositivos maiores. Note que eventualmente ao utilizar vetores de entrada maiores, o compilador pode acusar falta de pinos para mapear todas as portas do circuito. Neste caso utilize dispositivos com maior número de de pinos.

Para realizar a verificações abaixo descritas, inicialmente crie um projeto com o código VHDL do circuito hamming_distance e realize a compilação (Processing > Start Compilation).

Área ocupada no FPGA pelo circuito

Verifique o número de Elementos lógicos utilizados pelo circuito. No caso mostrado abaixo estão sendo utilizados 68 elementos lógicos entre os 2910 disponíveis. Também são utilizados 55 dos 65 pinos de I/O disponíveis.

Observe a disposição desses elementos no Chip Planner (Tools > Chip Planner). Note que como nenhuma restrição de tempo foi inserida, os elementos lógicos utilizados estão espalhado no dispositivo. Note que a intensidade da cor azul indica a taxa de ocupação.

Tempo de Propagação entre entrada e saída

Para determinar os tempos de propagação entre cada bit de entrada e os bits de saída analise o "Compilation Report" (Processing > Compilation Report > TimeQuest Timing Analyzer >Datasheet Report > Propagation Delay).

Para encontrar o caminho crítico ("Critical Path") do circuito ordene os tempos de propagação do maior para menor. No exemplo da figura abaixo o caminho crítico é entre a entrada a[24] e saída y[2], com tempo de propagação de 23,772 ns.

Visualização dos tempos de propagação no Chip Planner

Para visualizar os tempos de