Mudanças entre as edições de "MIC29004-2020-1"

| Linha 25: | Linha 25: | ||

**[http://docente.ifsc.edu.br/roberto.matos/mic_public/material/mic-slides_1-memoria.pdf Slides Memória] | **[http://docente.ifsc.edu.br/roberto.matos/mic_public/material/mic-slides_1-memoria.pdf Slides Memória] | ||

**[[MIC29004-lista1 | Lista de Exercícios: Memória, Arquitetura, Organização e BIP]] | **[[MIC29004-lista1 | Lista de Exercícios: Memória, Arquitetura, Organização e BIP]] | ||

| + | |||

| + | == Exemplo de Caminho de Dados Rudimentar == | ||

| + | * [http://docente.ifsc.edu.br/roberto.matos/mic_public/first_cpu/first_cpu.qar Projeto Quartus] | ||

| + | * Teste com uma carga, duas somas, uma subtração e uma leitura em sequência. | ||

| + | ::http://docente.ifsc.edu.br/roberto.matos/mic_public/first_cpu/test_first_cpu.png | ||

| + | |||

Edição das 12h51min de 14 de fevereiro de 2020

Microprocessadores: Diário de Aula 2020-1

- Professor: Roberto de Matos

- Encontros: 3ª feira às 13:30 e 4ª feira às 15:40h

- Local: Laboratório de Sistemas Digitais

- Atendimento Paralelo: 3ª feira às 10h e 5ª feira às 14:30h (1h cada)

- Plano de Ensino

- Cronograma de Aulas

Aula 11/02/2019: Apresentação

- Apresentação do professor.

- Apresentação da disciplina: conteúdo, bibliografia e avaliação.

Aula 13/02/2019: Introdução à Memória

- Objetivo:

- Revisão

- Registradores

- Exemplo Circuito

- Memória

- Material:

Exemplo de Caminho de Dados Rudimentar

- Projeto Quartus

- Teste com uma carga, duas somas, uma subtração e uma leitura em sequência.

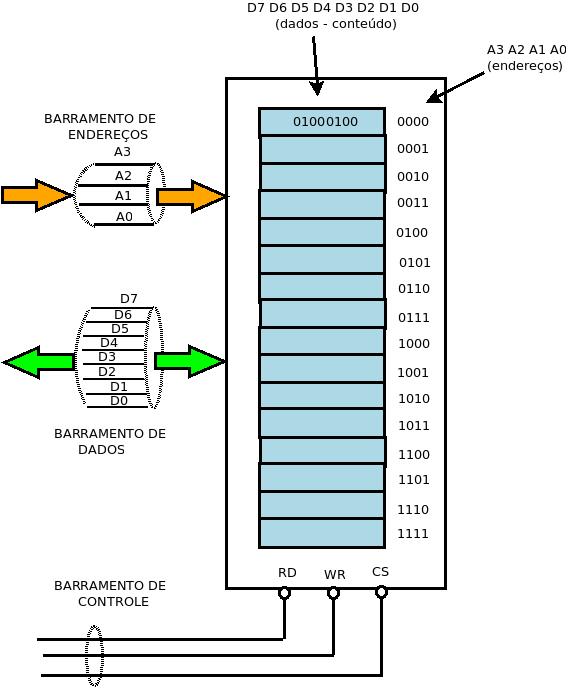

Diagrama em blocos da memória e barramentos

No diagrama abaixo está representado um bloco de memória primária de 16x8 (dezesseis endereços por 8 bits).

- Note que uma posição de memória pode ser vista como uma caixa que possue um endereço e um conteúdo.

- O conteúdo associado a posição de memória é uma palavra binária e, neste caso, possui 8 bits.

Para que us dispositivo externo possa "acessar" a memória para leitura ou escrita, ele deve se utilizar de um conjunto de fios que chamamos de barramentos.

Barramento de Endereços

Este barramento permite determinar o endereço de uma posição a ser acessada na memória. Um barramento de 4 linhas de endereço é designado por A3,A2,A1 e A0.

Supondo uma memória com endereços designados da forma hexadecimal de 0h a Fh. Supondo que A3 seja associado ao bit mais significativo e A0 ao bit menos significativo. Então, para acessar a posição Bh de memória, deve-se injetar A3=1, A2=0, A1=1 e A0=1. Note que

O termo "injetar" significa aqui que um dispositivo externo deve forçar tensão nas linhas do barramento. Esta tensão depende da tecnologia utilizada. Poderia ser, por exemplo, 5V para o nível lógico 1 e 0V par ao nível lógico 0.,