Mudanças entre as edições de "MIC29004-2016-1 Microprocessadores - Engenharia"

| Linha 10: | Linha 10: | ||

=Recursos= | =Recursos= | ||

| − | *[[Media:mic-slides_2-handout.pdf|Introdução à Microprocessadores]] | + | *[[Media:mic-slides_2-handout.pdf| Introdução à Microprocessadores]] |

*[[Media:bip.pdf|Arquitetura e Organização do BIP]] | *[[Media:bip.pdf|Arquitetura e Organização do BIP]] | ||

*[[Media:mic-slides_3-handout.pdf|Microcontrolador e 8051]] | *[[Media:mic-slides_3-handout.pdf|Microcontrolador e 8051]] | ||

=Aulas= | =Aulas= | ||

| + | |||

==Aula 01 (24/03/2016)== | ==Aula 01 (24/03/2016)== | ||

| Linha 20: | Linha 21: | ||

*Apresentação inicial; | *Apresentação inicial; | ||

*Visão geral do funcionamento de um sistema microprocessado. | *Visão geral do funcionamento de um sistema microprocessado. | ||

| + | |||

==Aula 02 (27/03/2016)== | ==Aula 02 (27/03/2016)== | ||

| Linha 29: | Linha 31: | ||

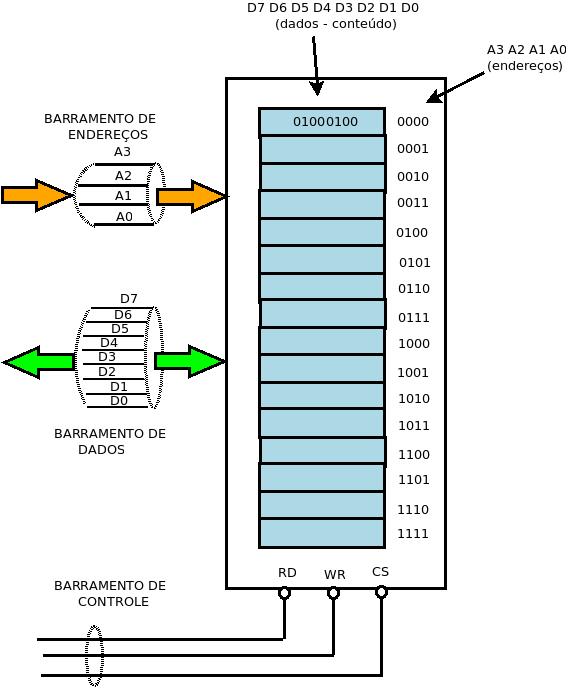

===Diagrama em blocos da memória e barramentos=== | ===Diagrama em blocos da memória e barramentos=== | ||

| − | No diagrama abaixo está representado um bloco de memória primária de | + | No diagrama abaixo está representado um bloco de memória primária de 16 x 8 (dezesseis endereços por 8 bits). |

| − | *Note que uma posição de memória pode ser vista como uma caixa que | + | *Note que uma posição de memória pode ser vista como uma caixa que possui um endereço e um conteúdo. |

*O conteúdo associado a posição de memória é uma palavra binária e, neste caso, possui 8 bits; | *O conteúdo associado a posição de memória é uma palavra binária e, neste caso, possui 8 bits; | ||

| Linha 48: | Linha 50: | ||

O termo "injetar" significa aqui que um dispositivo externo deve forçar tensão nas linhas do barramento. | O termo "injetar" significa aqui que um dispositivo externo deve forçar tensão nas linhas do barramento. | ||

Esta tensão depende da tecnologia utilizada. Poderia ser, por exemplo, 5V para o nível lógico 1 e 0V par ao nível lógico 0., | Esta tensão depende da tecnologia utilizada. Poderia ser, por exemplo, 5V para o nível lógico 1 e 0V par ao nível lógico 0., | ||

| − | |||

| − | |||

===Tarefa === | ===Tarefa === | ||

| Linha 62: | Linha 62: | ||

==Aula 04 (04/04/2016)== | ==Aula 04 (04/04/2016)== | ||

| − | * | + | * Memória RAM e sua estrutura |

| − | + | * Análise do comportamento (diagrama em blocos) | |

| − | * | + | * Modo de Escrita (WR) |

| − | |||

| − | + | * Modo de Leitura (RD) | |

| − | * | + | * Habilitação (CE) |

| − | |||

| − | |||

| − | |||

| − | + | === Atividade 01 === | |

| − | * | + | *[[Media:apostilamemorias.pdf|Slides Memória]] |

| − | ==Aula | + | ==Aula 05 (07/04/2016)== |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | * Introdução ao BIP | |

| − | + | * Upcode | |

Edição das 17h02min de 4 de abril de 2016

Informações Gerais

- Professor: Clayrton Monteiro Henrique

e-mail: clayrton.henrique@ifsc.edu.br

Plano de Ensino

Recursos

Aulas

Aula 01 (24/03/2016)

- Apresentação inicial;

- Visão geral do funcionamento de um sistema microprocessado.

Aula 02 (27/03/2016)

- Elemento de Memória;

- Flip Flop Tipo D;

Diagrama em blocos da memória e barramentos

No diagrama abaixo está representado um bloco de memória primária de 16 x 8 (dezesseis endereços por 8 bits).

- Note que uma posição de memória pode ser vista como uma caixa que possui um endereço e um conteúdo.

- O conteúdo associado a posição de memória é uma palavra binária e, neste caso, possui 8 bits;

Para que um dispositivo externo possa "acessar" a memória para leitura ou escrita, ele deve se utilizar de um conjunto de fios que chamamos de barramentos.

Barramento de Endereços

Este barramento permite determinar o endereço de uma posição a ser acessada na memória. Um barramento de 4 linhas de endereço é designado por A3,A2,A1 e A0.

Supondo uma memória com endereços designados da forma hexadecimal de 0h a Fh. Supondo que A3 seja associado ao bit mais significativo e A0 ao bit menos significativo. Então, para acessar a posição Bh de memória, deve-se injetar A3=1, A2=0, A1=1 e A0=1. Note que

O termo "injetar" significa aqui que um dispositivo externo deve forçar tensão nas linhas do barramento. Esta tensão depende da tecnologia utilizada. Poderia ser, por exemplo, 5V para o nível lógico 1 e 0V par ao nível lógico 0.,

Tarefa

Aula 03 (31/03/2016)

- Memórias - Tipos e características construtivas

- Associação de memórias e exercícios

Aula 04 (04/04/2016)

- Memória RAM e sua estrutura

- Análise do comportamento (diagrama em blocos)

- Modo de Escrita (WR)

- Modo de Leitura (RD)

- Habilitação (CE)

Atividade 01

Aula 05 (07/04/2016)

- Introdução ao BIP

- Upcode