MIC29004-2013-2

Revisão de 20h55min de 5 de setembro de 2013 por Roberto.matos (discussão | contribs) (→Registradores)

Microprocessadores: Diário de Aula 2013-2

Professor: Roberto de Matos

Encontros: 4ª feira 9:40 e 6ª feira 9:40

Atendimento paralelo: 4ª feira das 13:30 às 15:20.

Aula 16/08/2013: Apresentação

- Apresentação do professor.

- Apresentação dos alunos: Nome, perfil, preferências, etc.

- Apresentação da disciplina: conteúdo, bibliografia e avaliação.

- Aula Introdutória: Projetos práticos com Microcontroladores

Aula 21/08/2013: Histórico

- Evolução dos processadores

Aula 23/08/2013:

- Introdução a Arquitetura de Computadores

- Conceito de Processador (Unidade de Controle + Unidade de Processamento)

- Memória, Registradores, Barramentos

Aula 28/08/2013: IAS

- Arquitetura Von Neumann

- Arquitetura IAS

- Execução de um Programa (Acesso a memória, Registradores Internos, Sinais de Controle)

- Assembly IAS (Classes de Instruções)

Aula 30/08/2013: Não Houve Aula

- Paralisação

Aula 04/09/2013: IAS Sim

Objetivo

Ao final da aula o aluno deverá:

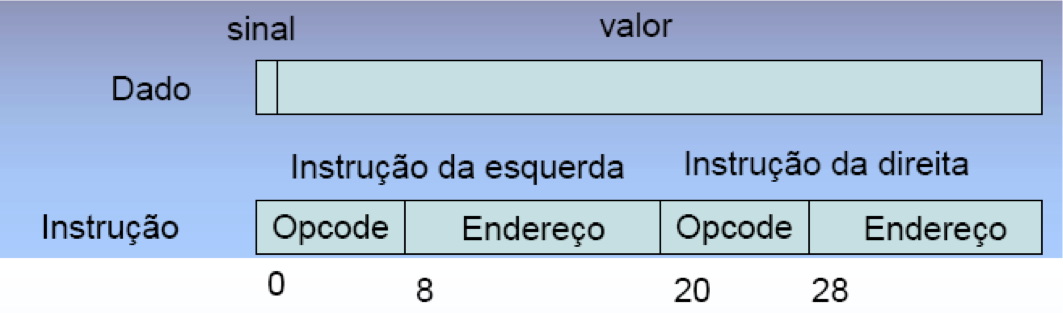

- Entender na prática a organização da memória do IAS e a diferença na representação de instruções e dados.

- Se familiarizar com o simulador acadêmico IAS Sim (rodar o simulador, carregar programa, janela de memória, registradores, etc.)

- Conseguir criar e executar um programa simples em Assembly.

Memória IAS

Exercício: Instruções de Transferência e Aritméticas

- Instruções com Opcode 1 a 12, 17, 20 e 21 do conjunto de instruções

- Faça um programa que execute o seguinte conjunto de instruções:

g = 3;

h = 5;

i = 2;

j = 1;

f = (g+h) – (i+j);

</syntaxhighlight>

- Solução:

S(x)->Ac+ g

S(x)->Ah+ h

S(x)->Ah- i

S(x)->Ah- j

At->S(x) f

halt

g: .data 3

h: .data 5

i: .data 2

j: .data 1

f: .data 0

</syntaxhighlight>

Aula 06/09/2013: IAS Sim (continuação)

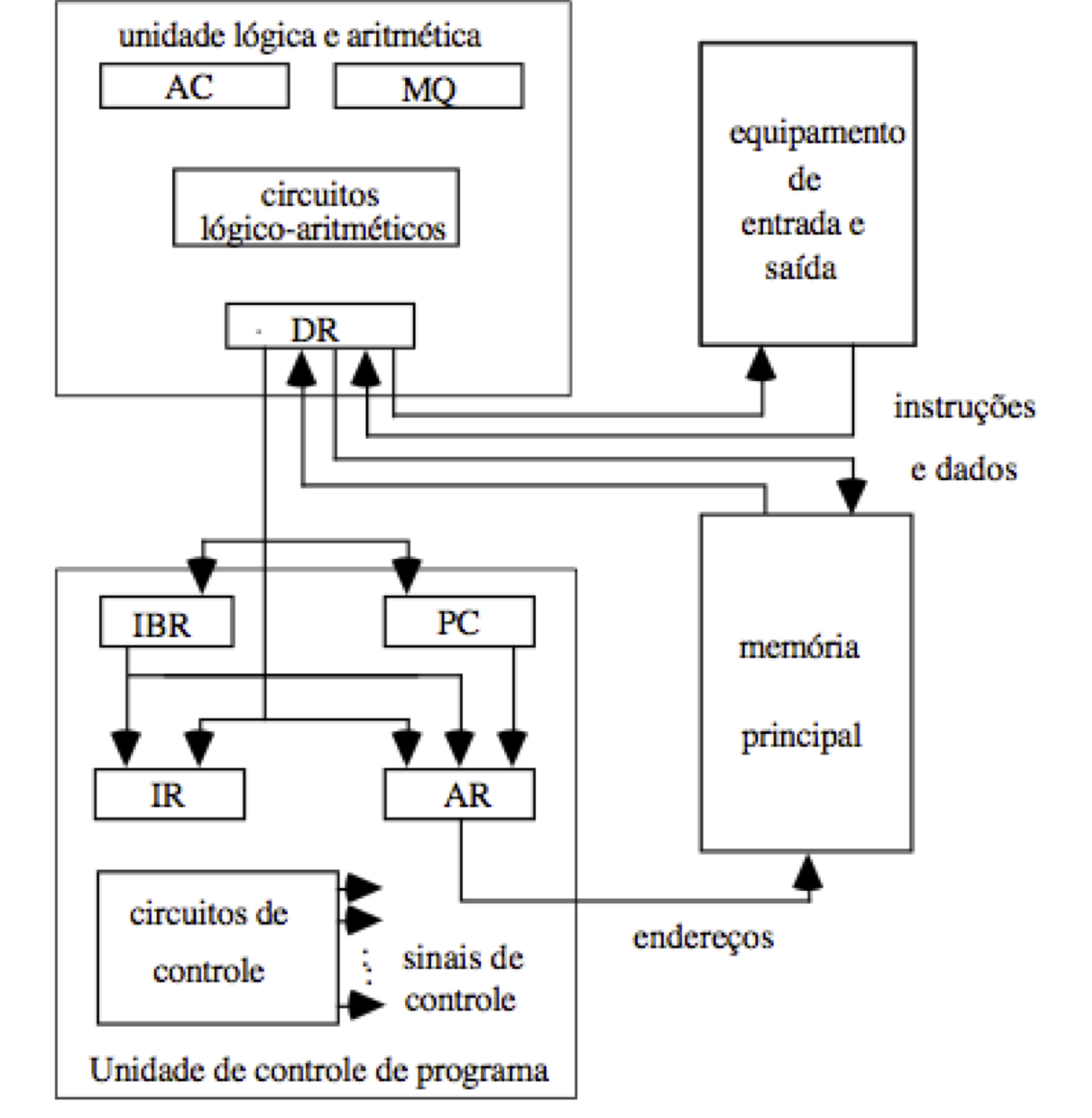

Estrutura do IAS

Registradores IAS Sim

Registradores "Visíveis" ao programador:

- Accumulator (AC)

- Arithmetic Register (AR)

Registradores internos:

- Control Counter (CC): Contador de Programa.

- Control Register (CR): Instrução em execução.

- Function Table Register (FR): Opcode em execução.

- Memory Address Register (MAR): Posição de memória que sofrerá ação do Opcode.

- Selectron Register (SR): O valor lido ou escrito na memória.

Exercício: Instruções de Desvio

- Instruções com Opcode 13 a 16 do conjunto de instruções