Mudanças entre as edições de "MIC-2013-1-CST Introdução aos Microcoprocessadores"

(→AULA 2) |

|||

| Linha 209: | Linha 209: | ||

Registrador de Instrução (IR), atualizando os registros ou dados da memória, | Registrador de Instrução (IR), atualizando os registros ou dados da memória, | ||

dependendo da instrução em questão. | dependendo da instrução em questão. | ||

| + | |||

| + | =AULA 5= | ||

| + | |||

| + | ==Objetivos== | ||

| + | |||

| + | Os alunoss deverão ser capazes de: | ||

| + | |||

| + | *enumerar as principais característcias do microcontrolador 8051; | ||

| + | *desenvolver pequenos programas de movimentação de dados entre registradores,memória de código, memória interna e memória externa; | ||

| + | |||

| + | ==Material de Aula== | ||

| + | |||

| + | [* [http://www.sj.ifsc.edu.br/~eraldo/MIC/2013-1/Arquitetura8051.pdf Plano da disciplina]] | ||

Edição das 07h20min de 6 de maio de 2013

DADOS GERAIS DA DISCIPLINA

- Professor: Eraldo Silveira e Silva (email: eraldo@ifsc.edu.br)

- Plano de Ensino 2013-1

Cronograma

| AULA | DATA | Descriçao |

|---|---|---|

| 1 | 2/4/2013 | |

| 2 | 9/4/2013 |

AULA 1 - Dia 22/04/2013

OBS: aula improvisada pelo fato de ter sido repassada na última sexta.

Objetivos

- apresentar os objetivos da disciplina

- trabalhar memórias na forma de diagrama em blocos

- apresentar barramentos de endereço/dados/controle

- diferenciar conteúdo de endereço de memória;

- apresentar o procedimento de acesso para escrita e para a leitura;

- apresentar um diagrama de tempo simplificado de acesso a memória;

- apresentar a CPU/microcontrolador como a "entidade" que acessa a memória

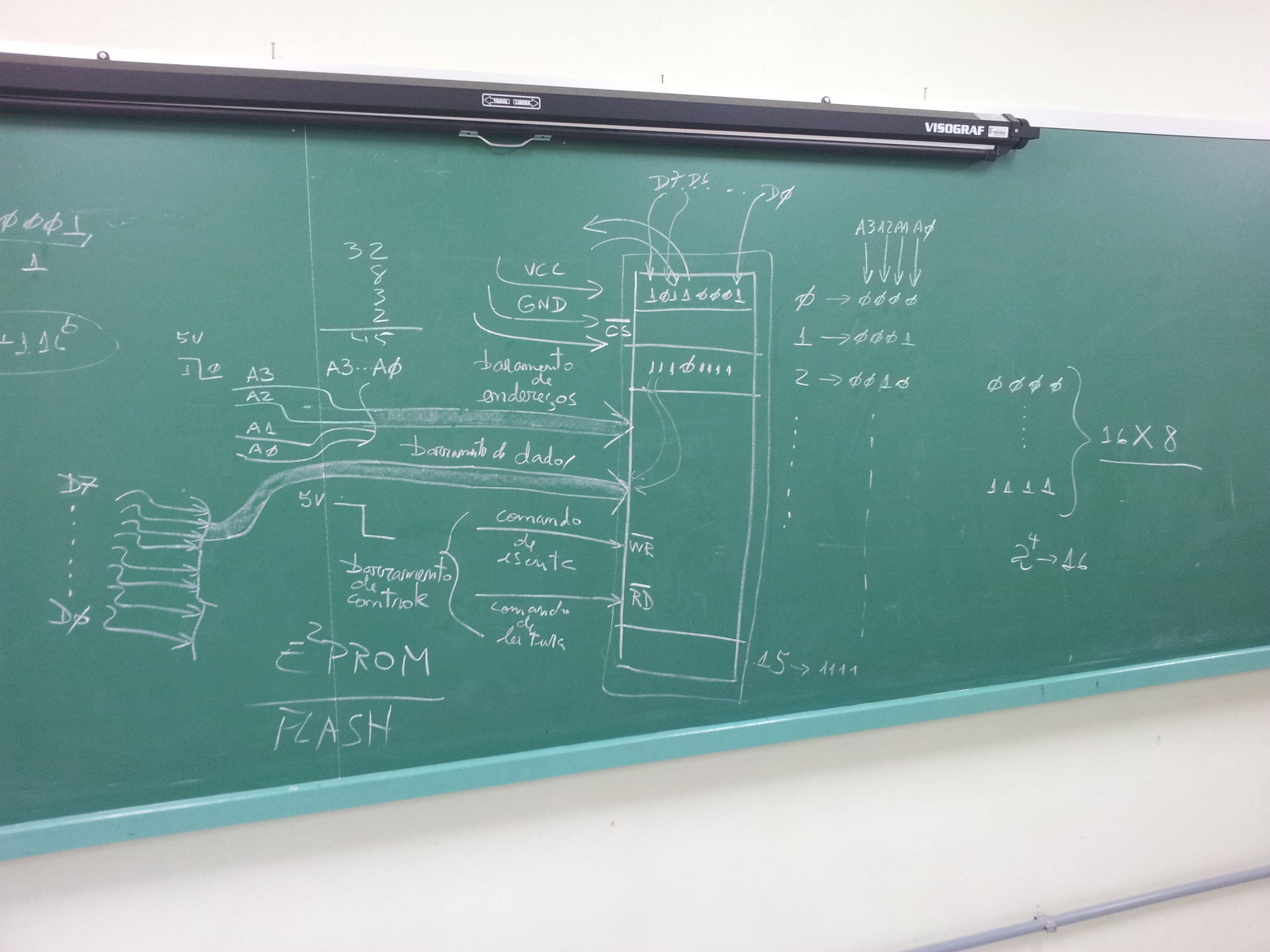

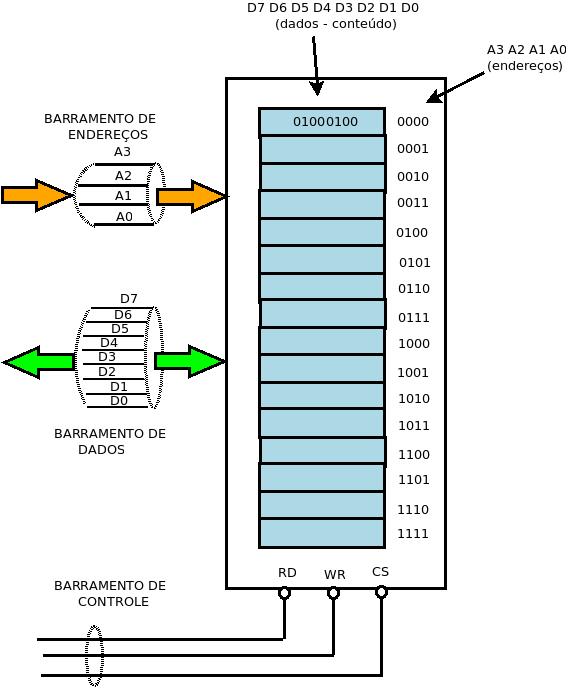

Diagrama em blocos da memória e barramentos

No diagrama abaixo está representado um bloco de memória primária de 16x8 (dezesseis endereços por 8 bits).

- Note que uma posição de memória pode ser vista como uma caixa que possue um endereço e um conteúdo.

- O conteúdo associado a posição de memória é uma palavra binária e, neste caso, possui 8 bits.

ou

Para que us dispositivo externo possa "acessar" a memória para leitura ou escrita, ele deve se utilizar de um conjunto de fios que chamamos de barramentos.

Barramento de Endereços

Este barramento permite determinar o endereço de uma posição a ser acessada na memória. Um barramento de 4 linhas de endereço é designado por A3,A2,A1 e A0.

Supondo uma memória com endereços designados da forma hexadecimal de 0h a Fh. Supondo que A3 seja associado ao bit mais significativo e A0 ao bit menos significativo. Então, para acessar a posição Bh de memória, deve-se injetar A3=1, A2=0, A1=1 e A0=1. Note que

O termo "injetar" significa aqui que um dispositivo externo deve forçar tensão nas linhas do barramento. Esta tensão depende da tecnologia utilizada. Poderia ser, por exemplo, 5V para o nível lógico 1 e 0V par ao nível lógico 0.,

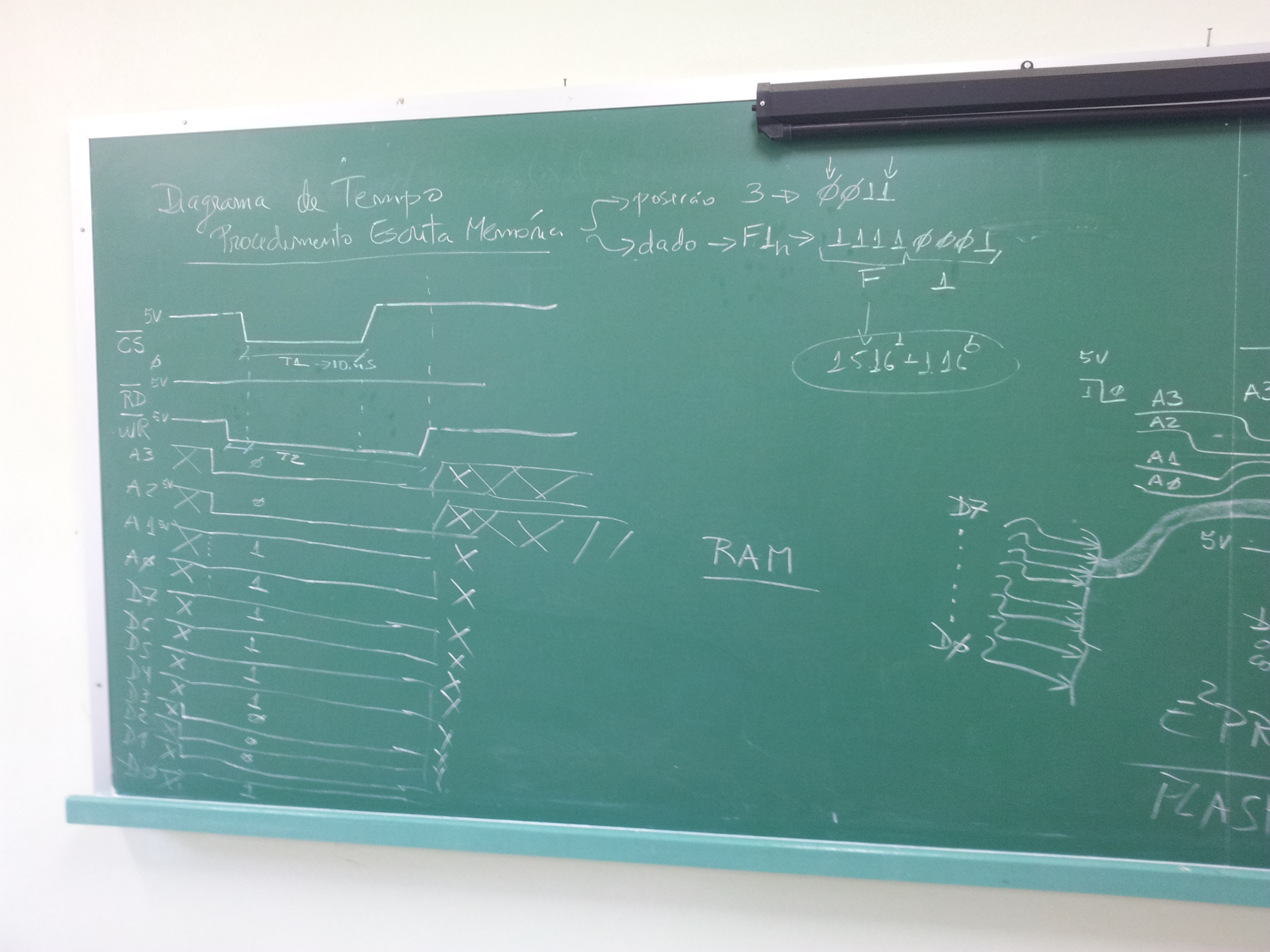

Diagrama de Tempo - Acesso para escrita

AULA 2

Objetivos

- apresentar, através de um exercício, um sistema hipotético de microprocessamento;

- desenvolver a noção do que é a linguagem de máquina e do que é linguagem assembly;

Sistema de microprocessamento hipotético

Seja um sistema hipotético de processamento com os seguintes componentes:

Uma CPU contendo:

- Unidade de Controle;

- Unidade Lógica e Aritmética;

- Registradores:

- Registrador de Instrução (IR) de palavra de 6 bits: Armazena a instrução que será executada pela CPU;

- Contador de Programa (PC) de palavra de 4 bits: Armazena o endereço da próxima instrução a ser executada;

- Registrador A e Registrador B, ambos de 6 bits: Registros temporários para transferência de dados da memória e operações de lógica e aritmética.

- Barramentos:

- Barramento de Dados - 6 bits : D5, D4, D3, D2, D1, D0.

- Barramento de Endereço - 4 bits : A3, A2, A1, A0.

- Barramento de Controle:

- WR - Escrever RAM (memória de dados);

- RD - Ler RAM (memória de dados);

- PSEN - Ler ROM (memória de programa)

- Memória externa de Dados: 16 posições de 6 bits;

- Memória externa de Programa: 16 posições de 6 bits;

\section{Conjunto de Intruções do Sistema Hipotético}

\begin{table}[h] \caption{Conjunto de Intruções} \begin{tabular} {|p{1.5cm}|c|p{10cm}|l|} \hline % Código & tam & Descrição & Mnemônico\\ \hline % 00\small{XXXX} & 1 & Ler endereço \small{XXXX} da memória de dados para acumulador A. & MOV A,direto \\ 01\small{XXXX} & 1 & Escrever no endereço \small{XXXX} da memória de dados o valor do acumulador A. & MOV direto,A \\ 100000 & 1 & Somar acumulador A com registrador B e colocar resultado em A. & ADD A,B \\ 100001 & 1 & Decrementar acumulador A. & DEC A \\ 100010 & 1 & Mover o conteúdo do acumulador A para o registrador B. & MOV B,A \\ 100011 & 1 & Subtrair o valor do registrador B do acumulador A e colocar resultado em A & SUBB A,B \\ 100100 & 1 & Parar o microprocessador & HALT \\ 100101 \small{YYYYYY} & 2 & Mover o dado imediato \small{YYYYYY} (armazenado na memória de programa) para o acumulador A & MOV A,\#dado6 \\ 11\small{XXXX} & 1 & Saltar (JUMP) para o endereço \small{XXXX} da memória de programa se acumulador A for diferente de 0. & JNZ direto \\ \hline % \end{tabular} \end{table}

\section{Executando um programa}

Considere a memoria de programa com o seguinte código:

\begin{table}[h] \caption{Conteúdo da Memória de Programa} \begin{tabular} {|c|c|p{8cm}|l|} \hline % Endereço & Conteúdo & Descrição & Mnemônico\\ \hline % 0H & 000001 & Movimenta conteúdo lido da posição 0001 da memória de dados para o registrador A & MOV A,1H \\ 1H & 100010 & Move o conteúdo do registrador A para o registrador B & MOV B,A \\ 2H & 000010 & Movimenta conteúdo lido da posição 0010 da memória de dados para o registrador A & MOV A,2H \\ 3H & 100011 & Subtrair o valor do registrador B do acumulador A e colocar resultado em A. & SUBB A,B \\ 4H &110011 & Saltar (JUMP) para o endereço 0011 da memória de programa se acumulador A for diferente de 0. & JNZ 3H\\ 5H & 010000 & Escrever no endereço 0000 da memória de dados o valor do acumulador A. & MOV 0H,A\\ 6H & 100100 & Parar o microprocessador & HALT \\ \hline % \end{tabular} \end{table}

Preencha a taebela conforme a execução do programa:

\begin{table}[h] \caption{Conteúdo dos principais registros a cada passo do programa exemplo} \begin{tabular} {|c|c|c|c|c|c|c|c|c|} \hline % passo & IR & A & B & PC & RAM 0000 & RAM 0001 & RAM 0010 & RAM 0011\\ \hline % 0 & 000000 & 000000 & 000000 & 0000 & 000111 & 000001 & 000011 & 000010\\ \hline % 1&&&&&&&&\\ \hline % 2&&&&&&&&\\ \hline % 3&&&&&&&&\\ \hline % 4&&&&&&&&\\ \hline % 5&&&&&&&&\\ \hline % 6&&&&&&&&\\ \hline % 7&&&&&&&&\\ \hline % 8&&&&&&&&\\ \hline % 9&&&&&&&&\\ \hline % 10&&&&&&&&\\ \hline % 11&&&&&&&&\\ \hline % 12&&&&&&&&\\ \hline %

As condições de ``reset do sistem são as seguintes: Registros A, B, PC e IR são zerados.

A CPU executará eternamente a sequência:\textbf{ ciclo de busca} e \textbf{ciclo de execução de instrução}. O ciclo de busca consiste basicamente em: \begin{enumerate}

\item Colocar o endereço do PC no Barramento de Endereços;

\item Enviar o controle de leitura $\overline{PSEN}$ para Memória de Programa;

\item Ler a instrução do Barramento de Dados através da aplicação de

um comando de escrita no Registrador de Instrução (IR);

\item Incrementar o PC em função do número de palavras da instrução.

\end{enumerate}

O ciclo de execução é basicamente a decoficação da instrução que está no Registrador de Instrução (IR), atualizando os registros ou dados da memória, dependendo da instrução em questão.

AULA 5

Objetivos

Os alunoss deverão ser capazes de:

- enumerar as principais característcias do microcontrolador 8051;

- desenvolver pequenos programas de movimentação de dados entre registradores,memória de código, memória interna e memória externa;