MI1022806 2021 2 AULA09

Memória Interna

Embora o conceito de memória seja relativamente simples, é talvez o componente que apresenta maior variedade de tipos, tecnologias, organizações, desempenhos e custos.

Isto porque nenhuma das tecnologias de memória existentes satisfaz de maneira ótima todos os requisitos de armazenamento de dados em computadores.

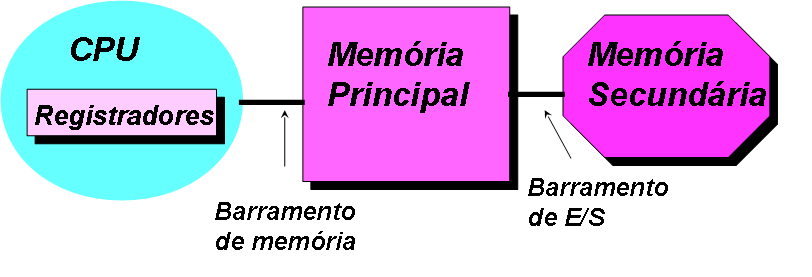

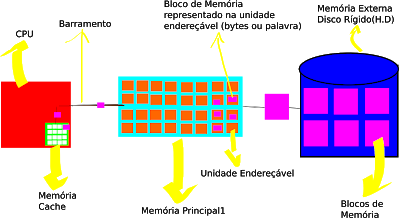

Assim, um sistema de computador típico é equipado com uma hierarquia de subsistemas de memória, algumas internas (diretamente acessíveis pelo processador), e outras externas (acessíveis ao processador por meio de um módulo de E/S).

Figura 1 - Sistema típico de computador com destaque para as memórias.

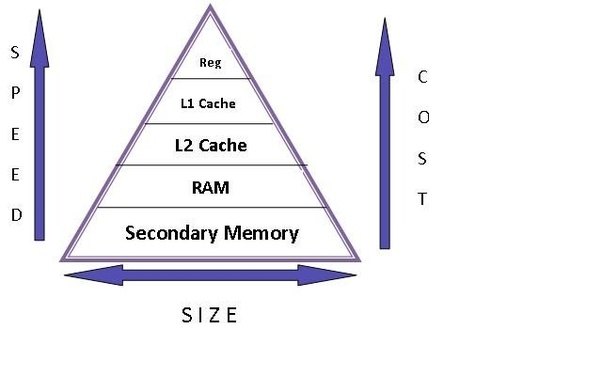

Figura 2 - Relação custo vs. velocidade vs. tamanho por tipos de memórias.

A chave para o sucesso desta organização hierárquica está na diminuição da frequência de acessos.

Esse conceito será melhor detalhado na seção sobre memória cache.

Exemplo:

Considere um processador com acesso a dois níveis de memória cache.

O nível 1, o qual é acessado diretamente pelo processador, contém mil palavras e o tempo de acesso é de 0,1 µs.

Já o nível 2 contém 100 mil palavras e o tempo de acesso é de 1 µs. Caso a palavra requerida esteja no nível 2, ela tem que ser primeiramente transferida para o nível 1, para depois ser acessada pelo processador.

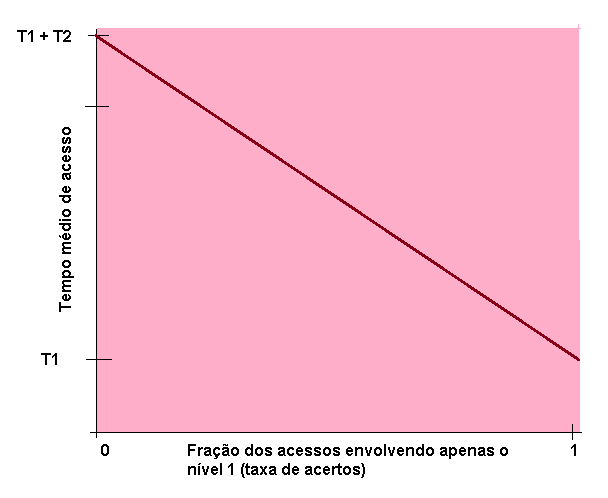

A Figura 3 ilustra a forma geral da curva que corresponde a essa situação.

Figura 3 - Desempenho de uma memória simples com dois níveis.

onde:

- H é definido como a fração de acessos à memória, em que a palavra requerida é encontrada na memória cache;

- T1 é o tempo de acesso ao nível 1 e,

- T2 é o tempo de acesso ao nível 2.

Como se pode observar, se a taxa de acessos ao nível 1 for alta, então o tempo total de acesso médio é muito mais próximo do tempo de acesso ao nível 1, do que do tempo de acesso ao nível 2.

Suponha, por exemplo, que em 95% dos acessos à memória a palavra requerida seja encontrada na memória cache de nível 1. Então, o tempo médio para acessar uma palavra pode ser expresso como:

⇒ (0,95).(0,1 µs) + (0,05).(0,1 µs + 1 µs) = ⇒ 0,095 + 0,055 = 0,15 µs

Essa estratégia só funciona se as seguintes condições forem válidas, à medida que descemos na hierarquia de memórias:

- O custo por bit diminui;

- A frequência de acesso à memória pelo processador diminui.

O que acontece, de fato, pelo uso de diferentes tecnologias de fabricação de memórias.

A base para a validade da segunda condição está no princípio conhecido como localidade de referências:

Ao longo da execução de um programa, as referências feitas à memória pelo processador, tanto no caso de instruções quanto de dados, tendem a formar grupos, nos quais elas estão próximas umas das outras.

Um programa típico contém certo número de laços iterativos e sub-rotinas. Dentro destes laços ou funções, ocorrem repetidas referências a um pequeno conjunto de instruções.

Da mesma maneira, operações sobre tabelas e vetores envolvem acessos a um conjunto de palavras que estão próximas umas das outras, na memória.

Assim, é possível organizar os dados ao longo da hierarquia de memória, de modo que a porcentagem de acessos de certo nível seja sucessivamente bem menor do que a porcentagem de acessos ao nível imediatamente superior.

Por exemplo, no exemplo anterior, suponha que a memória de nível 2 contenha todos os dados e instruções do programa. Neste caso, os conjuntos de dados mais utilizados em cada instante podem ser, temporariamente, armazenados no nível 1.

De tempos em tempos, alguns destes conjuntos de dados têm que ser removidos de volta ao nível 2, para dar espaço a um novo conjunto de dados no nível 1.

Entretanto, em média, a maioria das referências vai ser feita a instruções e dados localizados no nível 1.

Esta aula enfatiza as memórias internas, enquanto as memórias externas serão tratadas no próximo conteúdo.

A primeira seção aborda as características fundamentais dos sistemas de memória dos computadores.

As seções seguintes examinam os subsistemas de memória principal de semicondutor, incluindo memórias ROM, DRAM e SRAM.

Em seguida, um elemento essencial dos sistemas de computação modernos será discutido: a memória cache.

Os sistemas de memória podem ser mais facilmente compreendidos por meio de sua classificação.

As características mais importantes que são relacionadas abaixo:

Localização da memória

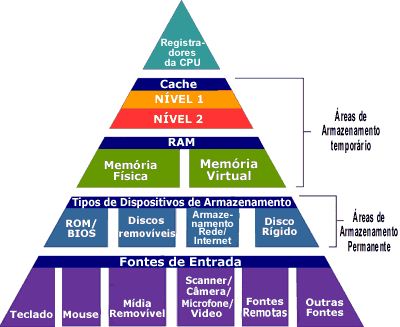

Como já foi discutido, a memória de um computador é organizada de maneira hierárquica, em função da velocidade, tamanho e "proximidade" com o processador da mesma.

Memória interna

O nível superior (mais próximo do processador) é constituído de registradores do processador.

Em seguida, vem um ou dois níveis de memória cache, designados como caches L1 e L2.

Figura 4 - Destaque para as áreas de armanzenamento temporário e permanente.

Depois, vem a memória principal, que normalmente usa módulos de memória dinâmica de acesso aleatório (dynamic random-acess memory - DRAM).

Essas memórias são consideradas as memória internas ao sistema de computação.

Memória externa

A hierarquia continua com a memória externa, na qual os níveis seguintes são, tipicamente, compostos por disco rígido, pen-drives, etc e que serão vistos na próxima aula.

Capacidade

A característica mais óbvia de uma memória é sua capacidade, que normalmente é expressa em bytes (1 byte = 8 bits) ou palavras.

A capacidade de uma memória é medida também em:

- kilobyte - 1 kB = 1024 ou 2^10 Bytes,

- Megabyte - 1 MB = 1024 kB ou 2^20 Bytes,

- Gigabyte - 1 GB = 1024 MB ou 2^30 Bytes e

- Terabyte - 1 TB = 1024GB ou 2^40 Bytes.

Nota: Segundo o sistema internacional a unidade, a letra "k" de kilobyte ou kilobits deve ser sempre escrita com letra minúscula, enquanto "kB" ou "kb" são respectivamente kilobytes (maiúsculo) kilobits (minúsculo).

As principais definições são:

- Palavra - unidade natural de organização de memória. O tamanho de uma palavra é tipicamente igual ao número de bits usado para representar um número inteiro e ao tamanho de uma instrução. Os tamanhos mais usuais de cada palavra são 8, 16, 32 e 64 bits.

- Unidade endereçável - na maioria dos sistemas, é a própria palavra. Entretanto, alguns sistemas permitem o endereçamento individual de bits, ou bytes.

- Unidade de transferência - representa o número de bits de dados da memória principal que podem ser lidos ou escritos, de uma só vez.

Unidade de transferência

Unidade de transferência de dados corresponde ao nº de bits que podem ser lidos ou escritos de cada vez.

- Memória interna: a unidade de transferência é governada pela largura do barramento de dados.

- Normalmente o nº de linhas de dados = tamanho da palavra.

- Internamente, o endereçamento é feito por palavras.

- Memória externa: a unidade de transferência é feita por blocos de dados.

- Um bloco é muito maior que uma palavra (bloco >> palavra).

- Em unidades de disco, o bloco é a unidade de endereçamento dos dados (clusters).

Igual ao número de linhas elétricas que saem, ou entram no módulo de memória.

Figura 5 - Bloco de memória endereçável.

Método de acesso

O método de acesso aos dados pode ser: Acesso sequencial, Acesso direto, Acesso aleatório e Associativo.

Acesso sequencial

Os dados são organizados na memória em unidades chamadas registros. O acesso é feito segundo uma sequencia linear específica.

Além dos dados, são armazenadas informações de endereçamento, utilizadas para separar um registro do registro seguinte, e facilitar o processo de busca por um determinado registro.

Um mecanismo compartilhado é usado para leitura e escrita; a cada operação ele é movido de sua posição atual para a desejada, ignorando registros intermediários. Portanto, o tempo de acesso a um registro arbitrário varia muito.

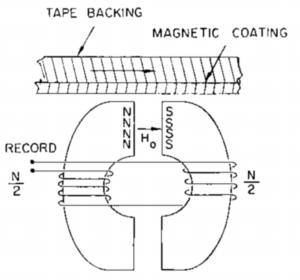

Figura 6 - Exemplo do mecanismo de leitura das Unidades de fita magnética.

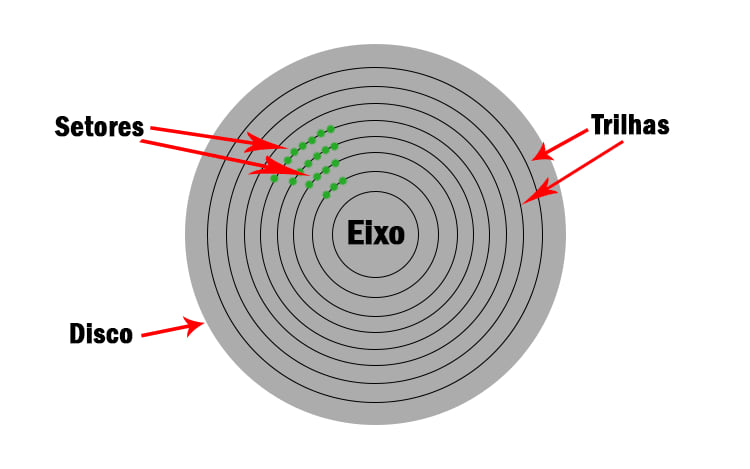

Acesso direto

O acesso é feito por um salto até um bloco de registros, seguido por uma pesquisa seqüencial até o registro (posição) desejado.

Assim como com o acesso sequencial, o acesso direto emprega um mecanismo compartilhado para leitura e escrita.

Entretanto, cada bloco individual ou registro possui um endereço único, baseado em sua localização física. O acesso é feito por meio de um acesso direto a uma vizinhança genérica do registro e, em seguida, por uma pesquisa sequencial, por contagem ou espera, até atingir a posição final.

O tempo de acesso também é variável.

Figura 7 - Divisão de um disco magnético (disquete) com seus setores e trilhas.

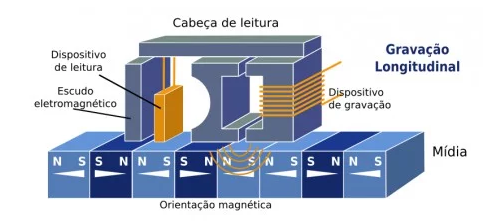

Figura 8 - Cabeça de leitura e gravação de unidades de disco.

Acesso aleatório

Esse tipo de acesso é feito diretamente ao registro através de seu endereço.

- Endereços individuais indicam a localização exata.

- Mecanismo independente para leitura e escrita.

- Tempo de acesso constante, independente da localização e dos acessos anteriores.

Cada posição de memória endereçável possui um mecanismo de endereçamento único e fisicamente conectado a ela.

O tempo de acesso a uma determinada posição é constante e independente da sequencia de acessos anteriores.

Desta maneira, qualquer posição pode ser selecionada de modo aleatório, sendo endereçada e acessada diretamente.

Figura 9 - A memória principal, assim como alguns sistemas cache, são dispositivos de acesso aleatório

Figura 10 - Quadro de uma célula de memória.

Figura 11 - Integração de chip de memória RAM.

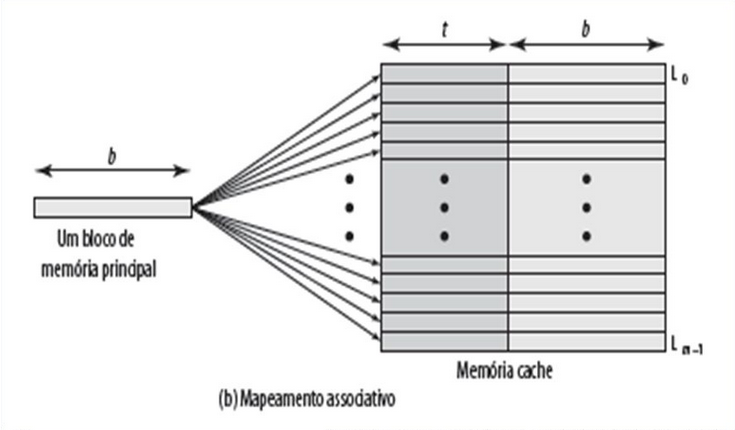

Associativo

O acesso é feito diretamente ao registro com base em parte de seu conteúdo.

- Mecanismo de endereçamento próprio, baseado na comparação simultânea de alguns bits da palavra com todas as palavras da memória (identificação por padrão de bits).

- Tempo de acesso constante.

Consiste em um tipo de memória de acesso aleatório que possibilita comparar simultaneamente um certo número de bits de uma palavra com todas as palavras da memória, determinando quais dessas palavras contêm o mesmo padrão de bits.

Uma palavra é buscada na memória com base em uma parte do seu conteúdo, e não de acordo com seu endereço.

Assim como na memória de acesso aleatório, cada posição de memória possui seu mecanismo de endereçamento próprio e o tempo de busca é constante e independente da posição ou do padrão dos acessos anteriores.

Figura 12 - Mapeamento associativo da memória cache para a memória principal.

Exemplo: As memórias cache podem empregar mecanismo de acesso associativo.

Desempenho

Do ponto de vista do usuário, as duas características mais importantes da memória são sua capacidade e seu desempenho.

Os parâmetros utilizados para medir o desempenho são: Tempo de acesso, Tempo de ciclo de memória e Taxa de transferência.

Tempo de acesso

É o tempo necessário para localizar, ler ou escrever um dado na memória.

Em uma memória de acesso aleatório, tempo gasto desde a apresentação do endereço, até o armazenamento ou a disponibilização do dado (operação L/E).

Em uma memória de acesso não-aleatório, o tempo de acesso é o tempo gasto para posicionar o mecanismo de leitura-escrita na posição desejada.

Tempo de ciclo de memória

É o tempo de acesso mais o tempo adicional requerido pela memória antes de iniciar o próximo acesso.

Esse conceito é aplicável principalmente a memórias de acesso aleatório e compreende o tempo de acesso e o tempo adicional requerido, antes que um segundo acesso possa ser iniciado.

Ainda, esse tempo adicional pode ser necessário para o desaparecimento de transientes nas linhas de sinais ou para a regeneração dos dados.

Taxa de transferência

É a taxa pela qual os dados podem ser transferidos "de" ou para a unidade de memória.

Na memória de acesso aleatório, é equivalente à frequência, em Hz, do relógio de sistema:

, onde TC é a duração de um ciclo de memória.

Para uma memória de acesso não-aleatório, é válida a seguinte relação:

onde:

TN é o tempo médio de L/E de N bits, e TA é o tempo médio de acesso.

Tecnologias

Diversas tecnologias têm sido empregadas para a fabricação de memórias de computadores. As mais comuns atualmente são as memórias de semicondutor, as memórias de superfície magnética, as memórias óticas e as magneto-óticas.

As principais tecnologias de implantação de memórias em uso corrente são:

- Portas lógicas e flip-flops, usados na implementação da memória cache.

- Transistores, capacitores e circuitos de refresh, usados na implementação da memória principal.

- Arranjos de conexões, utilizados na implementação de certas ROMs (memórias de leitura).

- Fitas magnéticas, utilizadas principalmente para cópias de segurança e arquivamento a longo prazo.

- Discos magnéticos, como discos rígidos e disquetes - a principal tecnologia de implementação de memória secundária.

- Discos ópticos, como CDs e DVDs, e suas diversas variações.

- Memória flash, um tipo de memória semicondutora não volátil, muito usada em câmeras digitais e leitores de MP3.

Memórias magnéticas

Memórias magnéticas tem um papel de destaque no mundo da tecnologia. Dentre as diversas tecnologias de memórias e armazenamento, o uso de um meio magnético sempre foi um conceito importante. Além dos HDs, outras mídias que se baseiam em armazenamento magnético são os Floppy Discs e as fitas K7 e VHS, todos já em desuso. A grande vantagem das memórias magnéticas é, além de serem não-voláteis, o seu preço, bem menor do que outras tecnologias de armazenamento. A principal desvantagem é a velocidade, bem menor do que memórias RAM, por exemplo.

O princípio de funcionamento das memórias magnéticas é relativamente simples. Consiste em utilizar um meio magnetizável, no qual diferentes micro-regiões possam ser polarizadas de forma diferente. Assim, cada bit 0 ou 1 é representado por uma orientação magnética diferente. O processo de escrita basicamente consiste na polarização dessas regiões, de acordo com o padrão de 0s e 1s a serem armazenados.

A leitura, grosso modo, é a operação de detectar a orientação magnética de cada setor, para determinar cada bit de informação. Em geral, uma cabeça de leitura-escrita é usada para fazer essas operações ao mover-se pela superfície do material magnético.

Diferentes tecnologias e dispositivos variam em como a cabeça de leitura percorre a superfície da mídia e como as regiões são organizadas, mas o princípio é o mesmo.

A maioria dos discos rígidos encontrados no mercado hoje utiliza um tipo de tecnologia de gravação chamada longitudinal, que falaremos na próxima aula, onde os bits são gravados na superfície magnética lado a lado. Este tipo de tecnologia de gravação vem sendo utilizado desde o lançamento dos primeiros discos rígidos. No entanto, um novo tipo de tecnologia de gravação, chamada perpendicular, vem sendo utilizada pelos discos rígidos mais novos e que permite uma maior densidade de gravação de dados do que a tecnologia longitudinal.

Existem também novas tecnologias de mídia magnética que estão sendo pesquisadas e que têm potencial para se tornar a base para novos dispositivos de memória magnética.

Figura 13 - Disco rígido (HD) com capacidade de 500GB.

Memórias de semicondutor

Nos primeiros computadores, a tecnologia mais comumente utilizada na fabricação da memória principal de acesso aleatório empregava um grupo de anéis de material ferromagnético, conhecidos como núcleos.

Desde seu aparecimento, as memórias baseadas na microeletrônica superaram de longe as memórias de núcleo magnético.

Atualmente, o uso de pastilhas de semicondutores para a memória principal é quase universal.

| Tipo de Memória | Categoria | Apagamento | Escrita | Volatilidade |

|---|---|---|---|---|

| Random Access Memorie (RAM) | Read/Write | Elétrico (byte a byte) | Elétrica | Volátil |

| Read-Only Memorie (ROM) | Read | Impossível | Máscara | Não volátil |

| Programmable ROM (PROM) | One-Time Programmable | Elétrica | ||

| Erasable PROM (EPROM) | Read-mostly | Ultra-violeta | ||

| Electrically EPROM (EEPROM) | Elétrico (byte a byte) | |||

| Flash EPROM | Elétrico por bloco |

Características físicas

Persistência

É a capacidade de manter a informação armazenada na ausência de energia.

As memórias voláteis são aquelas que, ao interromper a alimentação, perdem as informações armazenadas.

Exemplo: memórias RAM.

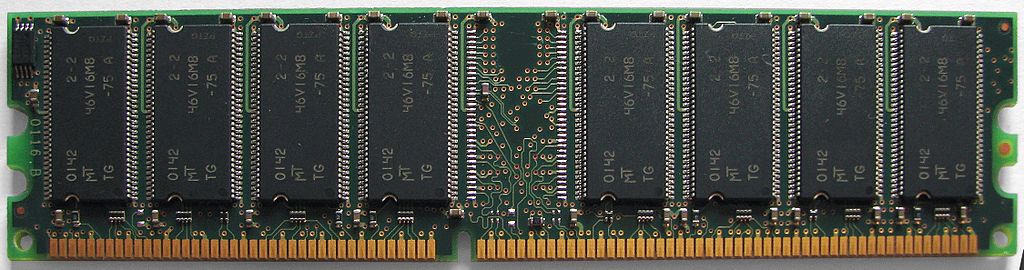

Figura 14 - O chamado "pente" de memória RAM para PC.

As memórias não voláteis são aquelas que, mesmo sem alimentação, continuam com as

informações armazenadas.

Exemplo: memórias ROM, PROM, EPROM.

Figura 15 - EPROM também conhecidas como UVPROM (ultravioleta PROM).

Alterabilidade

É a capacidade de modificar o conteúdo.

- Memórias somente de leitura: não permitem gravação, só leitura.

- Ex: memórias ROM e PROM.

- Memórias principalmente de leitura: permitem gravações, mas sua principal utilização é a leitura.

- Ex: memórias EPROM, EEPROM e flash.

- Memórias de leitura e gravação: permitem operações de leitura e escrita rápidas e fáceis.

- Ex: memórias RAM (cache e principal) e memórias secundárias

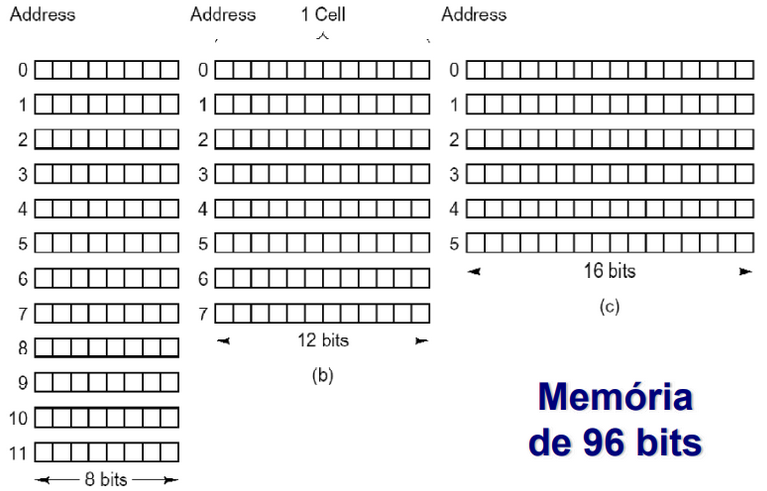

Organização

A memória do computador é dividida em células.

- Todas as células possuem o mesmo nº de bits.

- Células de k bits → armazenam 2^k valores diferentes.

- Uma célula é a menor unidade endereçável da memória, ou seja, menor localização unicamente endereçada.

Palavra é a unidade natural de organização da memória.

- Grande parte das instruções efetuam operações com palavras.

- A comunicação com a CPU é feita por palavras.

- Tamanhos usuais: 8, 16, 32 e 64 bits.

- Ex: computador de 32 bits

→ 4 bytes/palavra.

Organização: arranjo físico dos bits para formar palavras.

Figura 16 - Exemplo de arranjos de memória.

Forma de saída

As saídas das memórias podem ser de três tipos: totem-pole, open collector ou threestate.

As memórias three-state são as mais usadas por permitirem a criação de bancos de memória, de forma mais eficiente.

Saída totem-pole

Possui em sua estrutura interna um transistor conectado ao +Vcc, permitindo alimentar cargas capacitivas. Os transistores de saída estabelecem uma impedância baixa na saída, possibilitando um rápido chaveamento dos níveis lógicos.

Saída open collector (coletor aberto)

Não possui um resistor ligando o coletor de saída do transistor ao +Vcc, devendo ser ligado externamente (resistor pull-up). Esta saída possibilita o controle externo da corrente do coletor de saída, possibilitando o aumento do fan-out, além de poder habilitar saídas diferentes interligadas entre si, podendo assumir níveis lógicos opostos sem danos. A desvantagem é sua baixa velocidade de chaveamento dos níveis lógicos.

Saída three-state

Configuração que apresenta uma alta impedância de saída (terceiro estado), em relação à linha na qual está conectada. Funciona como se o dispositivo estivesse desligado. Assim, permite interligar várias saídas em uma mesma linha de dados, fornecendo nível lógico alto ou baixo, sem danificar outros circuitos

Memória RAM

O termo Random-Access Memory, ou RAM, ou Memória de Acesso Aleatório em português, veio porque essa tecnologia substituiu as anteriores memórias de Acesso Sequencial.

Hoje, o termo Memória RAM é utilizado de forma errada para representar a Memória Principal, mas na verdade, tanto registradores, quanto memória Cache e Memória Principal são feitos utilizando tecnologia RAM.

Assim, RAM é uma tecnologia e não uma memória. O termo correto, então, é dizer Memória Principal quando se referir à principal memória dos computadores.

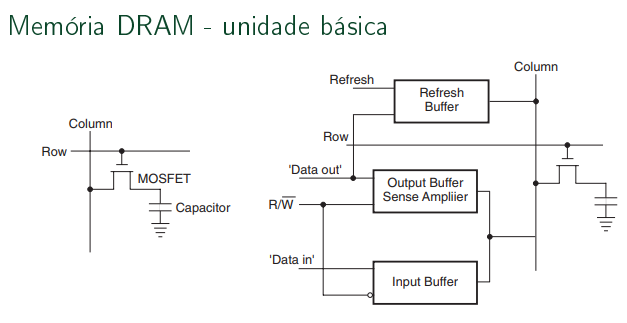

Dynamic RAM (DRAM)

As memórias Dynamic RAM são as mais simples de serem fabricadas.

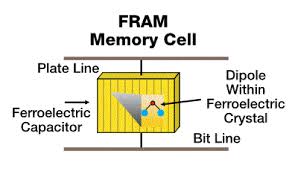

Como mostrado na Figura abaixo, “Estrutura de uma DRAM para armazenar um Bit”, é formada simplesmente por um único transistor e um capacitor.

Figura 17 - Estrutura de uma DRAM para armazenar um Bit.

A figura apresenta uma memória de um único bit. O transistor é responsável por abrir ou fechar a passagem de corrente para linha B.

Já a linha de endereço é utilizada para fechar a porta do transistor e carregar o capacitor.

Se o capacitor estiver carregado, é considerado que a memória contém o bit 1. Caso contrário, a memória contém o bit 0.

A simplicidade desta implementação traz resultado no seu principal ponto negativo. Assim como todo capacitor, o capacitor responsável por manter a carga da memória só é capaz de manter a carga por um curto tempo.

Aos poucos, a carga vai sendo dissipada, até o momento em que era o bit 1, se torna 0, gerando um erro.

Para evitar isso, é adicionado um circuito a parte que de lê o conteúdo da memória periodicamente e recarrega todos capacitores que estão com bit 1 - circuito de refresh.

Vamos lembrar que as memórias hoje estão na casa de Giga Bytes. Ou seja, bilhões de bytes.

Então, bilhões de capacitores devem ser lidos e recarregados periodicamente para que os conteúdos não sejam perdidos.

Esta técnica é chamada de Refrescagem. Ela resolve o problema dos dados perdidos, mas atrapalha bastante o desempenho da memória.

Sempre que a Refrescagem precisa ser realizada, todo acesso é bloqueado. Nada pode ser lido ou escrito enquanto isso. Assim, o processador precisa esperar que o processo de refrescagem termine para poder acessar novamente a memória.

Devido à sua simplicidade de fabricação, as memórias DRAM são mais utilizadas para compor a Memória Principal, devido ao preço mais acessível do que o das mais modernas SRAM.

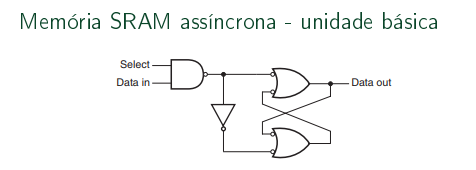

Static RAM (SRAM)

As memórias RAM Estáticas (Static RAM ou SRAM) se baseiam na composição de transistores para possibilitar que a carga do bit 1 seja compartilhada entre outros transistores.

A Figura 18 mostra a “estrutura de uma SRAM básica” e apresenta essa composição de portas lógicas.

Figura 18 - Estrutura de uma SRAM básica.

Nesta ilustração, pode-se observar dois gates básicos formando um flip-flop do tipo D.

As memórias SRAM não precisam de circuito de refrescagem, por isso, não precisam parar e tornam-se muito mais rápidas do que as DRAM. O problema é que elas precisam de muito mais transistores por bit, o que torna o projeto maior e, por consequência, mais caro.

Devido ao seu preço, elas são mais utilizadas em memórias Cache, mas em menor quantidade do que as memórias principais.

Synchronous Dynamic RAM (SDRAM)

Já a Synchronous Dynamic RAM (SDRAM) é uma DRAM com um pequeno avanço.

O relógio que determina o tempo das SDRAM vem diretamente do processador, e não de um relógio próprio, como nas DRAM convencionais.

Isso faz com que o momento exato da Refrescagem seja determinado pelo processador.

Dessa forma, o processador sabe exatamente quando ele não pode acessar a memória, e dedica seu tempo às outras tarefas, ou seja, o processador não perde mais tanto tempo esperando a memória.

Os pentes de memória SDR são usados em micros antigos: Pentium II e Pentium III e os primeiros Athlons e Durons soquete A. Por não serem mais fabricados, eles são atualmente muito mais raros e caros que os DDR, algo semelhante ao que aconteceu com os antigos pentes de 72 vias, usados na época do Pentium 1.

Figura 19 - Pentes de memória SDR utilizados nos Pentium II e Pentium III e nos primeiros Athlons e Durons soquete A.

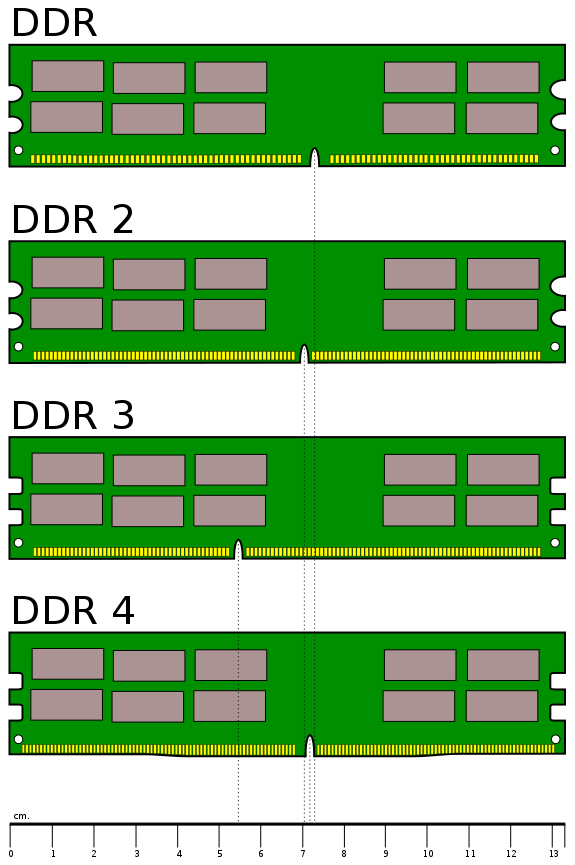

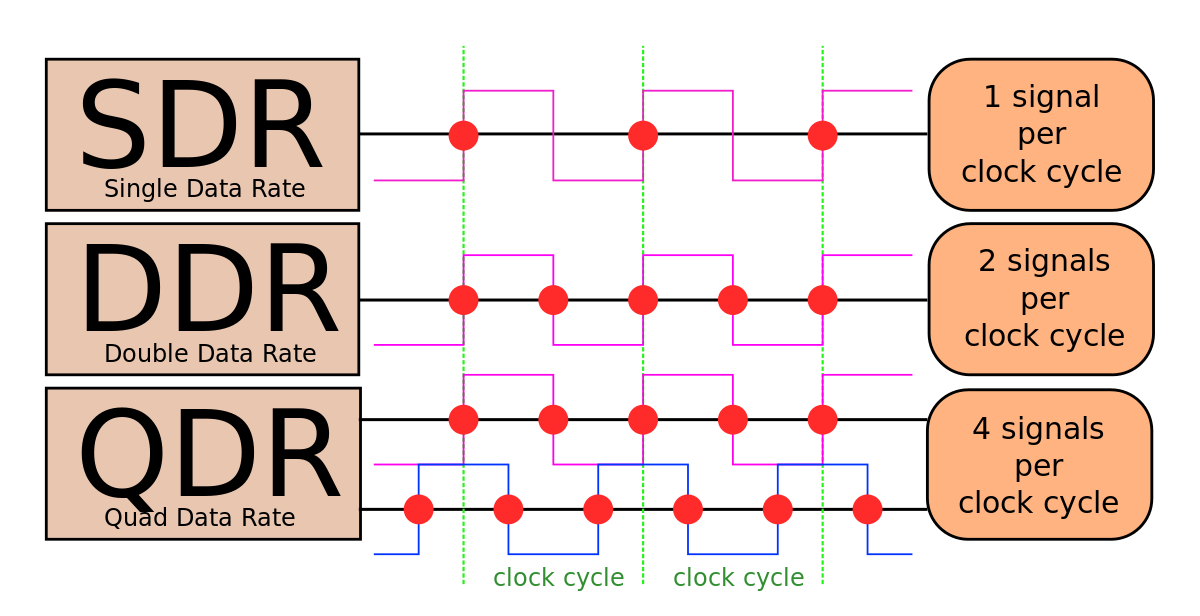

Double-Data Rate SDRAM (DDR-DRAM)

Após as SDRAM surgiram as DDR-SDRAM.

As memórias DDR são síncronas como as SDRAM, mas elas possuem um barramento extra que faz com que, a cada ciclo de clock da memória, o dobro de dados são transferidos.

Na verdade, o mecanismo funciona da seguinte maneira: um acesso à memória é feito na subida do clock do processador e outro, na descida.

As memórias DDR e suas sucessoras são mais utilizadas para utilização como memória principal.

É fácil diferenciar os pentes SDR e DDR, pois os SDR possuem dois chanfros e os DDR apenas um. Essa diferença faz com que também não seja possível trocar as bolas, encaixando por engano um pente DDR numa placa-mãe que use SDR e vice-versa.

Figura 20 - Diferença física entre os pentes de memória: DDR, DDR 2, DDR3 e DDR4.

Mais recentemente, tem acontecido a uma nova migração, com a introdução dos pentes de memória DDR2.

Neles, o barramento de acesso à memória trabalha ao dobro da frequência dos chips de memória propriamente ditos.

Isso permite que sejam realizadas duas operações de leitura por ciclo, acessando dois endereços diferentes.

Como a capacidade de realizar duas transferências por ciclo introduzida nas memórias DDR foi preservada, as memórias DDR2 são capazes de realizar um total de 4 operações de leitura por ciclo, uma marca impressionante.

Existem ainda alguns ganhos secundários, como o menor consumo elétrico, útil em notebooks.

Os pentes de memória DDR2 são incompatíveis com as placas-mãe antigas.

Eles possuem um número maior de contatos (um total de 240, contra 184 dos pentes DDR), e o chanfro central é posicionado de forma diferente, de forma que não seja possível instalá-los nas placas antigas por engano. Muitos pentes são vendidos com um dissipador metálico, que ajuda na dissipação do calor e permite que os módulos operem a frequências mais altas.

Figura 21 - Sinais transmitidos por ciclo de clock nas diferentes tecnologias de memórias.

Registradores

Pequenas unidades de memória com alta velocidade.

Material semicondutor (circuitos Flip-Flop D)

- É a memória + rápida, menor e + cara (custo/bit).

- Tempo de acesso < 1 ciclo do relógio.

- Capacidade para apenas um dado (palavra).

Armazenamento temporário de dados, instruções e endereços em utilização pelo processador.

- Armazena internamente resultados (ex: AC, MQ, AX - DX)

- Auxilia no controle das operações (ex: PC, IR, MAR, MBR)

Possuem diferentes funções, mas apresentam um uso bem definido dentro da arquitetura

Read-Only Memory (ROM)

As memórias ROM também possuem um nome criado há muitos anos e hoje é um termo que não faz tanto sentido.

Em português significam Memória Apenas de Leitura.

Isso porque as primeiras ROM eram escritas durante a fabricação e não podiam mais ser modificadas (consistiam de diodos que eram queimados na fabricação).

Mas outras gerações foram desenvolvidas que permitiram a escrita e tornou o termo ROM antiquado.

Todas memórias ROM são não voláteis, ou seja, mantêm seu conteúdo mesmo com a falta do fornecimento de energia elétrica.

Sua grande aplicação é no armazenamento de sistemas operacionais de computadores e outros sistemas digitais, em circuitos de geração de caracteres, na construção de circuitos combinacionais.

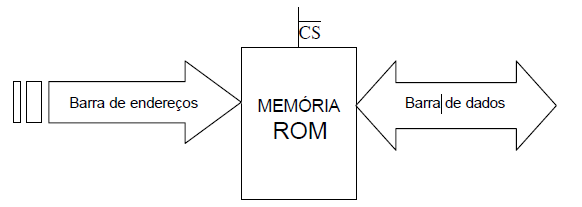

A Figura 22 apresenta o bloco representativo de uma memória ROM, com terminais e barramentos.

Figura 22 - Bloco representativo de uma memória ROM com terminais e barramentos.

O terminal de controle CS (Chip Select) refere-se à habilitação ou seleção da pastilha, ou seja, é uma entrada de nível lógico que, quando em 0, ativa ou habilita as saídas para fornecer os dados armazenados ou para serem lidos, conforme o endereçamento estabelecido.

Se o terminal de controle estiver em 1, as saídas estarão desabilitadas, assumindo estados de alta impedância (tri-state), liberando a barra de dados para uso por outros dispositivos presentes num sistema controlado por microprocessador.

A escolha do nível lógico 0 para habilitação é por razão em proporcionar maior imunidade ao ruído. Com nível lógico 1, haveria maior suscetibilidade para o acionamento dos blocos dentro do sistema diante de um transiente indesejável.

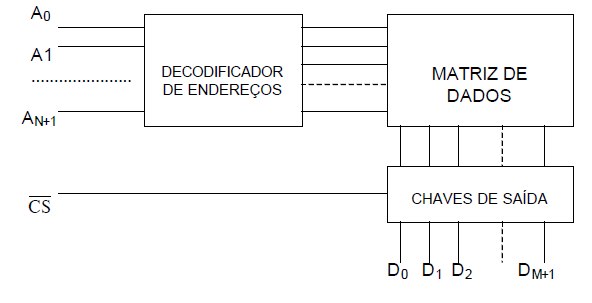

A arquitetura básica de uma ROM genérica é apresentada em blocos abaixo, com os respectivos terminais e barramentos de entrada e saída.

Figura 23 - Blocos da arquitetura básica de uma memória ROM.

O decodificador de endereços (multiplexador) ativa uma saída de cada vez em função do endereçamento.

A matriz de dados (arranjo de linhas e colunas) possibilita a gravação dos dados pelo fabricante e conseqüente leitura pelo usuário.

Para a saída dos dados, a memória possui um conjunto de chaves lógicas (buffers) que, conforme a habilitação através do terminal CS, possibilita a conexão das saídas (em nível 0) ou imprime alta impedância (em nível 1) desconectando as saídas de dados do sistema.

- Exemplo 1

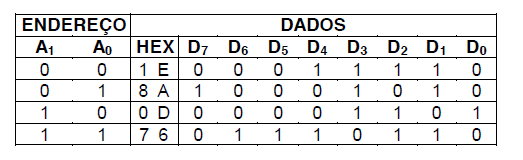

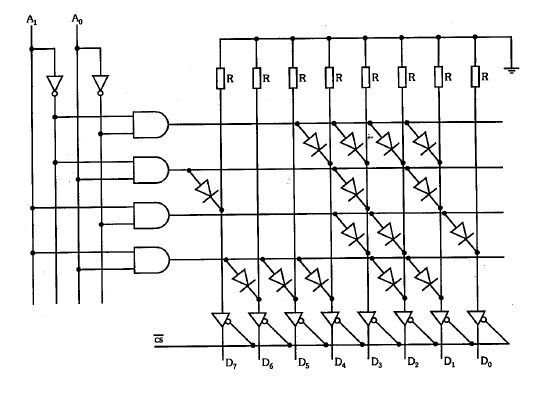

Para evidenciar a estrutura interna dos blocos e explicar seu funcionamento, será construída uma memória ROM de 4 palavras de 8 bits, cujo conteúdo dos dados é mostrado na tabela abaixo.

Figura 24 - Tabela com dados de uma memória ROM de 4 palavras de 8 bits.

O circuito a seguir apresenta o codificador de endereços constituído de portas lógicas inversora e E, a matriz de dados formada por diodos semicondutores e as chaves de saídas constituídas por buffers ativos com zero.

Figura 25 - Matriz de dados formada por um conjunto de diodos que constitui a célula da memória.

A matriz de dados formada por um conjunto de diodos constitui a célula da memória, definindo uma série de portas lógicas OU, de modo que a presença do diodo em determinada localidade estabelece nível lógico 1 e, a sua ausência, o nível lógico 0.

Para analisar um dado de saída específico, será endereçado A1A0 = 00 e aplicado à entrada de controle CS = 0, ativando o conjunto de buffers.

Neste endereço, apenas o fio de saída da primeira porta lógica E é ativado com 1 pelo decodificador, provocando a condução de corrente dos respectivos diodos através dos resistores R ao terra do circuito.

Devido a estas conduções, os resistores apresentarão quedas de tensão que serão transpostas pelos fios até as saídas D4, D3, D2 e D1, resultando no dado 00011110(2) = 1E(16).

Portanto, as saídas apresentam nível lógico 1 onde houver diodos conectados na matriz e nível lógico 0, na ausência de diodos.

Na tecnologia de fabricação da matriz de dados, também são utilizados outros elementos semicondutores, tais como transistores bipolares ou transistores de efeito de campo (MOS-FET).

O processo de programação é facilitado pelo uso de um gabarito fotográfico das ligações elétricas chamado máscara, donde provêm as memórias denominadas MROM programadas por Máscara.

As memórias ROM ainda são produzidas com programações determinadas e sob encomenda, em grande quantidade e normalmente para clientes específicos e/ou fabricantes de equipamentos.

Para o pequeno usuário, a solução é o uso das ROMs programáveis.

Memórias PROM (Programmable ROM)

são memórias que vem com a conexões abertas de fábrica e precisam de uma máquina para que os dados sejam escritos nelas.

Uma vez escritos, eles não podem mais ser modificados.

O princípio básico de programação numa PROM é a destruição de pequenas ligações semicondutoras existentes (diodo ou fusível em série com diodo) internamente nas localidades onde se quer armazenar a palavra de dados, através de um nível de tensão convenientemente especificado pelo fabricante e conforme o endereçamento realizado.

Este roteiro é fornecido pelo fabricante através de manuais ou através de kits apropriados para realizar os procedimentos conforme o tipo de pastilha, com maior eficiência e rapidez.

Memórias EPROM (Erasable PROM)

se baseiam no mesmo princípio das PROM, mas uma máquina especial que utiliza raios UV pode ser utilizada para apagar todo seu conteúdo e escrever novamente.

As memórias EPROM (Erasable Programmable Read-Only Memory) permitem programar e apagar dados, mediante banho de luz ultravioleta, efetuado através da exposição da pastilha por uma janela existente em seu encapsulamento e, ainda, serem reprogramadas.

São também conhecidas como UVPROM (Ultraviolet PROM).

Figura 26 - Memórias EPROM (Erasable Programmable Read-Only Memory).

É um dispositivo com arquitetura similar às memórias PROM, do tipo MOS, onde a gravação é feita através de circuitos eletrônicos especiais e o apagamento do conjunto inteiro das informações armazenadas é feito através da aplicação de raios ultravioleta em uma janela de quartzo localizada numa das faces do chip, durante um intervalo de tempo entre 10 a 30 minutos.

Após o apagamento, todas as localidades assumem níveis lógicos 1, podendo o processo de regravação e apagamento se repetir por inúmeras vezes.

Uma fita adesiva opaca deve ser colocada sobre a janela após a reprogramação para evitar que ela seja acidentalmente apagada pela luz ambiente.

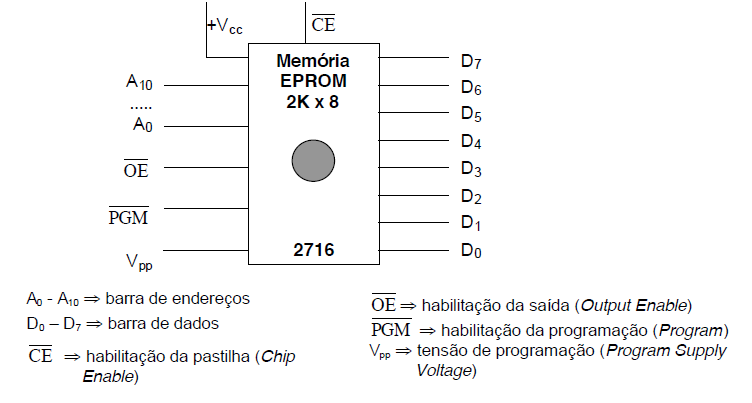

O desenho a seguir mostra o bloco de uma memória EPROM de 2k x 8 bits, com a respectiva terminologia e função dos terminais dos barramentos.

Figura 27 - Bloco de uma memória EPROM de 2k x 8 bits.

Para a capacidade desta memória, o acesso às localidades é efetuado por 11 fios (211 = 2.048 = 2k) e 8 fios para a barra de dados.

Quando CE=0, ativa o bloco e quando CE=1, o bloco permanece desativado na situação de baixo consumo de potência (stand-by).

A entrada de controle OE =0 habilita o barramento de saída.

A programação é efetuada pelo terminal Vpp com uma tensão típica maior que Vcc, da habilitação de programação PGM =0, do endereçamento e da aplicação das respectivas palavras de dados ao bloco, sequencialmente, possibilitarão o armazenamento das informações.

Memórias EEPROM (Electronically Erasable PROM)

possuem o mesmo princípio das PROM, mas a máquina utilizada para escrita e apagar é eletrônica.

Isso permite que um computador, ou um máquina especial seja utilizada para escrever nas memórias, as tornando muito mais utilizadas.

As memórias EEPROM ou E2PROM (Electrically Erasable Programmable Read-Only Memory) permitem o apagamento dos dados eletricamente, além de possibilitar esta ação isoladamente por palavra de dados, sem necessidade de reprogramação total.

As alterações de programação podem ser efetuadas pelo próprio sistema onde a memória estiver inserida, sem necessidade de sua desconexão do soquete.

Apesar desta memória ser acessível para escrita e leitura, a mesma faz parte das memórias PROM.

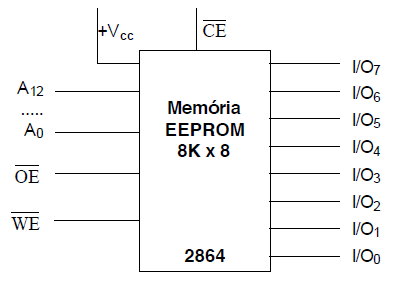

O bloco abaixo representa uma EEPROM de 8k x 8.

Figura 28 - Bloco de uma memória EEPROM de 8k x 8.

O acesso das localidades desta memória pe estabelecido através de 13 entradas de endereço (213= 8.192 = 8k) e oito pinos de entrada/saída de dados.

A barra de dados I/O é bidirecional por possibilitar a escrita e a leitura.

A escrita de uma palavra de dados é obtida através do endereçamento e respectiva aplicação da palavra nos terminais da barra de dados, isto é, com o terminal OE =1 e o de habilitação da escrita WE=0, dentro de um ciclo de tempo mínimo especificado pelo fabricante (normalmente 10 ms).

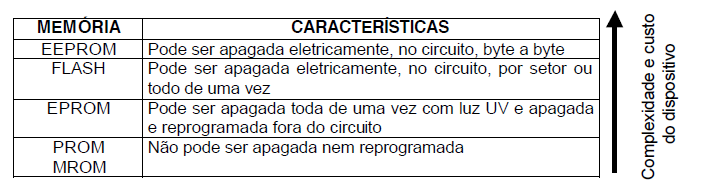

Memórias Flash

se baseiam no princípio das memórias EEPROM, mas o processo de apagar é feito em blocos grandes, o que acelera bastante o processo.

As memórias flash recebem esta denominação por possuírem tempos curtos de apagamento e escrita.

A maioria destas memórias efetua o apagamento em bloco e dura em torno de centenas de ms.

Entretanto, também são encontradas memórias mais recentes que oferecem o modo de apagamento por setor.

A tabela abaixo mostra as vantagens e desvantagens dos vários tipos de memórias semicondutoras não-voláteis. À medida que aumenta a flexibilidade para apagar e programar, também aumentam a complexidade e o custo do dispositivo.

Figura 29 - Tabela com a relação entre tipo de memória e suas características.

As memórias ROM são muito utilizadas na formação da BIOS dos computadores e as memórias Flash são o princípio básico de cartões de memória, pen-drives e memórias de estado sólido.

Aplicações de Memória ROM

- Firmware – armazenamento de programas ou dados que devem estar disponíveis no processo de inicialização de sistemas microprocessados. Por exemplo, produtos como videocassetes, CD players, fornos microondas etc.

- Memória de Bootstrap – tipo de programa armazenado em uma ROM que trata da inicialização do hardware de um computador. Após a inicialização, o programa de bootstrap chama o sistema operacional e o computador começa a executar o sistema operacional.

- Tabela de Dados – as ROMs são bastante utilizadas para armazenar tabelas de dados que não variam. Por exemplo, tabela trigonométricas, códigos ASCII, etc.

- Conversor de Códigos – este tipo de aplicação toma valores expressos em um determinado tipo de código e produz uma saída expressa em outro código. Por exemplo, o código BCD pode ser convertido para 7 segmentos por uma ROM.

- Gerador de Funções – basicamente, um gerador de funções é um circuito que produz formas de onda senóides, triangulares e quadradas. Uma ROM com tabelas de valores armazenados e um conversor D/A podem ser usados para gerar essas formas de onda.

- Armazenamento Auxiliar – dados podem ser armazenados em memórias ROM apagáveis (EPROM, EEPROM, FLASH), tornando essas memórias como alternativa aos discos magnéticos de armazenamento.

Formato dos módulos

Existem diferentes formatos para os módulos de memória.

Além disso, os chips de memória destes módulos também podem possuir tecnologias diferentes.

É bastante comum as confundir formatos de módulos (SIMM, DIMM, etc.) com a tecnologia das memórias que os compõem (FPM, EDO, SRAM, etc.)

Os tipos de DRAM existentes variam em função da capacidade, velocidade, consumo, custo e versatilidade:

- SIMM (Single-In-line Memory Module) e DIMM (Dual-In-line Memory Module) – são módulos de memória que permitem uma instalação rápida e são padrões de diversos tipos de DRAMs. Os módulos SIMM e DIMM definem apenas como a DRAM é “empacotada”.

- DRAM FPM (Fast Page module) – permite acesso mais rápido a qualquer posição de memória dentro da “página” corrente. Normalmente, a maioria dos dados gravados na memória são seqüenciais. Nesse tipo de DRAM, o endereço da linha (RAS) é enviado uma vez e o endereço da coluna (CAS) é incrementado.

- DRAM EDO (Extended data output) – é uma melhoria em relação às FPM. Os dados são colocados na saída e a DRAM EDO já pode decodificar o próximo endereço sem que esses dados tenham sido lidos;

- DRAM BEDO (Burst EDO) – Possui uma arquitetura que permite alcançar alta velocidade ao se acessar dados seqüenciais;

- SDRAM (Synchronous DRAM) – são organizadas em dois bancos que são acessados alternadamente utilizando um sinal de clock sincronizado com a CPU. Desse modo essas memórias alcançam altas taxas de transferências.

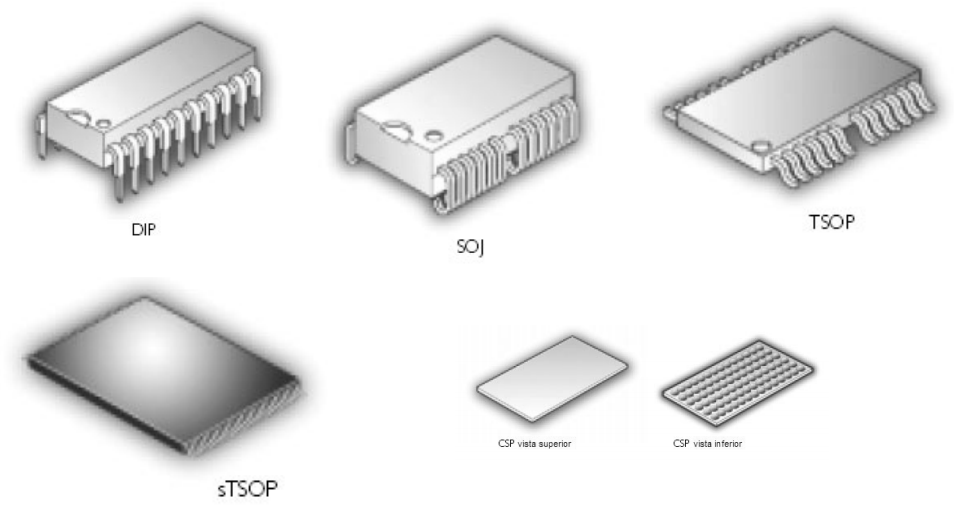

Encapsulamento

É o nome que se dá ao formato físico e pinagem dos chips.

Os antigos chips de memória, da época do PC XT usavam um encapsulamento do tipo DIP.

Este encapsulamento também é muito comum em chips de memória ROM usados nas placas mãe.

Os principais tipos de encapsulamento para chips de memória:

Figura 30 - Tipos de encapsulamento para chips de memória.

- DIP (Dual In-line Package)

- Quando se fala em chip, normalmente é a primeira imagem que se lembra. Este é o encapsulamento DIP, que hoje em dia já está caindo em desuso.

- SOJ (Small Outline J-Lead)

- Este encapsulamento tem este nome porque os terminais do chip se dobram em forma de “J”. Este chip não é encaixado em pinos das placas. Ao invés disso é montado num processo mais parecido com uma “colagem” do chip e muito usado atualmente nas placas de circuito. Este processo é chamado de tecnologia de montagem em superfície (SMT).

- TSOP (Thin Small Outline Package)

- No Encapsulamento TSOP, o chip tem uma espessura muito pequena, bem menor que a do chip com encapsulamento SOJ. Foi usado pela primeira vez em cartões de memória para notebooks.

- sTSOP (Shrink Thin Small Outline Package)

- Uma variação do encapsulamento TSOP, com a metade de seu tamanho. Permite mais memória em menos espaço.

- CSP (Chip Scale Package)

- Ao contrário dos encapsulamentos já apresentados, o CSP não usa pinos para se conectar ao PCB. Ao invés disso ele possui pequenas esferas de metal em sua parte inferior. Este padrão de encaixe é chamado de BGA (Ball Grid Array). As memórias do tipo RDRAM e DDR-II usam este tipo de encapsulamento.

Empilhamento de chips

O empilhamento de chips é usado para conseguir chips com quantidades de memória maiores.

Pode ser interno ou externo.

Nos empilhamentos externos podemos ver claramente os chips um em cima do outro.

Já no empilhamento interno isto não é possível.

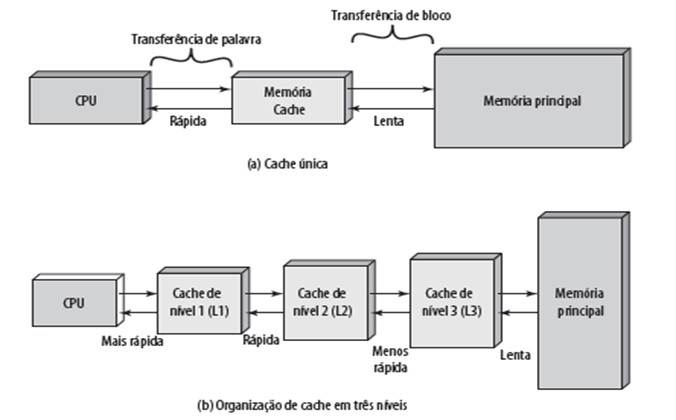

Memória Cache

Apesar de toda a evolução, a RAM continua sendo muito mais lenta que o processador.

Para atenuar a diferença, são usados dois níveis de cache, incluídos no próprio processador: a cache L1 e a cache L2.

Figura 31 - Chip de processador onde encontramos as memórias cache L1 e a cache L2.

Quando o processador deseja ler uma palavra da memória, é realizado um teste para determinar se a palavra está na memória cache, ou cacheada, como se diz.

Se estiver, ela é fornecida ao processador. Caso contrário, um bloco de dados da memória principal, constituído por um número fixo de palavras, é lido para a memória cache e, em seguida, a palavra requerida é entregue ao processador.

Figura 32 - Organização de memória cache única (a) ou em três níveis (b).

Ou seja, a CPU faz referência ao conteúdo de uma determinada posição de memória (palavra):

- Se o conteúdo está na cache ⇒ acerto ou hit:

- A palavra desejada é enviada para a CPU.

- Se o conteúdo NÃO está na cache ⇒ falha ou miss:

- O bloco correspondente é transferido da MP à cache.

- A palavra desejada é enviada para a CPU.

Em razão do fenômeno da localidade de referências, quando um bloco de dados é trazido para a memória cache para satisfazer uma dada referência à memória, é provável que futuras referências sejam feitas para outras palavras desse bloco.

A cache L1 é extremamente rápida, trabalhando próximo à frequência nativa do processador.

Em seguida vem o cache L2, que é um pouco mais lento tanto em termos de tempo de acesso (o tempo necessário para iniciar a transferência) quanto em largura de banda, mas é bem mais econômico em termos de transistores, permitindo que seja usado em maior quantidade.

O volume de cache L2 usado varia muito de acordo com o processador. Enquanto a maior parte dos modelos do Sempron utilizam apenas 256 KB, os modelos mais caros do Core 2 Duo possuem 4 MB completos.

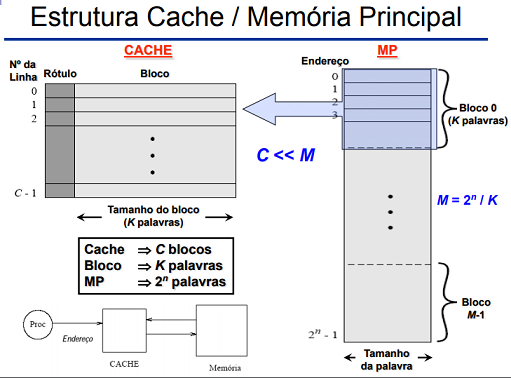

A Figura 33 representa a estrutura de um sistema de memória com uma memória principal (MP) e uma cache.

Figura 33 - Estrutura de um sistema de memória com uma memória principal (MP) e uma cache.

A memória principal é constituída de 2^n palavras endereçáveis, cada qual com um endereço distinto de n bits.

Para fins de mapeamento na cache, podemos considerar essa memória sendo constituída de um determinado número de blocos de tamanho fixo, cada qual com K palavras.

Ou seja, vão existir M = 2^n/K blocos.

A memória cache consistirá de C linhas de K palavras. sendo sempre o número de linhas C consideravelmente menor que o número de blocos da memória principal (C << M).

Em qualquer instante, um subconjunto dos blocos da memória principal reside nas linhas da cache.

Ao ler uma palavra de um bloco da MP, esse bloco todo é transferido para a cache.

Como existe um número maior de blocos do que linhas da cache, não é possível uma linha armazenar um mesmo bloco permanentemente.

Assim, cada linha inclui um rótulo que identifica qual é o bloco de memória nela armazenado. Esse rótulo é geralmente uma parte do endereço de MP.

Políticas de atualização

Antes que um bloco residente na memória cache possa ser substituído, é necessário verificar se ele foi alterado na cache, mas não na MP.

Se isso não ocorreu, então um novo bloco pode ser escrito sobre o bloco antigo.

Caso contrário, se pelo menos uma operação de escrita foi feita sobre uma palavra dessa linha da cache, então a MP deve ser atualizada.

O problema é muito complexo, uma vez que a referida palavra pode ser alterada também por dispositivos de E/S e por outras caches.

A técnica de atualização mais simples é denominada escrita direta (write-through). Nesta, todas as operações de escrita são feitas tanto na memória cache, quanto na MP, assegurando assim que a MP esteja sempre com os dados válidos.

A principal desvantagem é que esta técnica gera um tráfego de memória considerável, podendo criar um gargalo no sistema.

Em uma outra alternativa, chamada de escrita de volta (write-back), todas as operações de escrita são feitas apenas na memória cache. Quando é feita uma atualização, é atribuído valor 1 a um bit de ATUALIZAÇÃO, associado à linha atualizada na cache.

Quando um bloco vai ser substituído, ele apenas é escrito de volta na MP se seu bit de atualização for 1.

O problema desta técnica é que, se neste ínterim, se outro módulo tentar acessar diretamente a MP, pode vir a recuperar dados inválidos/desatualizados.

O acesso teria que ser sempre restrito também à memória cache, podendo gerar um gargalo.

Algoritmo de Substituição

Define em qual bloco da cache deve ser colocado um novo conteúdo trazido da memória principal.

⇒ Implementação em hardware.

⇒ Blocos modificados na cache devem ser gravados antes de sua troca (política de atualização).

Os algoritmos de substituição mais usados são:

- LRU (Least Recently Used): substitui o bloco da cache que está mais tempo sem uso.

- Provavelmente o algoritmo mais eficiente.

- Implementado através de adição de bits de uso.

- FIFO (First In, First Out): substitui a linha de cache que está a mais tempo na cache.

- Implementado através de um armazenamento circular.

- LFU (Least Frequently Used): substitui a linha de cache que foi menos referenciada.

- Implementada através de um campo contador.

- Aleatório: escolhe aleatoriamente a linha de cache a ser substituída.

- Não é baseada no histórico de uso das linhas.

- Apresenta uma ligeira perda no desempenho

Material de Apoio

[1] Videoaula | Memória Interna