Mudanças entre as edições de "Laboratórios com Altera NIOS2"

| Linha 34: | Linha 34: | ||

Para utilizar versões modificadas do hardware, precisaremos também modificar o software que carregamos no Nios II. | Para utilizar versões modificadas do hardware, precisaremos também modificar o software que carregamos no Nios II. | ||

As informações a respeito do sistema de software gerado com apoio das ferramentas da Altera estão [https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/hb/nios2/n2sw_nii5v2.pdf neste manual]. | As informações a respeito do sistema de software gerado com apoio das ferramentas da Altera estão [https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/hb/nios2/n2sw_nii5v2.pdf neste manual]. | ||

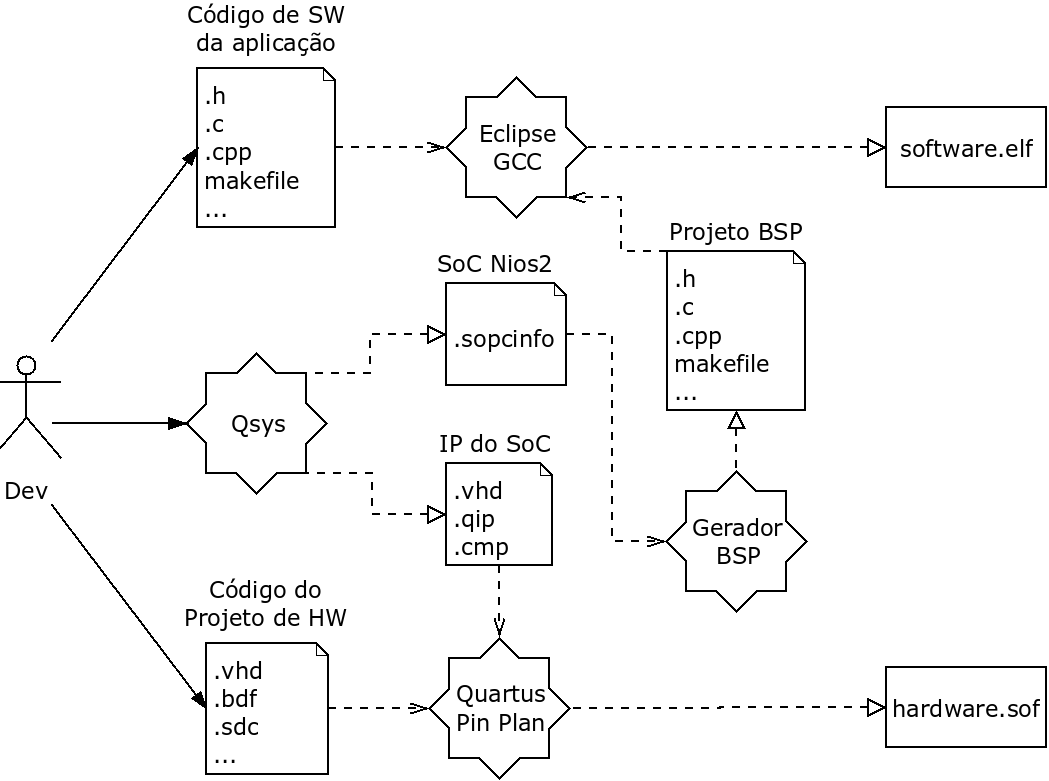

| − | + | Nas figuras abaixo, a primeira apresenta o fluxo de projeto utilizando as ferramentas da Altera. As duas seguintes, retiradas do manual, nos dão, respectivamente, uma visão geral da arquitetura deste software e da organização dos projetos no eclipse. | |

| + | |||

| + | [[Arquivo:fluxo-soc-altera.png]] | ||

[[Arquivo:nios2_sw_arch.png]] | [[Arquivo:nios2_sw_arch.png]] | ||

Edição das 10h28min de 7 de março de 2017

Roteiro Básico

Nesta aula nós seguiremos um tutorial da Altera para construir um System-on-a-Chip (SoC), sintetizando um processador softcore NIOS em uma FPGA e carregando um software nele. Nas próximas aulas nós integraremos nossa própria lógica neste processador. Esta arquitetura de sistema deverá ser empregada em todos os trabalhos ao longo do semestre.

A figura abaixo dá uma visão geral do que iremos implementar:

Você precisará destes documentos para desenvolver este tutorial:

- Tutorial com pontos importantes destacados.

- Código-base para início do tutorial na ALTERA,no IFSC

- Pinagem dos dispositivos de entrada e saída do kit MERCURIO IV

- Esquemático da MercurioIV

- Preparando para gravar o circuito lógico no FPGA

Recomenda-se seguir este roteiro:

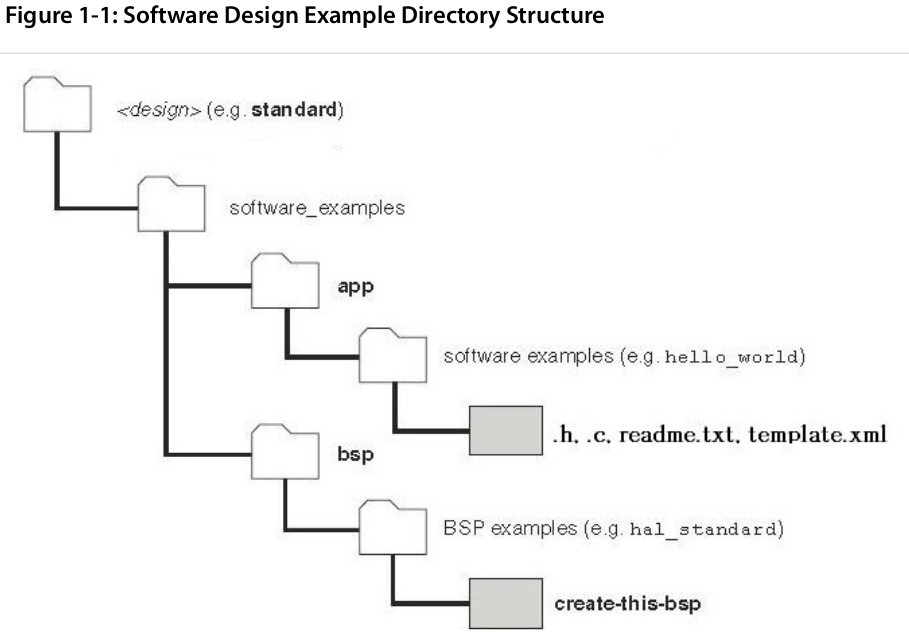

- Analisar e debater figura 1-1 na página 1-2;

- Destacar os requisitos de hardware para o experimento na página 1-3;

- Analisar e debater o fluxo de desenvolvimento de projeto da figura 1-2 na página 1-4;

- Debater as questões de análise de requisitos do sistema na página 1-5;

- Partir para criação do exemplo na página 1-8;

- Seguir tutorial (passos importantes destacados no PDF);

- Usando o Pin Planner (Assignment > Pin Planner) selecione os pinos corretos no kit Mercúrio IV. Veja a pinagem em Preparando para gravar o circuito lógico no FPGA.

- Mude a tensão default dos pinos para 3.3V (Assignment > Device > Device and Pin Options > Voltage), [Default I/O standard = 3.3-V LVTLL] [OK] [OK]

- Configure os pinos não usados para Tri-State (Assignment > Device > Device and Pin Options > Unused Pins), [Reserve all unused pins = As input tri-stated] e [OK] [OK]

Se o Eclipse SBT do Nios II não inicializar em um sistema Ubuntu 14.04 ou mais recente, você precisa instalar a libGTK2:

sudo apt-get install libgtk2.0-0:i386

Desenvolvimento de software para o Nios II

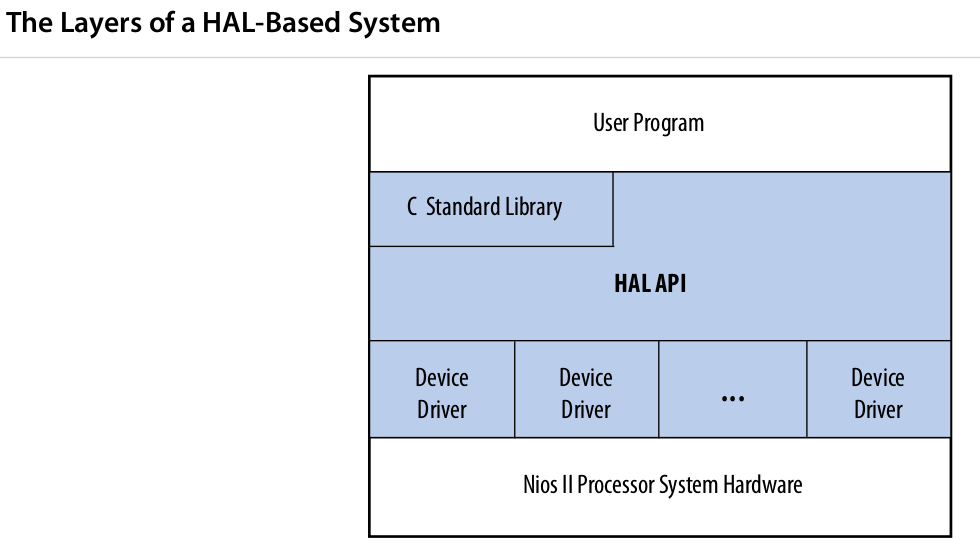

Para utilizar versões modificadas do hardware, precisaremos também modificar o software que carregamos no Nios II. As informações a respeito do sistema de software gerado com apoio das ferramentas da Altera estão neste manual. Nas figuras abaixo, a primeira apresenta o fluxo de projeto utilizando as ferramentas da Altera. As duas seguintes, retiradas do manual, nos dão, respectivamente, uma visão geral da arquitetura deste software e da organização dos projetos no eclipse.

Outras questões importantes a serem entendidas sobre o BSP gerado pela Altera:

Arquivo system.h

Este arquivo contém a descrição do hardware Nios II. Este arquivo contém os detalhes de cada periférico integrado ao Nios II, incluindo as configurações do periférico, o endereço base dos registradores, informações sobre IRQ (se houver) e um nome simbólico para o dispositivo. Exemplo:

/*

* sys_clk_timer configuration

*

*/

#define SYS_CLK_TIMER_NAME "/dev/sys_clk_timer"

#define SYS_CLK_TIMER_TYPE "altera_avalon_timer"

#define SYS_CLK_TIMER_BASE 0x00920800

#define SYS_CLK_TIMER_IRQ 0

#define SYS_CLK_TIMER_ALWAYS_RUN 0

#define SYS_CLK_TIMER_FIXED_PERIOD 0

Definição de tipos

O BSP também define tipos padrão para integração com o processador no arquivo alt_types.h. Os tipos definidos são os abaixo:

- alt_8: Signed 8-bit integer.

- alt_u8: Unsigned 8-bit integer.

- alt_16: Signed 16-bit integer.

- alt_u16: Unsigned 16-bit integer.

- alt_32: Signed 32-bit integer.

- alt_u32: Unsigned 32-bit integer.

- alt_64: Signed 64-bit integer.

- alt_u64: Unsigned 64-bit integer.

Como as ferramentas integradas pela Altera incluem o Gnu GCC, os seguintes tipos da linguagem C para aquele compilador também são suportados:

- (unsigned) char: 8 bits.

- (unsigned) short: 16 bits.

- (unsigned) long: 32 bits.

- (unsigned) int: 32 bits.

Funções de API equivalentes ao UNIX

A HAL do BSP provê algumas funções similares às disponíveis em sistemas UNIX para facilitar a integração dos programas com a biblioteca padrão ANSI C. Estas funções estão definidas no cabeçalho stdio.h, e inclui as funções _exit(), close(), fstat(), getpid(), gettimeofday(), ioctl(), isatty(), kill(), lseek(), open(), read(), sbrk(), settimeofday(), stat(), usleep(), wait(), write().

Sistema de arquivos

A HAL do BSP também oferece algumas funções para acesso a arquivo que podem ser utilizadas para construir um sistema de arquivos sobre qualquer dispositivo de armazenamento. Estas declarações estão no file.h.

Char devices

Dispositivos de caractere (e.g., UART) podem ser registrados como nós no sistema de arquivos da HAL e manipulados pelas mesmas operações definidas no file.h, assim como ocorre em sistemas UNIX.

Entrada e Saída Padrão

A HAL também suporta operações sobre a entrada padrão (stdin), saída padrão (stdout) e saída de erro padrão (stderr). Esta manipulação pode ser feito pelas chamadas printf() e perror(), declarados no stdio.h.

Mais detalhes da API da HAL

No capítulo 14 do manual.

Modificações Propostas

Modificação 1: Mais GPIOs

Modificar o projeto da aula passada para:

- Ler um conjunto de entradas digitais a partir das chaves da placa;

- Obter estes sinais no software rodando no Nios através de uma PIO;

- Escrever estes sinais para LEDs no software, através de outra PIO.

Modificação 2: Integração de componente externo

Modificar projeto realizado anteriormente para:

- Incluir um módulo VHDL multiplicador;

- Utilizar saídas PIO do Nios para gerar entradas do módulo;

- Utilizar uma entrada PIO do Nios para ler a saída do módulo;

Modificação 3: Integração de componente externo com FIFOs

Modificar projeto realizado anteriormente para:

- No Qsys, remover/desabilitar componentes PIO para integração com o componente externo;

- Criar FIFOs (onchip FIFO memory) mapeadas em memória (Avalon-MM) de 8x32 bits para cada saída (2) e para a entrada (1);

- Conectar as entradas (in) das FIFOs de saída à CPU, e exportar suas saídas (out);

- Conectar a saída (out) da FIFO de entrada à CPU, e exportar suas entradas (in);

- Regerar SoC e adaptar projeto no quartus;

- Para fins de teste de software, você pode utilizar este componente para fazer um loopback entre FIFOs.