Mudanças entre as edições de "Interfaces de entrada e saída da DE2-115"

| Linha 95: | Linha 95: | ||

=Conexão dos Displays= | =Conexão dos Displays= | ||

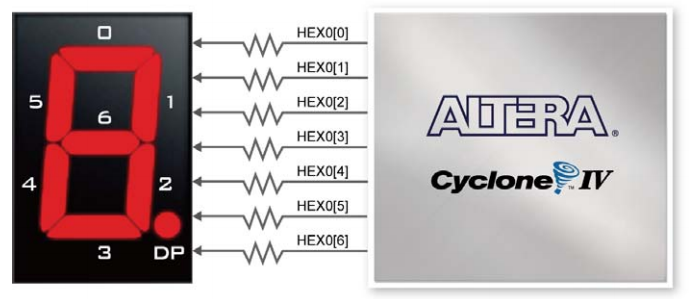

A placa DE2-115 tem oito [[Display de 7 segmentos]]. Estes displays são do tipo [[Display de 7 segmentos#Anodo_comum | '''anodo comum''']]. Eles estão conectados aos pinos do FPGA Cyclone IV conforme mostrado na figura abaixo. A pinagem no FPGA é mostrado na tabela abaixo. | A placa DE2-115 tem oito [[Display de 7 segmentos]]. Estes displays são do tipo [[Display de 7 segmentos#Anodo_comum | '''anodo comum''']]. Eles estão conectados aos pinos do FPGA Cyclone IV conforme mostrado na figura abaixo. A pinagem no FPGA é mostrado na tabela abaixo. | ||

| − | Aplicando um nível lógico '0' no pino correspondente fará com que o segmento acenda, enquanto que a aplicação do nível lógico '1' fará com com que ele fique apagado. Cada segmento é identificado com um índice de 0, 1, 2, 3, 4, 5, 6 (que correspondem os segmentos a, b, c, d, e, f, g). | + | Aplicando um nível lógico '0' no pino correspondente fará com que o segmento acenda, enquanto que a aplicação do nível lógico '1' fará com com que ele fique apagado. Cada segmento é identificado com um índice de 0, 1, 2, 3, 4, 5, 6 (que correspondem os segmentos a, b, c, d, e, f, g). O LED do ponto decimal (DP) dos displays não está conectado ao FPGA. |

[[Arquivo:ConectDE2-115-Display.png | right |400px]] | [[Arquivo:ConectDE2-115-Display.png | right |400px]] | ||

==Pinagem dos oito Display de sete segmentos== | ==Pinagem dos oito Display de sete segmentos== | ||

| + | [[Arquivo:DE2-115-Display.png | right |400px]] | ||

<table border="1" cellpadding="2"> | <table border="1" cellpadding="2"> | ||

Edição das 15h36min de 12 de dezembro de 2018

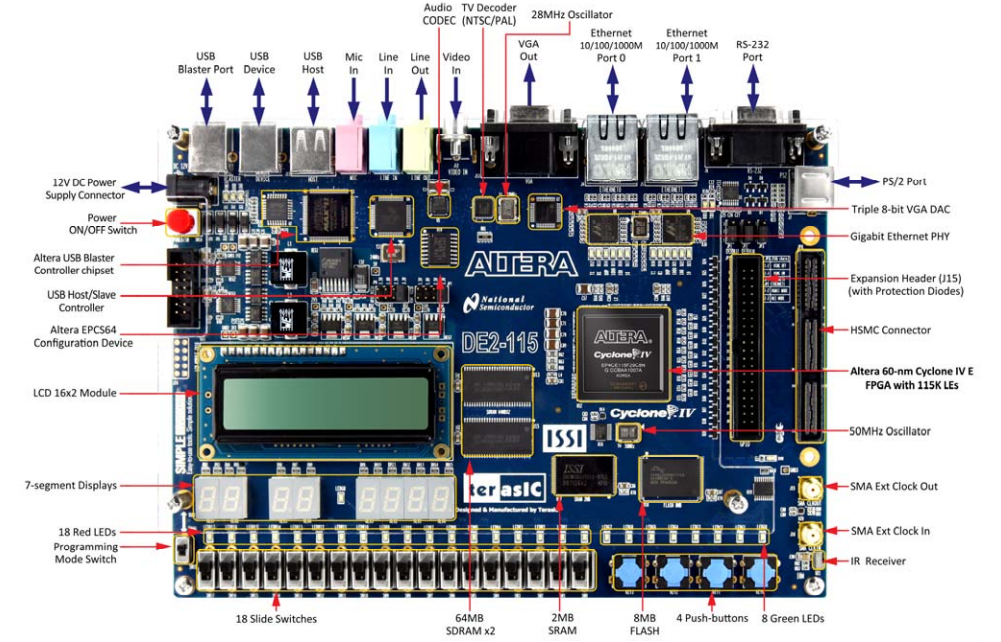

Interfaces Externas

Conexões do Sinal de Clock

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| CLOCK_50 | PIN_Y2 | 50 MHz clock input | 3.3V |

| CLOCK2_50 | PIN_AG14 | 50 MHz clock input | 3.3V |

| CLOCK3_50 | PIN_AG15 | 50 MHz clock input | Depending on JP6 |

| SMA_CLKOUT | PIN_AE23 | External (SMA) clock output | Depending on JP6 |

| SMA_CLKIN | PIN_AH14 | External (SMA) clock input | 3.3V |

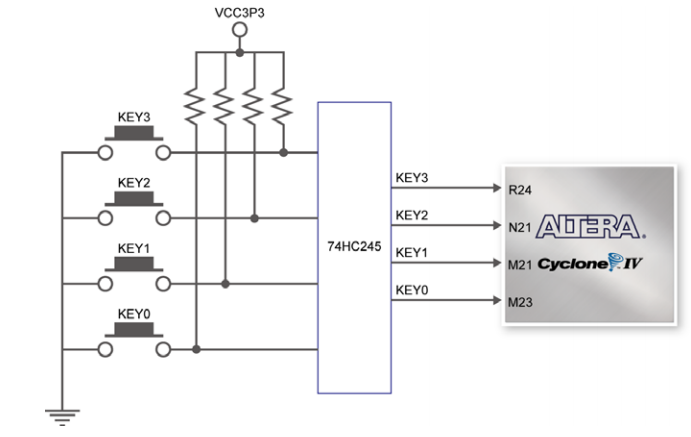

Conexões das Chaves de contato momentâneo KEY0-3

Observe atentamente este diagrama, pois as chaves pushbottom estão normalmente em HIGH, e enquanto estiverem acionadas mudam para LOW. Muita atenção especialmente se for usar essa chave para um RESET do sistema. Neste caso normalmente é necessário incluir um inversor no circuito.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| KEY[0] | PIN_M23 | Push-button[0] | Depending on JP7 |

| KEY[1] | PIN_M21 | Push-button[1] | Depending on JP7 |

| KEY[2] | PIN_N21 | Push-button[2] | Depending on JP7 |

| KEY[3] | PIN_R24 | Push-button[3] | Depending on JP7 |

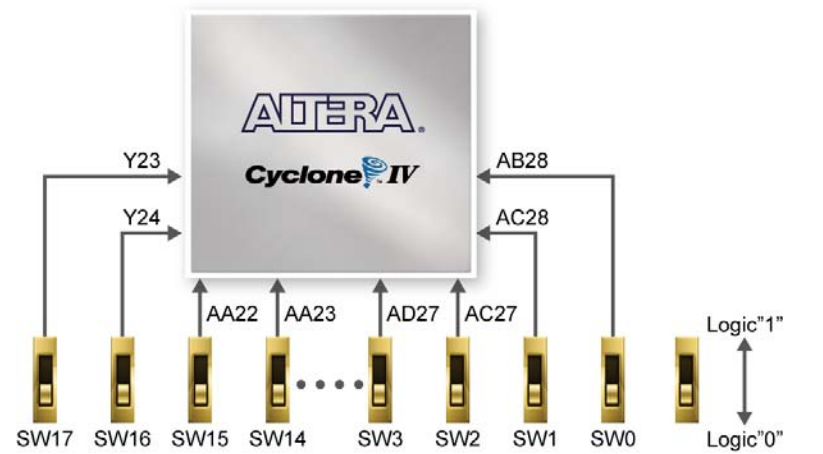

Conexões das Chaves SW01-17

| Signal Name | FPGA Pin No. | Pin | I/O Standard |

|---|---|---|---|

| SW[0] | PIN_AB28 | Slide Switch[0] | Depending on JP7 |

| SW[1] | PIN_AC28 | Slide Switch[1] | Depending on JP7 |

| SW[2] | PIN_AC27 | Slide Switch[2] | Depending on JP7 |

| SW[3] | PIN_AD27 | Slide Switch[3] | Depending on JP7 |

| SW[4] | PIN_AB27 | Slide Switch[4] | Depending on JP7 |

| SW[5] | PIN_AC26 | Slide Switch[5] | Depending on JP7 |

| SW[6] | PIN_AD26 | Slide Switch[6] | Depending on JP7 |

| SW[7] | PIN_AB26 | Slide Switch[7] | Depending on JP7 |

| SW[8] | PIN_AC25 | Slide Switch[8] | Depending on JP7 |

| SW[9] | PIN_AB25 | Slide Switch[9] | Depending on JP7 |

| SW[10] | PIN_AC24 | Slide Switch[10] | Depending on JP7 |

| SW[11] | PIN_AB24 | Slide Switch[11] | Depending on JP7 |

| SW[12] | PIN_AB23 | Slide Switch[12] | Depending on JP7 |

| SW[13] | PIN_AA24 | Slide Switch[13] | Depending on JP7 |

| SW[14] | PIN_AA23 | Slide Switch[14] | Depending on JP7 |

| SW[15] | PIN_AA22 | Slide Switch[15] | Depending on JP7 |

| SW[16] | PIN_Y24 | Slide Switch[16] | Depending on JP7 |

| SW[17] | PIN_Y23 | Slide Switch[17] | Depending on JP7 |

Conexões dos Leds

Pinagem dos LEDs verdes LEDG0-8

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| LEDG[0] | PIN_E21 | LED Green[0] | 2.5V |

| LEDG[1] | PIN_E22 | LED Green[1] | 2.5V |

| LEDG[2] | PIN_E25 | LED Green[2] | 2.5V |

| LEDG[3] | PIN_E24 | LED Green[3] | 2.5V |

| LEDG[4] | PIN_H21 | LED Green[4] | 2.5V |

| LEDG[5] | PIN_G20 | LED Green[5] | 2.5V |

| LEDG[6] | PIN_G22 | LED Green[6] | 2.5V |

| LEDG[7] | PIN_G21 | LED Green[7] | 2.5V |

| LEDG[8] | PIN_F17 | LED Green[8] | 2.5V |

Pinagem dos LEDs vermelhos LEDR0-17

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| LEDR[0] | PIN_G19 | LED Red[0] | 2.5V |

| LEDR[1] | PIN_F19 | LED Red[1] | 2.5V |

| LEDR[2] | PIN_E19 | LED Red[2] | 2.5V |

| LEDR[3] | PIN_F21 | LED Red[3] | 2.5V |

| LEDR[4] | PIN_F18 | LED Red[4] | 2.5V |

| LEDR[5] | PIN_E18 | LED Red[5] | 2.5V |

| LEDR[6] | PIN_J19 | LED Red[6] | 2.5V |

| LEDR[7] | PIN_H19 | LED Red[7] | 2.5V |

| LEDR[8] | PIN_J17 | LED Red[8] | 2.5V |

| LEDR[9] | PIN_G17 | LED Red[9] | 2.5V |

| LEDR[10] | PIN_J15 | LED Red[10] | 2.5V |

| LEDR[11] | PIN_H16 | LED Red[11] | 2.5V |

| LEDR[12] | PIN_J16 | LED Red[12] | 2.5V |

| LEDR[13] | PIN_H17 | LED Red[13] | 2.5V |

| LEDR[14] | PIN_F15 | LED Red[14] | 2.5V |

| LEDR[15] | PIN_G15 | LED Red[15] | 2.5V |

| LEDR[16] | PIN_G16 | LED Red[16] | 2.5V |

| LEDR[17] | PIN_H15 | LED Red[17] | 2.5V |

Conexão dos Displays

A placa DE2-115 tem oito Display de 7 segmentos. Estes displays são do tipo anodo comum. Eles estão conectados aos pinos do FPGA Cyclone IV conforme mostrado na figura abaixo. A pinagem no FPGA é mostrado na tabela abaixo. Aplicando um nível lógico '0' no pino correspondente fará com que o segmento acenda, enquanto que a aplicação do nível lógico '1' fará com com que ele fique apagado. Cada segmento é identificado com um índice de 0, 1, 2, 3, 4, 5, 6 (que correspondem os segmentos a, b, c, d, e, f, g). O LED do ponto decimal (DP) dos displays não está conectado ao FPGA.

Pinagem dos oito Display de sete segmentos

| Segment | Signal Name | FPGA Pin No. | I/O Standard |

|---|---|---|---|

| a | HEX0[0] | PIN_G18 | 2.5V |

| b | HEX0[1] | PIN_F22 | 2.5V |

| c | HEX0[2] | PIN_E17 | 2.5V |

| d | HEX0[3] | PIN_L26 | Depending on JP7 |

| e | HEX0[4] | PIN_L25 | Depending on JP7 |

| f | HEX0[5] | PIN_J22 | Depending on JP7 |

| g | HEX0[6] | PIN_H22 | Depending on JP7 |

| Segment | Signal Name | FPGA Pin No. | I/O Standard |

| a | HEX1[0] | PIN_M24 | Depending on JP7 |

| b | HEX1[1] | PIN_Y22 | Depending on JP7 |

| c | HEX1[2] | PIN_W21 | Depending on JP7 |

| d | HEX1[3] | PIN_W22 | Depending on JP7 |

| e | HEX1[4] | PIN_W25 | Depending on JP7 |

| f | HEX1[5] | PIN_U23 | Depending on JP7 |

| g | HEX1[6] | PIN_U24 | Depending on JP7 |

| Segment | Signal Name | FPGA Pin No. | I/O Standard |

| a | HEX2[0] | PIN_AA25 | Depending on JP7 |

| b | HEX2[1] | PIN_AA26 | Depending on JP7 |

| c | HEX2[2] | PIN_Y25 | Depending on JP7 |

| d | HEX2[3] | PIN_W26 | Depending on JP7 |

| e | HEX2[4] | PIN_Y26 | Depending on JP7 |

| f | HEX2[5] | PIN_W27 | Depending on JP7 |

| g | HEX2[6] | PIN_W28 | Depending on JP7 |

| Segment | Signal Name | FPGA Pin No. | I/O Standard |

| a | HEX3[0] | PIN_V21 | Depending on JP7 |

| b | HEX3[1] | PIN_U21 | Depending on JP7 |

| c | HEX3[2] | PIN_AB20 | Depending on JP6 |

| d | HEX3[3] | PIN_AA21 | Depending on JP6 |

| e | HEX3[4] | PIN_AD24 | Depending on JP6 |

| f | HEX3[5] | PIN_AF23 | Depending on JP6 |

| g | HEX3[6] | PIN_Y19 | Depending on JP6 |

| Segment | Signal Name | FPGA Pin No. | I/O Standard |

| a | HEX4[0] | PIN_AB19 | Depending on JP6 |

| b | HEX4[1] | PIN_AA19 | Depending on JP6 |

| c | HEX4[2] | PIN_AG21 | Depending on JP6 |

| d | HEX4[3] | PIN_AH21 | Depending on JP6 |

| e | HEX4[4] | PIN_AE19 | Depending on JP6 |

| f | HEX4[5] | PIN_AF19 | Depending on JP6 |

| g | HEX4[6] | PIN_AE18 | Depending on JP6 |

| Segment | Signal Name | FPGA Pin No. | I/O Standard |

| a | HEX5[0] | PIN_AD18 | Depending on JP6 |

| b | HEX5[1] | PIN_AC18 | Depending on JP6 |

| c | HEX5[2] | PIN_AB18 | Depending on JP6 |

| d | HEX5[3] | PIN_AH19 | Depending on JP6 |

| e | HEX5[4] | PIN_AG19 | Depending on JP6 |

| f | HEX5[5] | PIN_AF18 | Depending on JP6 |

| g | HEX5[6] | PIN_AH18 | Depending on JP6 |

| Segment | Signal Name | FPGA Pin No. | I/O Standard |

| a | HEX6[0] | PIN_AA17 | Depending on JP6 |

| b | HEX6[1] | PIN_AB16 | Depending on JP6 |

| c | HEX6[2] | PIN_AA16 | Depending on JP6 |

| d | HEX6[3] | PIN_AB17 | Depending on JP6 |

| e | HEX6[4] | PIN_AB15 | Depending on JP6 |

| f | HEX6[5] | PIN_AA15 | Depending on JP6 |

| g | HEX6[6] | PIN_AC17 | Depending on JP6 |

| Segment | Signal Name | FPGA Pin No. | I/O Standard |

| a | HEX7[0] | PIN_AD17 | Depending on JP6 |

| b | HEX7[1] | PIN_AE17 | Depending on JP6 |

| c | HEX7[2] | PIN_AG17 | Depending on JP6 |

| d | HEX7[3] | PIN_AH17 | Depending on JP6 |

| e | HEX7[4] | PIN_AF17 | Depending on JP6 |

| f | HEX7[5] | PIN_AG18 | Depending on JP6 |

| g | HEX7[6] | PIN_AA14 | 3.3V |

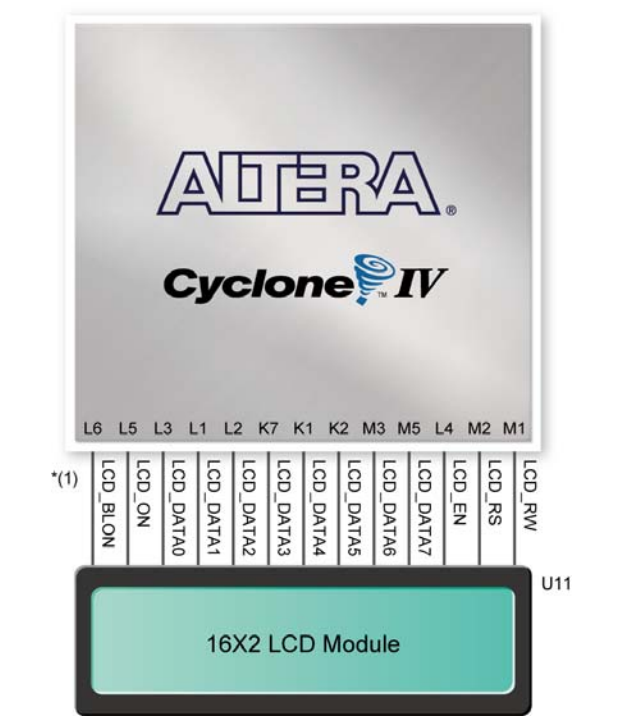

Conexão do LCD

A placa DE2-115 tem um LCD de 2 x 16 caracteres. Ele está conectados aos pinos do FPGA Cyclone IV conforme mostrado na figura abaixo. A pinagem no FPGA é mostrado na tabela abaixo.

O módulo LCD tem um gerador de caracteres que pode ser utilizado para mostrar os textos a partir do envio de comandos adequados para o controlador de display. Informações detalhadas sobre o uso do controlador podem ser obtidas no datasheet do HD44780.

Pinagem LCD

| Signal Name | FPGA Pin No. | I/O Standard |

|---|---|---|

| LCD_DATA[7] | PIN_M5 | 3.3V |

| LCD_DATA[6] | PIN_M3 | 3.3V |

| LCD_DATA[5] | PIN_K2 | 3.3V |

| LCD_DATA[4] | PIN_K1 | 3.3V |

| LCD_DATA[3] | PIN_K7 | 3.3V |

| LCD_DATA[2] | PIN_L2 | 3.3V |

| LCD_DATA[1] | PIN_L1 | 3.3V |

| LCD_DATA[0] | PIN_L3 | 3.3V |

| LCD Enable | PIN_L4 | 3.3V |

| LCD Read/~Write | PIN_M1 | 3.3V |

| LCD LCD Data Select/~Command | PIN_M2 | 3.3V |

| LCD Power ON | PIN_L5 | 3.3V |

| LCD Back Light ON | PIN_L6 | 3.3V |