Mudanças entre as edições de "Experimento 5 para Circuitos Lógicos"

Ir para navegação

Ir para pesquisar

| Linha 91: | Linha 91: | ||

#Note que apenas o segmento '''g''' está implementado. | #Note que apenas o segmento '''g''' está implementado. | ||

#Monte os demais segmentos, seguindo este exemplo e baseado em seu projeto já relaizado. | #Monte os demais segmentos, seguindo este exemplo e baseado em seu projeto já relaizado. | ||

| − | #Associe o dispositivo a ser utilizado: Assignments >> Device >> '''Family=Cyclone''' e '''Avaliable Devices: EP1C3T100A8''' ou '''Family: | + | #Associe o dispositivo a ser utilizado: Assignments >> Device >> '''Family=Cyclone''' e '''Avaliable Devices: EP1C3T100A8''' ou '''Family: Cyclone IV E''' e '''Available Devices: EP4CE30F23C7''' >> OK |

#Compile o projeto. | #Compile o projeto. | ||

#Associe os pinos (Assignments >> Assignment Editor) segundo um dos mapas: [[Interfaces_de_entrada_e_saída_da_DE2-115 | Interfaces de entrada e saída da DE2-115]] ou [[Pinagem_dos_dispositivos_de_entrada_e_saída_do_kit_MERCURIO_IV | kit MERCURIO IV - EP4CE30F23C7]]. | #Associe os pinos (Assignments >> Assignment Editor) segundo um dos mapas: [[Interfaces_de_entrada_e_saída_da_DE2-115 | Interfaces de entrada e saída da DE2-115]] ou [[Pinagem_dos_dispositivos_de_entrada_e_saída_do_kit_MERCURIO_IV | kit MERCURIO IV - EP4CE30F23C7]]. | ||

Edição das 08h39min de 24 de abril de 2019

Introdução ao sistema de numeração binário e aplicação do Mapa de Karnaugh

- Objetivos

- Aplicar o Mapa de Karnaugh para a criação de um decodificador de 7-segmentos;

- Gerar formas de onda para entrada de simulação;

- Fazer a simulação funcional do circuito com o QSIM;

- Materiais necessários

- 74X08 AND(disponível na biblioteca da ALTERA)

- 74X32 OR(disponível na biblioteca da ALTERA)

- 74X04 NOT(disponível na biblioteca da ALTERA)

- Computador com software Quartus II da Altera.

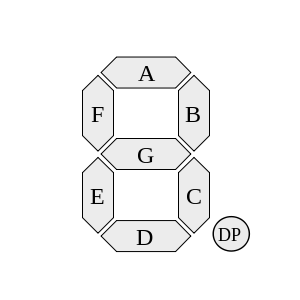

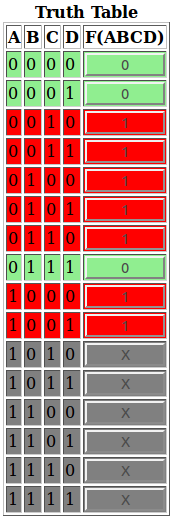

Tabela Verdade do decodificador SSD (Sete Segmentos - 0 a 9)

- Preencha a tabela verdade para todos os segmentos, para isso, analise as entradas e quais segmentos deverão estar acesos ou apagados a partir de uma configuração de catodo comum;

- Siga o exemplo do segmento G:

| Entradas | Saídas | Decimal | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| A | B | C | D | a | b | c | d | e | f | g | Display |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 2 |

| 0 | 0 | 1 | 1 | 1 | 3 | ||||||

| 0 | 1 | 0 | 0 | 1 | 4 | ||||||

| 0 | 1 | 0 | 1 | 1 | 5 | ||||||

| 0 | 1 | 1 | 0 | 1 | 6 | ||||||

| 0 | 1 | 1 | 1 | 0 | 7 | ||||||

| 1 | 0 | 0 | 0 | 1 | 8 | ||||||

| 1 | 0 | 0 | 1 | 1 | 9 | ||||||

| 1 | 0 | 1 | 0 | X | X | ||||||

| 1 | 0 | 1 | 1 | X | X | ||||||

| 1 | 1 | 0 | 0 | X | X | ||||||

| 1 | 1 | 0 | 1 | X | X | ||||||

| 1 | 1 | 1 | 0 | X | X | ||||||

| 1 | 1 | 1 | 1 | X | X | ||||||

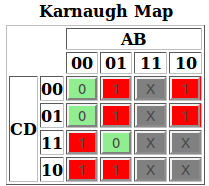

Mapa de Karnaugh

- Para implementar a minimização do Mapa de Karnaugh será utilizado o seguinte software.

- Primeiro, deve-se preencher a tabela verdade de acordo com o segmento g:

- O software preenche o Mapa de Karnaugh com a melhor minimização possível:

- Obtêm-se a expressão resultante do Mapa:

Inserindo a minimização do Mapa de Karnaugh no Quartus

- Crie um diretório com nome /home/aluno/bcd_ssd.

- Baixe o .qar do projeto e salve dentro do diretório criado.

- Execute o Quartus.

- Restaure o projeto: Project >> Restore Archived Project... > Archive Name: Selecione a pasta e o arquivo .qar anteriormente salvo >> OK.

- Será criada uma pasta 7-seg_restored. Esse será nosso diretório de trabalho.

- Compile o projeto.

- Note que apenas o segmento g está implementado.

- Monte os demais segmentos, seguindo este exemplo e baseado em seu projeto já relaizado.

- Associe o dispositivo a ser utilizado: Assignments >> Device >> Family=Cyclone e Avaliable Devices: EP1C3T100A8 ou Family: Cyclone IV E e Available Devices: EP4CE30F23C7 >> OK

- Compile o projeto.

- Associe os pinos (Assignments >> Assignment Editor) segundo um dos mapas: Interfaces de entrada e saída da DE2-115 ou kit MERCURIO IV - EP4CE30F23C7.

- Utilize quatro chaves (sw) como entrada BCD.

- Utilize um dos dois displays SSD como saída.

- Compile o projeto.

- Conecte a placa via USB.

- Faça a carga do código: Tools >> Programer >> Start.

- Verifique o funcionamento do conversor: altere o código BCD com as chaves de entrada e verifique a saída no display SSD.

Fazer a simulação funcional do circuito com o QSIM

- Após a implementação de todos os segmentos, realize teste funcional e verifique se o resultado obtido corresponde a respostas do circuito implementado.

- Abra o editor de forma de onda do simulador QSIM (File > New > University Programa VWF) (v 13.0 e 13.1).

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

- Desenhe a forma de onda dos sinais de entrada, simulando todas as combinações de uma tabela verdade de quatro entradas, ou seja, dos valores 0000 a 1111.

- Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK] (v. 13.0)

- Faça a simulação funcional do circuito lógico usando o sinal criado (Simulation > Run Functional Simulation)

- O resultado da simulação deve corresponder ao funcionamento do conversor BCD - SSD.

- Agrupe os sinais de entrada como RADIX "decimal não sinalizado". Para isso selecione os sinais [Edit > Grouping] [Group name = IN] > [Radix = Unsigned Decimal] > [OK].

- Tente visualizar o acendimento dos LEDs e a formação da representação dos respectivos números na saída.