|

|

| Linha 378: |

Linha 378: |

| | {{fig|1.8|Architetura do CPLD MAX 5000 da ALTERA| max_5000_architecture.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} | | {{fig|1.8|Architetura do CPLD MAX 5000 da ALTERA| max_5000_architecture.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} |

| | {{collapse bottom}} | | {{collapse bottom}} |

| − | * [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 1 e 2 | + | * [Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 1 e 2 |

| | | | |

| | :* Ver preços em | | :* Ver preços em |

Edição das 09h18min de 1 de março de 2024

Registro on-line das aulas

Unidade 1 - Aula inicial, Introdução a disciplina

| Unidade 1 - Aula inicial, Introdução a disciplina

|

- Encontro 1 (16 fev)

- A página da UC contém os materiais que não alteram entre semestre.

- Relação com as outras UCs do Eixo Sistemas Computacionais (Marrom). Ver grafo do curriculo

- ELD129002 - ELETRÔNICA DIGITAL I (ELD1): Sistema de numeração e códigos. Lógica booleana. Circuitos combinacionais. Circuitos aritméticos. Linguagem de descrição de hardware. Implementação e teste de circuitos digitais. Projeto de circuitos lógicos.

- ELD129003 - ELETRÔNICA DIGITAL II (ELD2): Dispositivos lógicos programáveis. Circuitos sequenciais. Metodologia síncrona. Projeto hierárquico e parametrizado. Máquinas de estados finita. Register Transfer Methodology. Teste de circuitos digitais. Implementação em FPGA. Introdução a Linguagem de Descrição de Hardware.

- AOC129004 - ARQUITETURA E ORGANIZAÇÃO DE COMPUTADORES (AOC): Introdução à Arquitetura Computadores. Linguagem Assembly. Linguagem de Máquina. Programação Assembly. Modos de Endereçamento. Processo de compilação e carga de um programa. Introdução à Organização de Computadores. Organização Monociclo e Multiciclo. Pipeline. Memória e Sistema de E/S.

- MIC129007 - MICROCONTROLADORES (MIC): Introdução a Microcontroladores e Aplicações. Arquitetura de um microcontrolador. Pilha e Subrotinas. Interrupção. Contadores e Temporizadores. Interface com Periféricos. Programação em alto nível (ex.: C, C++ e RUST) para Microcontroladores: Mapeamento de tipos e estruturas de alto nível para sistemas com recursos limitados. Projeto de hardware e firmware com microcontroladores.

- STE129008 - STE - SISTEMAS EMBARCADOS (STE): Conceitos em Sistemas Embarcados. Metodologia de Desenvolvimento de Sistemas Embarcados. Sistemas Operacionais para Sistemas Embarcados. Ferramentas de desenvolvimento e depuração. Barramentos e dispositivos de acesso a redes. Desenvolvimento de Projeto.

- Nesta página está o Registro diário dos encontros e avaliações.

- A entrega de atividades e avaliações será através da plataforma Moodle. A inscrição dos alunos é automática a partir do SIGAA.

- Para a comunicação entre professor-aluno, além dos avisos no SIGAA, utilizaremos o chat institucional. A princípio todos os alunos já estão previamente cadastrados pelo seu email institucional. Confiram enviando uma mensagem de apresentação.

- Utilizaremos durante as aulas algumas ferramentas computacionas como o site do Falstad para entender circuitos digitais e fazer simulações básicas.

- Também utilizaremos os softwares Quartus Light e ModelSim instalados nas maquinas do laboratório para praticar a parte de programação de hardware (descrição de hardware). Esses softwares também podem ser usados através da Nuvem do IFSC..

- LER PARA O PRÓXIMO ENCONTRO

- Revisão dos conceitos sobre circuitos combinacionais vistos em CIL/ELD1

- Para alunos que não cursaram ELD1 (não conhecem VHDL), irei fornecer uma sequência de estudos para conhecer melhor as instruções concorrentes do VHDL.

- Ler Introdução a linguagem de descrição de hardware (DHL)

|

Unidade REV - PRIMEIRO CONTATO COM VHDL

| Unidade REV - PRIMEIRO CONTATO COM VHDL

|

- Encontro 2 (20 fev)

- Declaração das bibliotecas e pacotes LIBRARY / PACKAGE

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

- PARA O PRÓXIMO ENCONTRO

- Para os alunos que são da matriz curricular 1290 (PPC 2023).

- Para conhecer um pouco mais da linguagem VHDL, ler VHDL ou VHDL.en. A maioria dessas instruções serão tratadas posteriormente.

- Encontro 3 (23 fev)

- Descrição do harware utilizando código VHDL no Quartus.

- Rever a IDE do Quartus

- Realizar análise e síntese.

- Obter Diagrama RTL e Technology Map do circuito

- Realizar simulação funcional com ModelSim

- Conhecer a IDE do ModelSim

- Seguir o procedimento descrito em Uso do ambiente EDA - QUARTUS Prime para programação em VHDL

- Encontro 4 (27 fev)

- Como arquivar um projeto

- Conhecer instruções WHEN_ELSE, WITH_SELECT, CONFIGURATION

Para ilustrar essas instruções utilizaremos o exemplo de um Mux4x1. Um multiplexador digital de N entradas e 1 saída, frequentemente abreviado como MUX N:1, é um circuito digital muito utilizado para rotear sinais digitais. Ele desempenha a função de selecionar uma das entradas para ser encaminhada para a saída com base em um sinal de seleção (ou controle).

| Mux2x1

|

|

A tabela verdade que descreve um MUX2:1 é mostrada abaixo:

| X1

|

X0

|

Sel

|

Y

|

| 0

|

0

|

0

|

0

|

| 0

|

0

|

1

|

0

|

| 0

|

1

|

0

|

1

|

| 0

|

1

|

1

|

0

|

| 1

|

0

|

0

|

0

|

| 1

|

0

|

1

|

1

|

| 1

|

1

|

0

|

1

|

| 1

|

1

|

1

|

1

|

O MUX2:1 também pode ser representado de forma resumida por:

| X1

|

X0

|

Sel

|

Y

|

| -

|

X0

|

0

|

X0

|

| X1

|

-

|

1

|

X1

|

Onde o X0 e X1 na entrada podem assumir os valores 0 ou 1, e o simbolo "-" corresponde ao don't care (em VDHL)

A função booleana que descreve a operação de um MUX 2:1 pode ser representada da seguinte forma:

Onde Y é a saída; Sel é o sinal de seleção; X0 e X1 são as entradas.

|

| Mux4x1

|

|

O MUX4:1 pode ser representado de forma resumida pela tabela verdade:

| Entradas

|

Seleção

|

Saída

|

| X3

|

X2

|

X1

|

X0

|

Sel1

|

Sel0

|

Y

|

| -

|

-

|

-

|

X0

|

0

|

0

|

X0

|

| -

|

-

|

X1

|

-

|

0

|

1

|

X1

|

| -

|

X2

|

-

|

-

|

1

|

0

|

X2

|

| X3

|

-

|

-

|

-

|

1

|

1

|

X3

|

A função booleana que descreve a operação de um MUX 4:1 pode ser representada da seguinte forma:

|

Dada a função booleana do MUX4:1 é simples para descreve-lo em VHDL utilizando apenas operadores lógicos.

entity mux4x1 is

port

(

-- Input ports

X: in bit_vector (3 downto 0);

Sel : in bit_vector (1 downto 0);

-- Output ports

Y : out bit

);

end entity;

-- Implementação com lógica pura

architecture v_logica_pura of mux4x1 is

begin

Y <= (X(0) and (not Sel(1)) and (not Sel(0))) or

...

end architecture;

No entanto, o MUX4:1 também pode ser descrito utilizando a instrução WHEN-ELSE

<optional_label>: <target> <=

<value> when <condition> else

<value> when <condition> else

...

<value> else

<value>;

- Importante: O último ELSE sem condição para cobrir todos os demais valores para evitar a criação de LATCHES.

Warning (13012): Latch ... has unsafe behavior

- No QuartusII existe um template pronto para ser utilizado em: [Edit > Insert Template > Language templates = VHDL (+) > Constructs (+) > Concurrent Statemens (+) > Conditional Signal Assignment]

No caso do MUX4:1 ele poderia ser descrito como:

-- Implementação com WHEN ELSE

architecture v_WHEN_ELSE of mux4x1 is

begin

Y <= X(0) when Sel = "00" else

X(1) when Sel = "01" else

X(2) when Sel = "10" else

X(3);

end architecture;

Outra forma de descrever o MUX4:1 seria utilizando a instrução WITH-SELECT

<optional_label>: with <expression> select

<target> <=

<value> when <choices>,

<value> when <choices>,

...

<value> when others;

- Importante: Para cobrir todas as demais possibilidades deve ser utilizado o WHEN OTHERS evitando novamente a criação de LATCHES, ou erros de análise.

Error (10313): VHDL Case Statement error ...: Case Statement choices must cover all possible values of expression

- No QuartusII existe um template pronto para ser utilizado em: [Edit > Insert Template > Language templates = VHDL (+) > Constructs (+) > Concurrent Statemens (+) > Selected Signal Assignment]. Mas ATENÇÃO, faltam as virgulas após cada escolha.

-- Implementação com WITH SELECT

architecture v_WITH_SELECT of mux4x1 is

begin

with Sel select

Y <= X(0) when "00", -- note o uso da ,

X(1) when "01",

X(2) when "10",

X(3) when others; -- note o uso de others, para todos os demais valores.

-- Não pode ser substituido por "11" mesmo que o signal seja bit_vector.

end architecture;

- Note que para associar uma entre várias arquiteturas com a sua ENTITY pode-se utilizar a instrução CONFIGURATION. No exemplo abaixo a ARCHITECTURE que está descomentada é a que será associada a ENTITY mux4x1.

- Caso não se use a instrução CONFIGURATION, a última ARCHITECTURE será associada a ENTITY.

- Apesar de apenas uma das ARCHITECTUREs ser associada, todas elas devem estar sintaticamente corretas, pois passarão pelo processo de ANÁLISE E SINTESE.

CONFIGURATION <configuration_name> OF <entity_name> IS

FOR <architecture_name> END FOR;

END CONFIGURATION;

-- Design Unit que associa a architecture com a entity

CONFIGURATION cfg_ifsc OF mux4x1 IS

FOR v_logica_pura END FOR;

-- FOR v_WHEN_ELSE END FOR;

-- FOR v_WITH_SELECT END FOR;

END CONFIGURATION;

- Faça a análise e sintese do mux4x1, associando a architecture v_logica_pura, depois v_WITH_SELECT, depois v_WHEN e por último v_IF_ELSE.

- Note a diferença entre os RTL Viewer obtidos para cada architecture.

Figura 2.1 - Código RTL do mux4x1 v_logica_pura

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura 2.2 - Código RTL do mux4x1 v_WHEN_ELSE

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura 2.3 - Código RTL do mux4x1 v_WITH_SELECT

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- OBS: Register Transfer-Level (RTL) é uma abstração na qual o circuito é descrito em termos de fluxo de sinais entre os registradores presentes no hardware e as operações combinacionais realizadas com esses dados.

- PARA O PRÓXIMO ENCONTRO

- Realize a simulação das 3 arquiteturas do MUX4:1 no Modelsim

- Crie um arquivo tb_mux4x1_v1.do que repita a simulação da arquitetura v1

- Crie um arquivo tb_mux4x1_v2.do que repita a simulação da arquitetura v2

- Crie um arquivo tb_mux4x1_v3.do que repita a simulação da arquitetura v1

- Inclua todos os arquivos .do no projeto do Quartus e salve o arquivo QAR

- Ver essa página Simulação Funcional usando o ModelSim

|

Unidade REV - PRIMEIRO CONTATO COM VHDL

| Unidade REV - PRIMEIRO CONTATO COM VHDL

|

ATUAL

- Encontro 5 (1 mar)

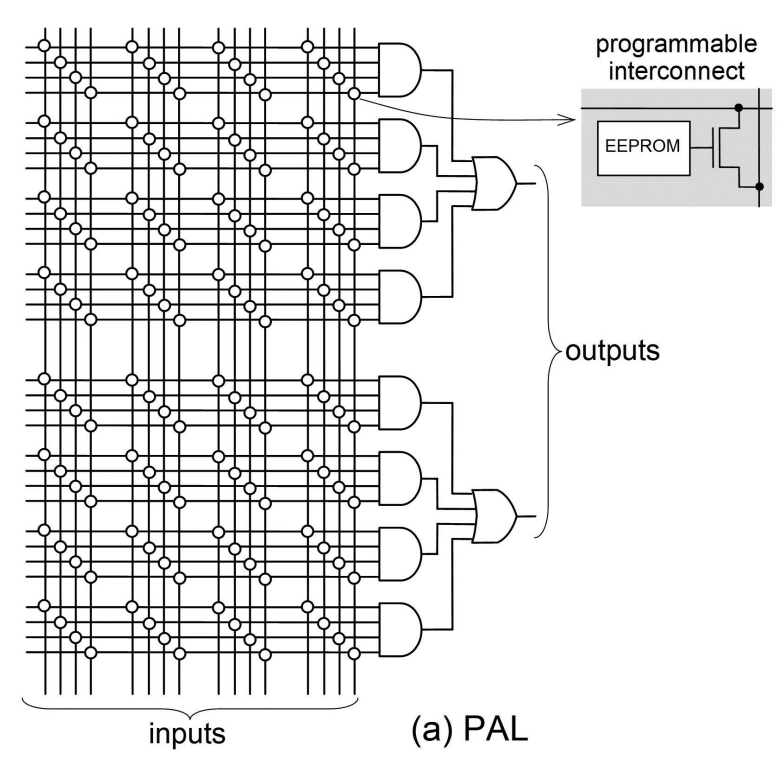

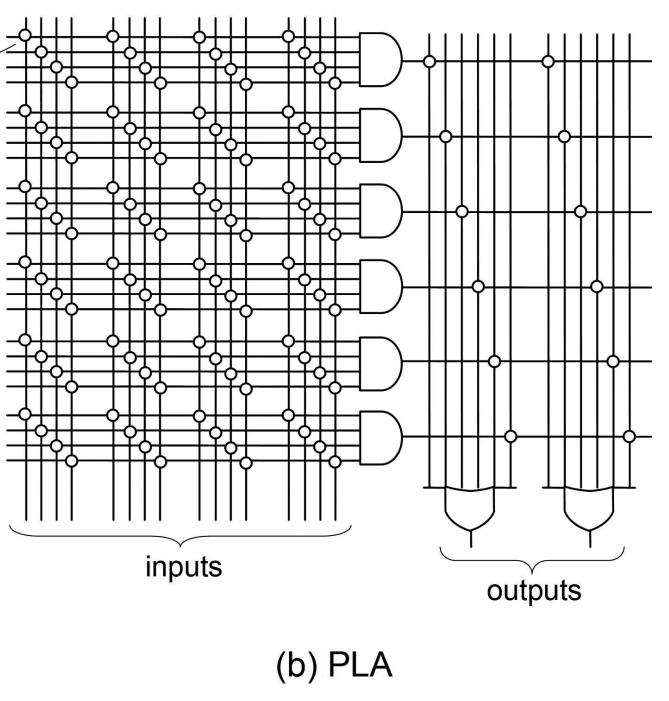

- Introdução aos dispositivos lógicos programáveis:

- Conceito, tipos de PLDs

- SPLD:

- [Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 1 e 2

-

- Fabricantes de DLPs/FPGAs e familias de DLPs atuais.

- PARA O PRÓXIMO ENCONTRO

|

Avaliações

Durante o semestre serão realizadas 4 avaliações. As avaliações devem ser enviadas pela plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - :

- A2 - :

- A3 - :

- A4 - :

- R - Recuperação de A1 a A4 :

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN.

A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN. Para os BÔNUS só serão considerados projetos entregues no prazo.

Referências Bibliográficas:

Curso de Engenharia de Telecomunicações