Mudanças entre as edições de "ELD129003-Engtelecom (Diário) - Prof. Marcos Moecke"

(→ATUAL) |

|||

| Linha 26: | Linha 26: | ||

===Unidade REV - PRIMEIRO CONTATO COM VHDL === | ===Unidade REV - PRIMEIRO CONTATO COM VHDL === | ||

| − | * | + | * 3 ENCONTROS |

{{collapse top | expand=true | Unidade REV - PRIMEIRO CONTATO COM VHDL}} | {{collapse top | expand=true | Unidade REV - PRIMEIRO CONTATO COM VHDL}} | ||

| Linha 85: | Linha 85: | ||

*Conhecer a IDE do ModelSim | *Conhecer a IDE do ModelSim | ||

*Seguir o procedimento descrito em [[Uso do ambiente EDA - QUARTUS Prime para programação em VHDL]] | *Seguir o procedimento descrito em [[Uso do ambiente EDA - QUARTUS Prime para programação em VHDL]] | ||

| − | + | ||

;Encontro 4 (27 fev): | ;Encontro 4 (27 fev): | ||

;[[Como arquivar um projeto]]: | ;[[Como arquivar um projeto]]: | ||

| Linha 344: | Linha 344: | ||

*Inclua todos os arquivos .do no projeto do Quartus e salve o arquivo QAR | *Inclua todos os arquivos .do no projeto do Quartus e salve o arquivo QAR | ||

*Ver essa página [[Simulação Funcional usando o ModelSim]] | *Ver essa página [[Simulação Funcional usando o ModelSim]] | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | |||

| + | ===Unidade REV - PRIMEIRO CONTATO COM VHDL === | ||

| + | * 3 ENCONTROS | ||

| + | {{collapse top | expand=true | Unidade REV - PRIMEIRO CONTATO COM VHDL}} | ||

| + | |||

| + | ====ATUAL==== | ||

| + | ;Encontro 5 (1 mar): | ||

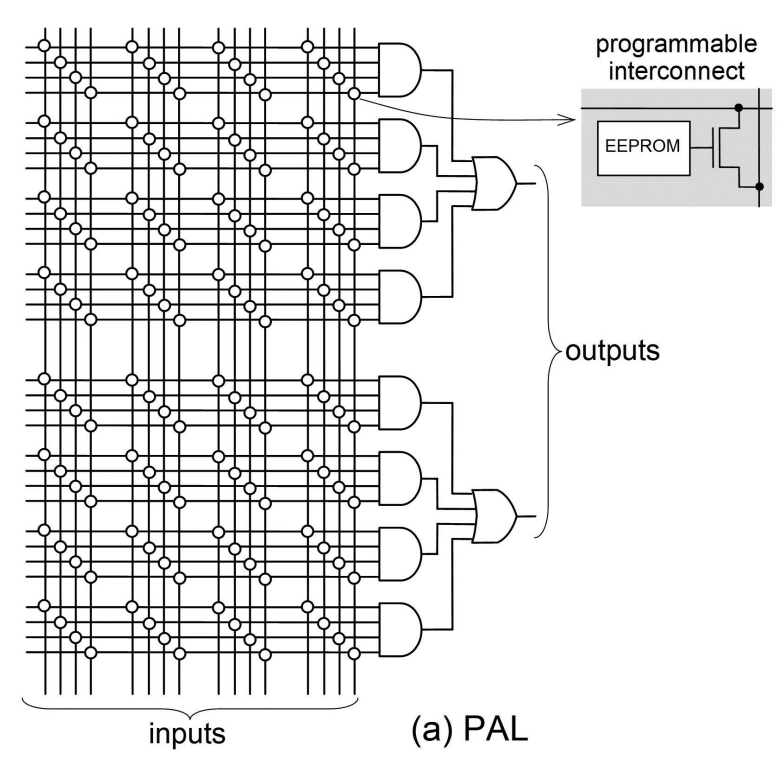

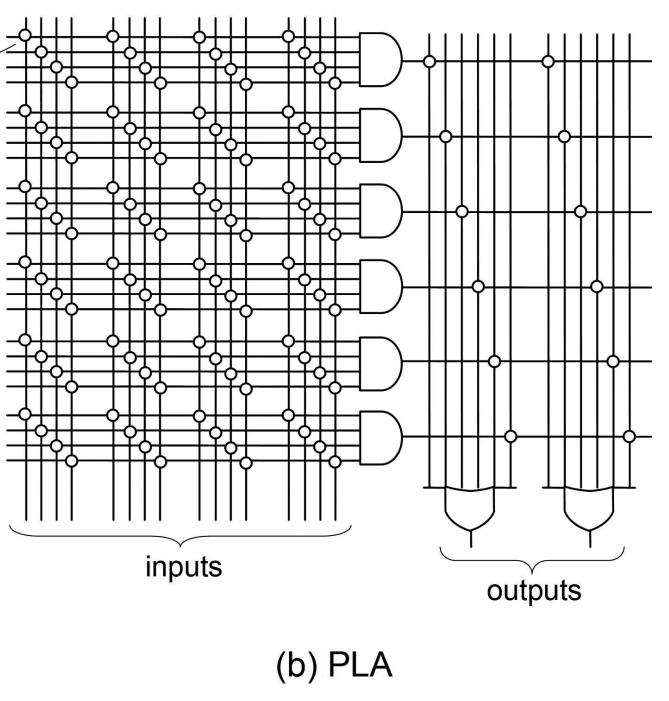

| + | *Introdução aos dispositivos lógicos programáveis: | ||

| + | :* Conceito, tipos de PLDs | ||

| + | :* SPLD: | ||

| + | ::*PAL (e.g. [[Media: PAL16.pdf| PAL16 da Texas Instruments (1984)]]) | ||

| + | ::*PLA (e.g. [[Media: PLS100.pdf| PLS100 da Philips Semiconductors (1993)]]) | ||

| + | ::*GAL (e.g. [[Media: GAL16V8.pdf| GAL16V8 da Lattice (2004)]]) | ||

| + | :* CPLDs (e.g. [[Media: ATF2500C.pdf| ATF2500C da Atmel (2008)]], [https://br.mouser.com/c/ds/semiconductors/programmable-logic-ics/cpld-complex-programmable-logic-devices/ Complex Programmable Logic Devices Datasheets - Mouser]) | ||

| + | |||

| + | {{collapse top | expand=true| Exemplos de PLDs}} | ||

| + | {{fig|1.1|Exemplo de PAL| PedroniFig4_4a.png| 400 px | http://www.vhdl.us/book/Pedroni_VHDL_3E_Chapter4.pdf}} | ||

| + | |||

| + | {{fig|1.2|Exemplo de PLA| PedroniFig4_4b.png| 400 px | http://www.vhdl.us/book/Pedroni_VHDL_3E_Chapter4.pdf}} | ||

| + | |||

| + | {{fig|1.3|Macrobloco do PLD EP300 da ALTERA| ep310_macrocell.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} | ||

| + | |||

| + | {{fig|1.4|Macrocélula dos PLDs Clássicos EP600, EP900, EP1800 da ALTERA (1999)| Macrocell_EP900.png| 400 px | https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ds/archives/classic.pdf}} | ||

| + | |||

| + | {{fig|1.5|Architetura do PLD EP1800 da ALTERA| ep1800_block_diagram.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} | ||

| + | |||

| + | {{fig|1.6|Architetura do PLD EP1800 da ALTERA| ep1800_block_diagram2.jpg| 400 px | https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ds/archives/classic.pdf}} | ||

| + | |||

| + | {{fig|1.7|Pinagem e tipos de encapsulamento do PLD EP1800 da ALTERA| PackagePinOut_EP1810.png| 400 px | https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ds/archives/classic.pdf }} | ||

| + | |||

| + | {{fig|1.8|Architetura do CPLD MAX 5000 da ALTERA| max_5000_architecture.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} | ||

| + | {{collapse bottom}} | ||

| + | * [https://wiki.sj.ifsc.edu.br/index.php/DLP29006-Engtelecom_(Di%C3%A1rio)_-_Prof._Marcos_Moecke#AE2_-_Conhecendo_os_dispositivos_l.C3.B3gicos_program.C3.A1veis Laboratório AE2 - Conhecendo os dispositivos lógicos programáveis] - Passo 1 e 2 | ||

| + | |||

| + | :* Ver preços em | ||

| + | ::*[https://www.arrow.com/ ARROW] | ||

| + | ::*[https://www.digikey.com/ Digikey] | ||

| + | ::*[https://mouser.com Mouser Electronics] | ||

| + | ::*[https://www.newark.com/ Newark] | ||

| + | :* Fabricantes de DLPs/FPGAs e familias de DLPs atuais. | ||

| + | ::*[https://www.altera.com/products/fpga/overview.html ALTERA/INTEL] - Stratix, Arria, Cyclone, Max | ||

| + | ::*[https://www.xilinx.com/products/silicon-devices/fpga.html Xilinx/AMD] - Virtex, Kintex, Artix, Zynq (SoC) | ||

| + | ::*[https://www.microchip.com/en-us/products/fpgas-and-plds/fpgas Microchip] - Igloo, PolarFire | ||

| + | ::*[http://www.latticesemi.com/Products.aspx#_D5A173024E414501B36997F26E842A31 Lattice] - ECP, iCE, Mach | ||

| + | |||

| + | ;PARA O PRÓXIMO ENCONTRO: | ||

| + | *[https://www.intel.com/content/www/us/en/products/details/fpga/platforms.html See why Microsoft chose Intel FPGAs to accelerate their next generation cloud infrastructure] | ||

| + | *[https://www.youtube.com/watch?v=ecyyZ6zTLic Microsoft's Bing* Intelligent Search with Intel® FPGAs] | ||

| + | *Seção 4.1 a 4.5 de [http://www.vhdl.us/book/Pedroni_VHDL_3E_Chapter4.pdf Review of Field Programmable Gate Arrays (FPGAs)], Volnei A. Pedroni. (ou para quem preferir em português, leia as seções 18.1 a 18.3 do livro: PEDRONI, Volnei A '''Eletrônica Digital Moderna e VHDL: Princípios Digitais, Eletrônica Digital, Projeto Digital, Microeletrônica e VHDL'''; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. ISBN 9788535234657. Têm 16 exemplares na [http://biblioteca.ifsc.edu.br/index.asp?codigo_sophia=30631 biblioteca do Campus]. Número de chamada: 621.392 P372e) | ||

| + | *Seção 2.1 Dispositivos lógicos programáveis do TCC [[Integração de ramais analógicos com FPGA utilizando processador softcore]], Renan Rodolfo da Silva. | ||

{{collapse bottom}} | {{collapse bottom}} | ||

Edição das 09h16min de 1 de março de 2024

Registro on-line das aulas

Unidade 1 - Aula inicial, Introdução a disciplina

- 1 ENCONTRO

| Unidade 1 - Aula inicial, Introdução a disciplina |

|---|

|

Unidade REV - PRIMEIRO CONTATO COM VHDL

- 3 ENCONTROS

| Unidade REV - PRIMEIRO CONTATO COM VHDL | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

Para ilustrar essas instruções utilizaremos o exemplo de um Mux4x1. Um multiplexador digital de N entradas e 1 saída, frequentemente abreviado como MUX N:1, é um circuito digital muito utilizado para rotear sinais digitais. Ele desempenha a função de selecionar uma das entradas para ser encaminhada para a saída com base em um sinal de seleção (ou controle).

Dada a função booleana do MUX4:1 é simples para descreve-lo em VHDL utilizando apenas operadores lógicos. entity mux4x1 is

port

(

-- Input ports

X: in bit_vector (3 downto 0);

Sel : in bit_vector (1 downto 0);

-- Output ports

Y : out bit

);

end entity;

-- Implementação com lógica pura

architecture v_logica_pura of mux4x1 is

begin

Y <= (X(0) and (not Sel(1)) and (not Sel(0))) or

...

end architecture;

No entanto, o MUX4:1 também pode ser descrito utilizando a instrução WHEN-ELSE <optional_label>: <target> <=

<value> when <condition> else

<value> when <condition> else

...

<value> else

<value>;

Warning (13012): Latch ... has unsafe behavior

No caso do MUX4:1 ele poderia ser descrito como: -- Implementação com WHEN ELSE

architecture v_WHEN_ELSE of mux4x1 is

begin

Y <= X(0) when Sel = "00" else

X(1) when Sel = "01" else

X(2) when Sel = "10" else

X(3);

end architecture;

Outra forma de descrever o MUX4:1 seria utilizando a instrução WITH-SELECT <optional_label>: with <expression> select

<target> <=

<value> when <choices>,

<value> when <choices>,

...

<value> when others;

Error (10313): VHDL Case Statement error ...: Case Statement choices must cover all possible values of expression

-- Implementação com WITH SELECT

architecture v_WITH_SELECT of mux4x1 is

begin

with Sel select

Y <= X(0) when "00", -- note o uso da ,

X(1) when "01",

X(2) when "10",

X(3) when others; -- note o uso de others, para todos os demais valores.

-- Não pode ser substituido por "11" mesmo que o signal seja bit_vector.

end architecture;

CONFIGURATION <configuration_name> OF <entity_name> IS

FOR <architecture_name> END FOR;

END CONFIGURATION;

-- Design Unit que associa a architecture com a entity

CONFIGURATION cfg_ifsc OF mux4x1 IS

FOR v_logica_pura END FOR;

-- FOR v_WHEN_ELSE END FOR;

-- FOR v_WITH_SELECT END FOR;

END CONFIGURATION;

Figura 2.1 - Código RTL do mux4x1 v_logica_pura  Figura 2.2 - Código RTL do mux4x1 v_WHEN_ELSE  Figura 2.3 - Código RTL do mux4x1 v_WITH_SELECT

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Unidade REV - PRIMEIRO CONTATO COM VHDL

- 3 ENCONTROS

| Unidade REV - PRIMEIRO CONTATO COM VHDL |

|---|

ATUAL

|

Avaliações

Durante o semestre serão realizadas 4 avaliações. As avaliações devem ser enviadas pela plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - :

- A2 - :

- A3 - :

- A4 - :

- R - Recuperação de A1 a A4 :

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN.

Atividade extra-classe (AE)

A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN. Para os BÔNUS só serão considerados projetos entregues no prazo.

Referências Bibliográficas: