Mudanças entre as edições de "ELD129002-Engtelecom (Diário) - Prof. Marcos Moecke"

(→ATUAL) |

(→ATUAL) |

||

| Linha 1 192: | Linha 1 192: | ||

;Encontro 18 (28 set) - Linguagem VHDL (cont): | ;Encontro 18 (28 set) - Linguagem VHDL (cont): | ||

*Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/262427/mod_resource/content/1/Introdu%C3%A7%C3%A3o%20a%20linguagem%20de%20descri%C3%A7%C3%A3o%20de%20hardware.pdf Introdução a linguagem de descrição de hardware (DHL)] | *Ver resumo em [https://moodle.ifsc.edu.br/pluginfile.php/262427/mod_resource/content/1/Introdu%C3%A7%C3%A3o%20a%20linguagem%20de%20descri%C3%A7%C3%A3o%20de%20hardware.pdf Introdução a linguagem de descrição de hardware (DHL)] | ||

| − | *Uso do | + | |

| + | * Estrutura do código VHDL | ||

| + | :* Declaração das bibliotecas e pacotes '''LIBRARY''' / '''PACKAGE''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | library library_name; | ||

| + | use library_name.package_name.all; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :* '''ENTITY''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity entity_name is | ||

| + | [generic ( | ||

| + | cons_name1: const_type const_value; | ||

| + | cons_name2: const_type const_value; | ||

| + | ... | ||

| + | cons_nameN: const_type const_value);] | ||

| + | [port ( | ||

| + | signal_name1: mode signal_type; | ||

| + | signal_name2: mode signal_type; | ||

| + | ... | ||

| + | signal_nameN: mode signal_type);] | ||

| + | [declarative_part] | ||

| + | [begin | ||

| + | statement_part] | ||

| + | end [entity] [entity_name]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :* '''ARCHITECTURE''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | architecture arch_name of entity_name is | ||

| + | [declarative_part] | ||

| + | begin | ||

| + | statement_part | ||

| + | end [architecture] [arch_name]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | * Exemplo - Declaração de uma porta NAND em VHDL | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | library std; | ||

| + | use std.standard.all; | ||

| + | |||

| + | entity nand_gate is | ||

| + | port (a, b: in bit; x: out bit); | ||

| + | end entity; | ||

| + | |||

| + | architecture nome_arch of nand_gate is | ||

| + | begin | ||

| + | x <= a nand b; | ||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | *Uso do ambiente EDA - QUARTUS Prime para programação em VHDL. | ||

| + | ;PASSO 0: | ||

| + | [[Acesso ao IFSC-CLOUD (NUVEM) | Acesse a nuvem do IFSC]] usando um terminal via ssh: | ||

| + | USER=LOGIN_SIGAA | ||

| + | ssh $USER@quartus.sj.ifsc.edu.br -XC | ||

| + | Insira a senha do SIGAA | ||

| + | LOGIN_SIGAA@quartus.sj.ifsc.edu.br's password: | ||

| + | |||

| + | ;PASSO 1: | ||

| + | Abra o Quartus Prime digitando no terminal | ||

| + | quartus20.1.sh | ||

| + | Em seguida abra um arquivo para inserir o código VHDL. No menu superior selecione '''[File > New > Design Files: VHDL File]''' e '''[OK]''' | ||

| + | |||

| + | ;PASSO 2: | ||

| + | *Copie o código VHDL acima para o espaço de edição e salve o arquivo com o nome da '''entity''': ''nand_gate.vhd'', em um pasta exclusiva para este projeto. | ||

| + | *Ao ser perguntado se deseja criar um novo projeto, responda [Yes]. Os próximos passos podem ser realizados da seguinte forma: | ||

| + | :*Na tela '''Introduction''' [Next >] | ||

| + | :*Na tela '''Directory, Name, Top-Level Entity''' | ||

| + | ::*Note onde o projeto será salvo. | ||

| + | /home/USER/PASTA_DO_PROJETO/ | ||

| + | ::*Note o nome do projeto. Se quiser pode mudá-lo | ||

| + | nand_gate | ||

| + | ::*Note o nome da '''top-level design entity''' | ||

| + | nand_gate | ||

| + | ::*Em seguida [Next >] | ||

| + | :*Na tela '''Project Type''' [Next >] | ||

| + | :*Na tela '''Add Files''' [Next >], pois seu arquivo já está na lista dos arquivos. | ||

| + | :*Na tela '''Family, Device & Board Settings''', escolha a Family = ['''Cyclone IV E'''] e o Device = ['''EP4CE6E22A7'''] e [Next >] | ||

| + | :*Na tela '''EDA Tool Setting''' [Next >] | ||

| + | :*Note na tela Summary os dados do projeto e clique [Finish] | ||

| + | |||

| + | ;PASSO 3: | ||

| + | Realize a '''Analysis & Synthesis''' ['''Processing > Start > Start Analysis & Synthesis'''], ou use um dos botões que o professor mostrou em aula. | ||

| + | :*Note o '''Compilation Report''' | ||

| + | |||

| + | ;PASSO 4: | ||

| + | *Use o [[RTL Viewer]] para ver a descrição RTL do circuito. | ||

| + | *Use o [[Technology Map Viewer]] para ver a como o circuito foi mapeado para os elementos lógicos disponíveis no dispositivo FPGA selecionado | ||

| + | |||

| + | ;PASSO 5: | ||

| + | *Modifique a descrição do circuito para implementar o circuito da função | ||

| + | Y = (A.B)' + C.D'B' | ||

{{collapse bottom}} | {{collapse bottom}} | ||

Edição das 22h55min de 27 de setembro de 2023

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

| Unidade 1 - Introdução a disciplina | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

O ser humano precisa contar para determinar quantidades de coisas, com as quantidades ele pode fazer operações matemáticas e comparações.

Ler mais sobre Byte e os prefixos binários na Wikipedia

13 (decimal) = 01101 (binário sem sinal) -13 (decimal) = 10010 (binário em complemento de um) -13 (decimal) = 10010 + 1 = 10011 (binário em complemento de dois) -13 (decimal) = 11101 (binário em sinal-magnitude)

O código ASCII (American Standard Code for Information Interchange), é um padrão de codificação de caracteres para comunicação digital. Ele tem apenas 128 pontos de código, sendo 95 são caracteres imprimíveis e os demais são não imprimíveis (em azul no quadro abaixo), sendo usados para diversos controles de equipamentos eletrônicos. Atualmente esse código está sendo substituido pelos códigos UNICODE, que tem milhões de pontos de código, mas nos UNICODE os primeiros 128 são iguais ao conjunto ASCII.

Exemplo de leitura do quadro acima:

Descubra o que está escrito em: 45 6e 67 74 65 6c 65 63 6f 6d 20 64 6f 20 49 46 53 43 20 01000010 01101111 01101101 00100000 01100100 01101001 01100001 00100000 01110000 01100101 01110011 01110011 01101111 01000001 01001100 01001100

O Unicode é capaz de representar uma ampla variedade de caracteres, incluindo caracteres alfabéticos, numéricos, símbolos, caracteres especiais e até mesmo caracteres em idiomas e sistemas de escrita complexos, como chinês, árabe, hindi, hebraico, japonês, emojis entre outros. O Unicode possui um espaço de codificação grande o suficiente para suportar milhares de caracteres diferentes. O Unicode é implementado nos esquemas de codificação UTF-8, UTF-16 e UTF-32. O mais utilizado na web é o UTF-8, por ser eficiente em uso de número de bits e ser compatível com o ASCII. Hoje em dia o UTF-8 é usado em 98% de todos os websites conhecidos [1]. Para cobrir uma vasta gama de caracteres, o Unicode os organiza em blocos. Exemplos de blocos: "Latin basic","Greek and Coptic", "Chess Symbols", "Emoticons", "Mayan Numerals", etc.

Exemplo: Estender o número binário sem sinal de 5 bits "01101" para 8 bits: Número original: 01101 = (13 em decimal), pois 8 + 4 + 1 = 13 Número estendido: 00001101 = (13 em decimal), pois 8 + 4 + 1 = 13

Exemplo: Estender o número binário com sinal em complemento de 2 de 5 bits "10011" para 8 bits: Número original: 10011 = (-13 em decimal), pois -16 + 2 + 1 = -13 Número estendido: 11110011 = (-13 em decimal), pois -128 + 64 + 32 + 16 + 2 + 1 = -13

Exemplo: Estender o número binário com sinal em sinal-magnitude de 5 bits "10011" para 8 bits: Número original: 11101 = (-13 em decimal), pois -(+8 + 4 + 1) = -13 Número estendido: 10001101 = (-13 em decimal), pois -(+8 + 4 + 1) = -13

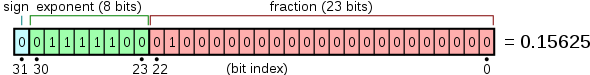

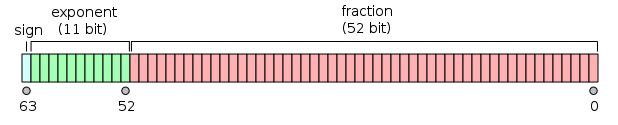

Os números de ponto flutuante são agrupados da esquerda para a direita:1) bit de sinal, 2) expoente e 3) mantissa. Para os formatos binários IEEE 754 (básico e estendido) que possuem implementações de hardware existentes, eles são distribuídos da seguinte forma:

Embora o expoente possa ser positivo ou negativo, em formatos binários ele é armazenado como um número sem sinal que possui um "viés" fixo adicionado a ele. A faixa de expoente para números normais é [−126, 127] para precisão simples, [−1022, 1023] para dupla. Existem três tipos principais de números: normalizados, denormalizados (ou desnormalizados) e especiais (como infinito e NaN - "Not a Number"). Nos formatos IEEE, o bit 1 inicial de um significando normalizado não é realmente armazenado. É chamado de bit "oculto" ou "implícito". Por causa disso, o formato de precisão simples na verdade tem um significando com 24 bits de precisão, o formato de precisão dupla tem 53. O layout para o ponto flutuante de 32 bits e de 64 bits são mostrados abaixo:

Exemplo: Dado o número floating point de 32 bits = 01000000111000000000000000000000 Sinal (msb): 0 => positivo Viés: (28-1 - 1) = -127 Expoente (8 bits): 10000001 = 129 - 127 = 2 Mantissa: (23 bits): 11000000000000000000000 Valor (24 bits): 1.11000000000000000000000 = 1,75 Resultado: (-) 1,75 x 22 = 7

Os números denormalizados não usam um "1" implícito no início da mantissa, ao contrário dos números normalizados. Isso significa que a mantissa dos números denormalizados começa com um "0" explícito antes da parte fracionária, permitindo representar valores muito pequenos que não podem ser normalizados devido à limitação dos bits do expoente.

Bit de sinal: 0 (positivo) Expoente: Todos os bits definidos como 1 (8 bits) Mantissa: Todos os bits definidos como 0 (23 bits) Representação em 32 bits: 0 11111111 00000000000000000000000

Bit de sinal: 1 (negativo) Expoente: Todos os bits definidos como 1 (8 bits) Mantissa: Todos os bits definidos como 0 (23 bits) Representação em 32 bits: 1 11111111 00000000000000000000000

Bit de sinal: Pode ser 0 ou 1 (geralmente usado para sinalizar erros ou operações indefinidas) Expoente: Todos os bits definidos como 1 (8 bits) Mantissa: Pelo menos um bit não nulo (23 bits) Representação: x 11111111 yyyyyyyyyyyyyyyyyyyyyyy (onde "x" é o bit de sinal e "y" são bits da mantissa)

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Unidade 2 - Funções, portas lógicas e algebra booleana

| Unidade 2 - |

|---|

ATUAL

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

Acesse a nuvem do IFSC usando um terminal via ssh: USER=LOGIN_SIGAA ssh $USER@quartus.sj.ifsc.edu.br -XC Insira a senha do SIGAA LOGIN_SIGAA@quartus.sj.ifsc.edu.br's password:

Abra o Quartus Prime digitando no terminal quartus20.1.sh Em seguida abra um arquivo para inserir o código VHDL. No menu superior selecione [File > New > Design Files: VHDL File] e [OK]

/home/USER/PASTA_DO_PROJETO/

nand_gate

nand_gate

Realize a Analysis & Synthesis [Processing > Start > Start Analysis & Synthesis], ou use um dos botões que o professor mostrou em aula.

Y = (A.B)' + C.D'B' |

Avaliações

Durante o semestre serão realizadas 4 avaliações. As avaliações devem ser enviadas pela plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - : dia XX/XX

- A2 - : dia XX/XX

- A3 - : dia XX/XX

- A4 - : dia XX/XX

- PF - Entrega do projeto final: dia XX/12

- R - Recuperação de A1 a A4 : dia XX/12

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN.

Atividade extra-classe (AE)

A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN. Para os BÔNUS só serão considerados projetos entregues no prazo.

Referências Bibliográficas:

![{\displaystyle [0,2^{N}-1]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/f5eb25a6a539bf3a9955017f5aba01160cdc022b)

![{\displaystyle [0,2^{8}-1]=[0,255]=[00000000_{2},11111111_{2}]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/fb5be03ed649ead5e68cd72a508f2e35a85a9cd9)

![{\displaystyle [-(2^{N-1}-1),(2^{N-1}-1(]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/a221d72e8db48e0485fc9c806eddebf90d025d8b)

![{\displaystyle [-(2^{8-1}-1),(2^{8-1}-1)]=[-(2^{7}-1),(2^{7}-1)]=[-127,-0,+0,+127]=[11111111_{2},10000000_{2},00000000_{2},01111111_{2}]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/3ee583c3440ece4c0754ca09cb58bcca0f94272f)

![{\displaystyle [-2^{N-1},2^{N-1}-1]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/98c77c4023c4f8693ba0abfb43664b86e21efda7)

![{\displaystyle [-2^{N-1},2^{N-1}-1]=[-128,0,+127]=[10000000_{2},00000000_{2},01111111_{2}]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/09a57011cf81984fda5df4a154f54e5e84d6bb6a)

![{\displaystyle [0,2^{M-F}-2^{-F}]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/031f01267eaa1c78218b276afbbbf48df80b6ea2)

![{\displaystyle [0;2^{5}-2^{-3}]=[0;31,875]=[00000,000_{2};11111,111_{2}]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/7c35daa9c5e766f28942844286e64b06a889c510)