EDI18701 2016 2 AULA08

Revisão de 10h40min de 25 de outubro de 2016 por Douglas (discussão | contribs) (→Esquemático dos CIs)

Laboratório 2

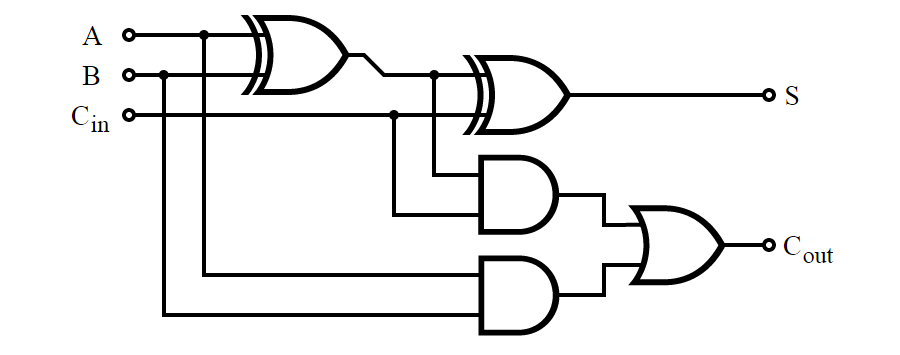

Um circuito somador de dois bits (half-adder) é um circuito combinatório que tem duas entradas, A e B, e produz duas saídas: o bit soma S e o bit de transporte Cout. Para se obter um somador de números em binário completo (full-adder) é necessário considerar um somador de dois bits A e B e um transporte Cin que produza um bit soma S e um transporte Cout. A Figura 1 mostra um esquema para o circuito somador de 3 bits.

Objetivo

- Realizar um experimento baseado em circuitos integrados discretos (TTL).

- Comprovar a tabela verdade para o circuito somador completo utilizando:

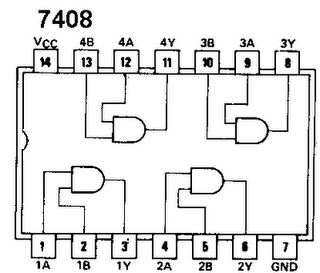

- Portas AND

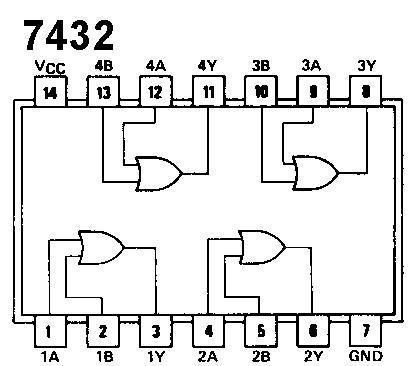

- Portas OR

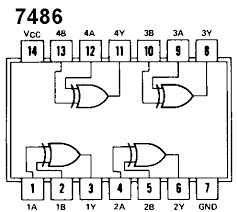

- Portas XOR

- Desenhar o diagrama de conexões a partir do modelo elétrico

- Montar os circuitos

- Fazer as ligação de VCC e GND de todos os CIs

- Conectar as entradas A, B e Cin nas chaves seletoras da bancada digital

- Conectar as saídas S e Cout nos LEDs

- Testar todas as possibilidades da tabela verdade e comprovar o seu funcionamento

Circuito Somador Completo

Figura 1 - Circuito Somador de 3 bits.

- Antes de iniciar o laboratório

[1] Determinar a equação da saída S do circuito do somador completo.

[2] Completar a sua tabela verdade.

Relatório

O relatório deverá ser entregue até a próxima aula 31/10/2016 (segunda-feira).

- Critérios para a avaliação do relatório simplificado

- Participação na aula prática: 1

- Montagem correta (organizada) e dentro do prazo: 1

- Esquema elétrico desenhado: 2

- Escrita legível e coerente: 2

- Conclusões, resultados e discussões: 4

Total: 10

Esquemático dos CIs

Referências

[1] https://www.dcc.fc.up.pt/~nam/aulas/0001/ic/boole/node8.html

| << | <> | >> |

|---|