Mudanças entre as edições de "EDI018702 2020 2 AULA03"

Ir para navegação

Ir para pesquisar

| (Uma revisão intermediária pelo mesmo usuário não está sendo mostrada) | |||

| Linha 1: | Linha 1: | ||

| − | = | + | =Laboratório 1= |

| − | |||

| − | + | O primeiro experimento da turma de Digital 2 do Técnico em Eletroeletrônica vai ser realizado no formato de ANP utilizando o ''software Proteus'' ou página/site do [https://www.falstad.com/circuit/ ''falstad'']. Os alunos terão que montar o circuito do Latch RS Controlado, na forma de blocos, - a partir das portas lógicas AND (E) e NOR (NOU), e simular o funcionamento comprovando o funcionamento através do correto preenchimento da tabela verdade. | |

| − | |||

| − | |||

| + | ==Latch RS Controlado== | ||

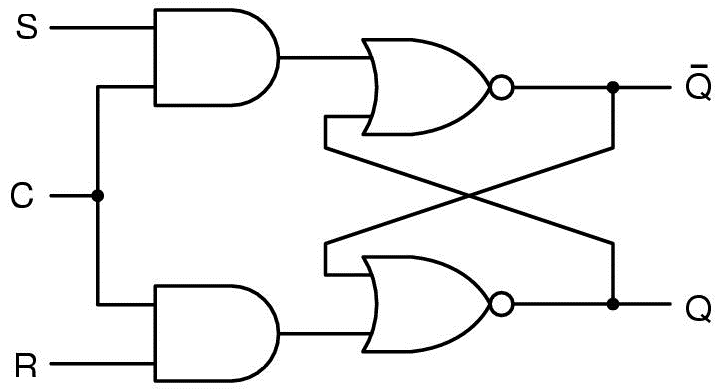

| − | + | ;Objetivo: Testar o funcionamento de um circuito Latch RS Controlado, feito a partir das portas lógicas AND (E) e NOR (NOU) como mostra a Figura 1. | |

| − | + | <br> | |

| − | + | [[Imagem:fig4_DIG222802.png|center|300px]] | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | [[Imagem: | ||

<center> | <center> | ||

| − | Figura | + | Figura 1 - Latch RS controlado. |

| + | <br> | ||

</center> | </center> | ||

| − | |||

| − | |||

| − | |||

| − | |||

{| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | {| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

| − | |+'''Tabela | + | |+'''Tabela Verdade''' |

|- | |- | ||

| − | |||

! style="background:#6A5ACD; color:white; width: 20px;" | C | ! style="background:#6A5ACD; color:white; width: 20px;" | C | ||

| − | ! style="background:#6A5ACD; color:white; width: 20px;" | | + | ! style="background:#6A5ACD; color:white; width: 20px;" | R |

| − | ! style="background:#6A5ACD; color:white; width: 20px;" | | + | ! style="background:#6A5ACD; color:white; width: 20px;" | S |

| − | ! style="background:#6A5ACD; color:white; width: 20px;" | | + | ! style="background:#6A5ACD; color:white; width: 20px;" | Q |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

|- | |- | ||

| − | |||

| 0 | | 0 | ||

| − | | | + | | X |

| − | | | + | | X |

| − | | | + | | |

| − | |||

|- | |- | ||

| − | |||

| 1 | | 1 | ||

| 0 | | 0 | ||

| 0 | | 0 | ||

| − | | | + | | |

| − | |||

|- | |- | ||

| − | |||

| 1 | | 1 | ||

| 0 | | 0 | ||

| 1 | | 1 | ||

| − | | | + | | |

| − | |||

|- | |- | ||

| − | |||

| 1 | | 1 | ||

| 1 | | 1 | ||

| 0 | | 0 | ||

| − | | | + | | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

|- | |- | ||

| − | |||

| − | |||

| − | |||

| − | |||

| 1 | | 1 | ||

| 1 | | 1 | ||

| − | |||

| − | |||

| − | |||

| 1 | | 1 | ||

| − | | | + | | |

| − | |||

| − | |||

|} | |} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | ==Procedimento== | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | #O trabalho é individual; | |

| + | #Desenhar as ligações utilizando o esquemático dos CIs; | ||

| + | #Desenhar o diagrama de pinagem de todos os CI utilizados (''pesquisar no datasheet''); | ||

| + | #Montar o circuito no software Proteus ou na página do ''falstad''; | ||

| + | ## Fazer a ligação entre as portas lógicas do circuito; | ||

| + | ## Fazer a ligação de R, S e C com entradas lógicas; | ||

| + | ## Fazer a ligação das Saídas Q e Q\ com saídas lógicas; | ||

| + | #Completar a Tabela Verdade. | ||

| − | + | ==Material Utilizado== | |

| − | + | * Listar qual o ''software'' que utilizou e se usou celular, tablet ou computador (PC, notebook, laptop). | |

| − | |||

| − | |||

| − | |||

| − | + | ==Relatório== | |

| − | + | O relatório simplificado deverá ser preenchido e postado em PDF no SIGAA dentro do prazo combinado para atividade. | |

| − | |||

| + | ;Critérios avaliativos: | ||

| − | + | ::Prática (montagem/equipe): 4 | |

| − | + | ::Circuito completo (todos): 3 | |

| − | + | ::Resultados e discussões : 3 | |

| − | |||

| + | ::'''Resultado''': 10 | ||

| − | + | =Referências= | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| + | [1] [https://www.falstad.com/circuit/ Circuito Simulador Applet - falstad] | ||

| − | + | [2] [https://www.google.com/url?sa=t&rct=j&q=&esrc=s&source=web&cd=&ved=2ahUKEwjRlcmokMbsAhXFILkGHTzsC_IQFjAAegQIAxAC&url=https%3A%2F%2Fwww.electroschematics.com%2Fwp-content%2Fuploads%2F2013%2F07%2F7408-datasheet.pdf&usg=AOvVaw0HaKh9sSFFcqEWaiubdCph Datasheet 7408] | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | == | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | [ | + | [3] [https://www.google.com/url?sa=t&rct=j&q=&esrc=s&source=web&cd=&ved=2ahUKEwi-nsfgkcbsAhVPDrkGHRf1Ce0QFjACegQIAhAC&url=http%3A%2F%2Fweb.mit.edu%2F6.131%2Fwww%2Fdocument%2F7402.pdf&usg=AOvVaw0Yow01v1-gtMs_xOjvXz2D Datasheet 7402] |

Edição das 14h05min de 23 de outubro de 2020

Laboratório 1

O primeiro experimento da turma de Digital 2 do Técnico em Eletroeletrônica vai ser realizado no formato de ANP utilizando o software Proteus ou página/site do falstad. Os alunos terão que montar o circuito do Latch RS Controlado, na forma de blocos, - a partir das portas lógicas AND (E) e NOR (NOU), e simular o funcionamento comprovando o funcionamento através do correto preenchimento da tabela verdade.

Latch RS Controlado

- Objetivo

- Testar o funcionamento de um circuito Latch RS Controlado, feito a partir das portas lógicas AND (E) e NOR (NOU) como mostra a Figura 1.

Figura 1 - Latch RS controlado.

| C | R | S | Q |

|---|---|---|---|

| 0 | X | X | |

| 1 | 0 | 0 | |

| 1 | 0 | 1 | |

| 1 | 1 | 0 | |

| 1 | 1 | 1 |

Procedimento

- O trabalho é individual;

- Desenhar as ligações utilizando o esquemático dos CIs;

- Desenhar o diagrama de pinagem de todos os CI utilizados (pesquisar no datasheet);

- Montar o circuito no software Proteus ou na página do falstad;

- Fazer a ligação entre as portas lógicas do circuito;

- Fazer a ligação de R, S e C com entradas lógicas;

- Fazer a ligação das Saídas Q e Q\ com saídas lógicas;

- Completar a Tabela Verdade.

Material Utilizado

- Listar qual o software que utilizou e se usou celular, tablet ou computador (PC, notebook, laptop).

Relatório

O relatório simplificado deverá ser preenchido e postado em PDF no SIGAA dentro do prazo combinado para atividade.

- Critérios avaliativos

- Prática (montagem/equipe): 4

- Circuito completo (todos): 3

- Resultados e discussões : 3

- Resultado: 10

Referências

[1] Circuito Simulador Applet - falstad

[2] Datasheet 7408

[3] Datasheet 7402