Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

| Linha 3 327: | Linha 3 327: | ||

LOAD : in std_logic; | LOAD : in std_logic; | ||

DATA : in std_logic_vector(WIDTH-1 downto 0); | DATA : in std_logic_vector(WIDTH-1 downto 0); | ||

| − | R0 : out std_logic | + | R0 : out std_logic; |

Q : out std_logic_vector(WIDTH-1 downto 0)); | Q : out std_logic_vector(WIDTH-1 downto 0)); | ||

end entity; | end entity; | ||

Edição das 08h55min de 25 de agosto de 2023

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 6 ENCONTROS

| Unidade 1 - Introdução a disciplina |

|---|

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 10 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

entity mux_novo is

port

(

-- Input ports

X: in bit_vector (3 downto 0);

S : in bit_vector (1 downto 0);

-- Output ports

Y : out bit

);

end entity mux_novo;

-- Implementação com lógica pura

architecture v_logica_pura of mux_novo is

begin

Y <= (X(0) and (not S(1)) and (not S(0))) or

(X(1) and (not S(1)) and (S(0))) or

(X(2) and (S(1)) and (not S(0))) or

(X(3) and (S(1)) and (S(0)));

end architecture Logica_pura;

-- Implementação com WHEN ELSE

architecture v_WHEN of mux_novo is

begin

Y <= X(0) when S = "00" else

X(1) when S = "01" else

X(2) when S = "10" else

X(3);

end architecture v_WHEN;

-- Implementação com WITH SELECT

architecture v_WITH_SELECT of mux_novo is

begin

with S select

Y <= X(0) when "00", -- note o uso da ,

X(1) when "01",

X(2) when "10",

X(3) when others; -- note o uso de others, para todos os demais valores.

-- Não pode ser substituido por "11" mesmo que o signal seja bit_vector.

end architecture v_WITH_SELECT;

-- Implementação com IF ELSE

architecture v_IF_ELSE of mux_novo is

begin

-- Uma arquitetura vazia como essa é denominada de STUB,

-- Pode ser utilizada em um projeto durante para conferir as conexões externas.

-- Posteriormente a arquitetura será descrita.

end architecture v_IF_ELSET;

-- Design Unit que associa a architecture com a entity

configuration cfg_ifsc of mux_novo is

-- for v_WITH_SELECT end for;

for v_WHEN end for;

end configuration;

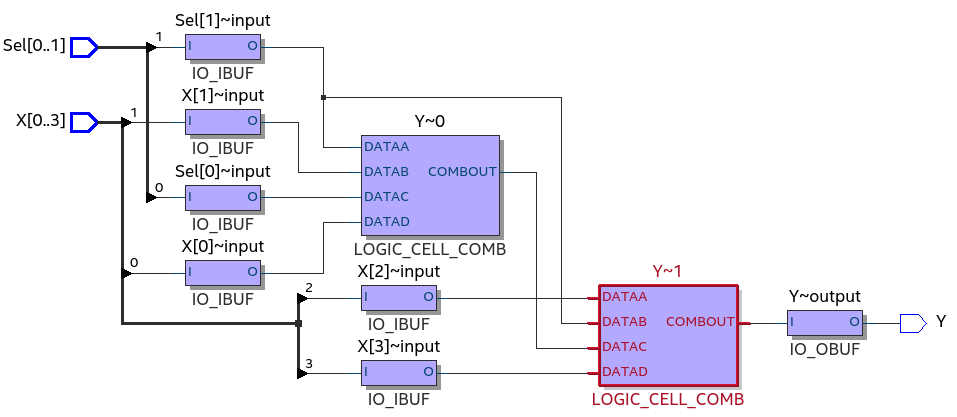

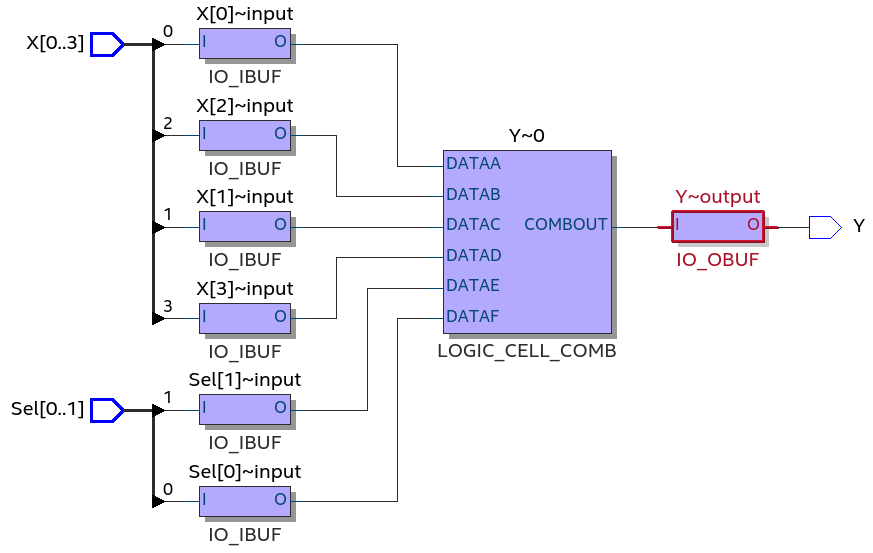

Figura 2.1 - Código RTL do mux 4x1 v_logica_pura  Figura 2.2 - Código RTL do mux 4x1 v_WHEN  Figura 2.3 - Código RTL do mux 4x1 v_WITH_SELECT

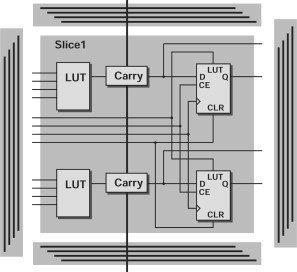

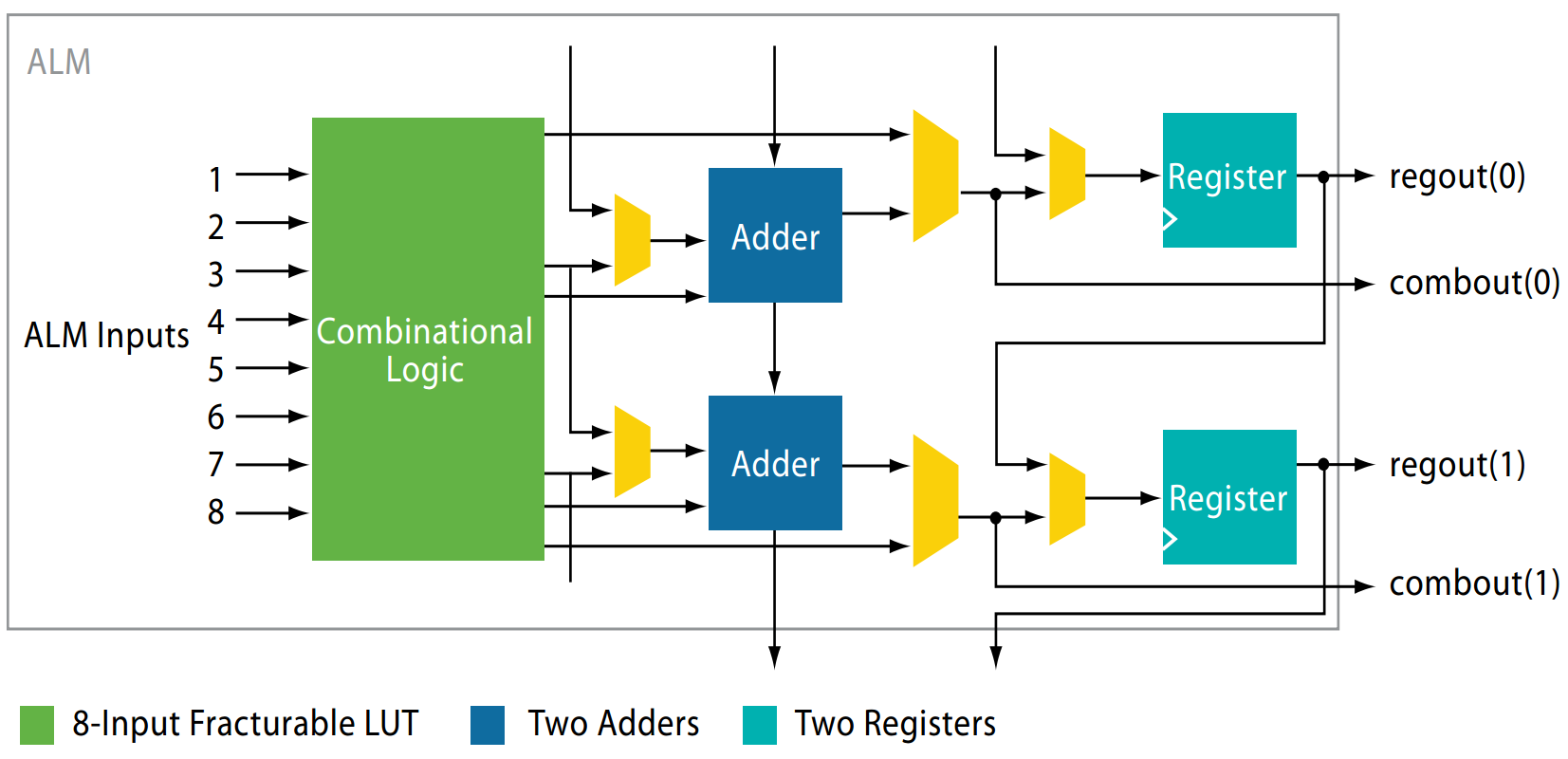

Figura 2.4 - Technology Map do mux 4x1 para a família Cyclone

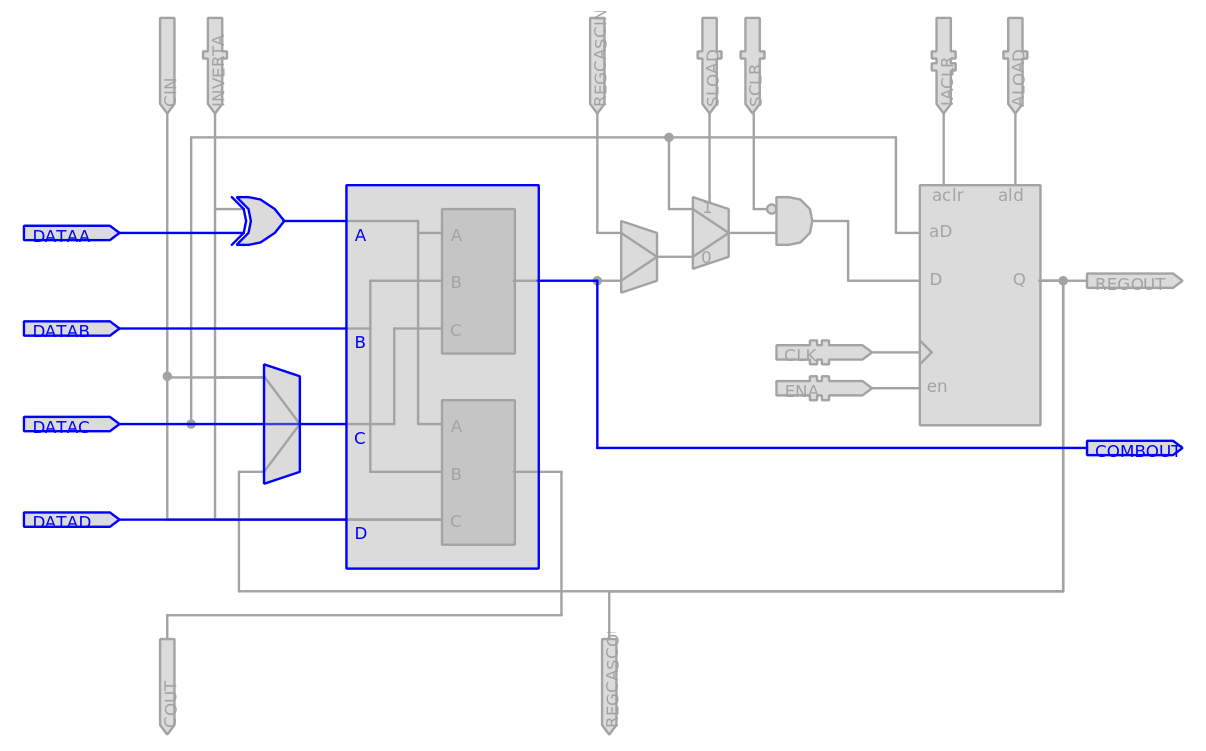

Figura 2.5 - Elemento Lógico usado no mux 4x1 para a família Cyclone (node properties)

No entanto se utilizarmos um dispositivo FPGA da família Stratix III, que tem LUT tem 6 entradas, será necessário apenas 1 LE, conforme ilustrado a seguir. Figura 2.5 - Technology Map do mux 4x1 para a família Stratix III

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

Figura 2.2 - Código RTL do Exemplo 2.2

Figura 2.3 - Technology Map do Exemplo 2.2

Figura 2.4 - Chip Planner do Exemplo 2.2

Figura 2.5 - RTL 4 FF

ls /opt/intelFPGA/20.1/quartus/libraries/vhdl/std

/opt/intelFPGA/20.1/quartus/libraries/vhdl/ieee

/opt/intelFPGA/20.1/quartus/libraries/vhdl/mentor/arithmetic (Mentor Graphics) /opt/intelFPGA/20.1/quartus/libraries/vhdl/synopsys/ieee (Synopsys)

ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add_v1 IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END ENTITY;

ARCHITECTURE ifsc_v1 OF registered_comp_add_v1 IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END ARCHITECTURE;

Figura 2.10 - Código RTL do Exemplo 2.3

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all; -- for the unsigned type

entity COUNTER is

generic (

WIDTH : in natural := 32);

port (

RST : in std_logic;

CLK : in std_logic;

LOAD : in std_logic;

DATA : in std_logic_vector(WIDTH-1 downto 0);

Q : out std_logic_vector(WIDTH-1 downto 0));

end entity COUNTER;

architecture RTL of COUNTER is

begin

process(all) is

begin

if RST then

Q <= (others => '0');

elsif rising_edge(CLK) then

if LOAD='1' then

Q <= DATA;

else

Q <= std_logic_vector(unsigned(Q) + 1);

end if;

end if;

end process;

end architecture RTL;

Figura 2.6 - Simulação funcional com QSIM de 4 FF - 100ns  Figura 2.7 - Simulação Temporal com QSIM de 4 FF - 100ns

IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possível verificar se o circuito atende as restrições de tempo.

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

ATUAL

|

Unidade 3 - Tipos de Dados e Operadores em VHDL

- 10 ENCONTROS

| Unidade 3 - Tipos de Dados e Operadores em VHDL |

|---|

Unidade 4 - Código Concorrente

- 4 ENCONTROS

| Unidade 4 - Código Concorrente |

|---|

Unidade 5 - Código Sequencial

- 7 ENCONTROS

| Unidade 5 - Código Sequencial |

|---|

Unidade 6 - Projeto a nível de Sistema

- 3 ENCONTROS

| Unidade 6 - Projeto a nível de Sistema |

|---|

Unidade 7 - Maquinas de Estado Finitas

- 3 ENCONTROS

| Unidade 7 - Maquinas de Estado Finitas |

|---|

Unidade 8 - Testbench

- 2 ENCONTROS

| Unidade 8 - Testbench |

|---|

Avaliações

Nas avaliações A1 e A2 vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

- Data das avaliações

- A1 - Unidade 1 a Unidade 4: dia XX/XX

- A2 - Unidade 5 a Unidade 7: dia XX/XX

- PF - Entrega do projeto final: dia 15/12

- R12 - Recuperação de A1 e A2 : dia 12/12

Atividade relâmpago (AR)

As atividades relâmpago devem ser entregues no Moodle da disciplina. A não entrega dessas atividades não gera nenhum desconto, apenas geram pontos de BÔNUS que são adicionados aos conceitos das avaliações A1 a AN.

Atividade extra-classe (AE)

A média ponderada das atividades extra-classe será considerada no cálculo do conceito final da UC. A entrega das mesmas será feita pelo Moodle, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

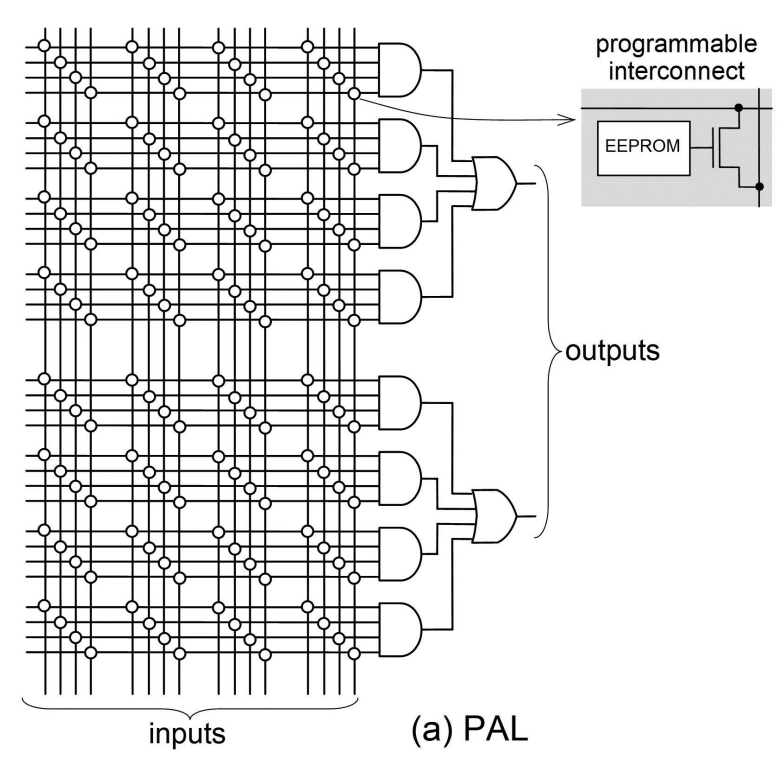

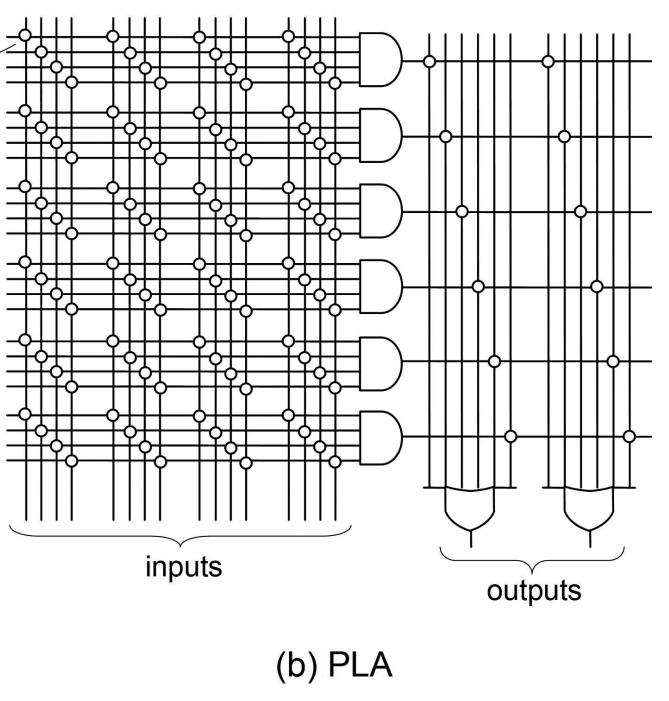

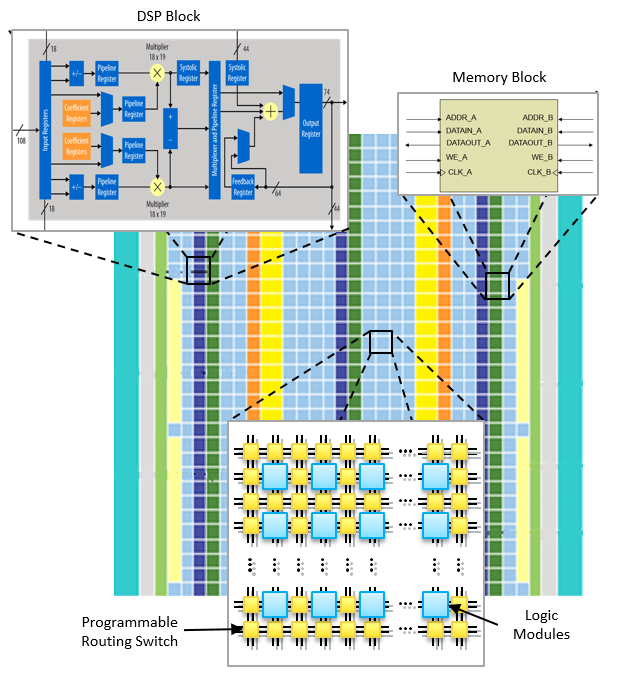

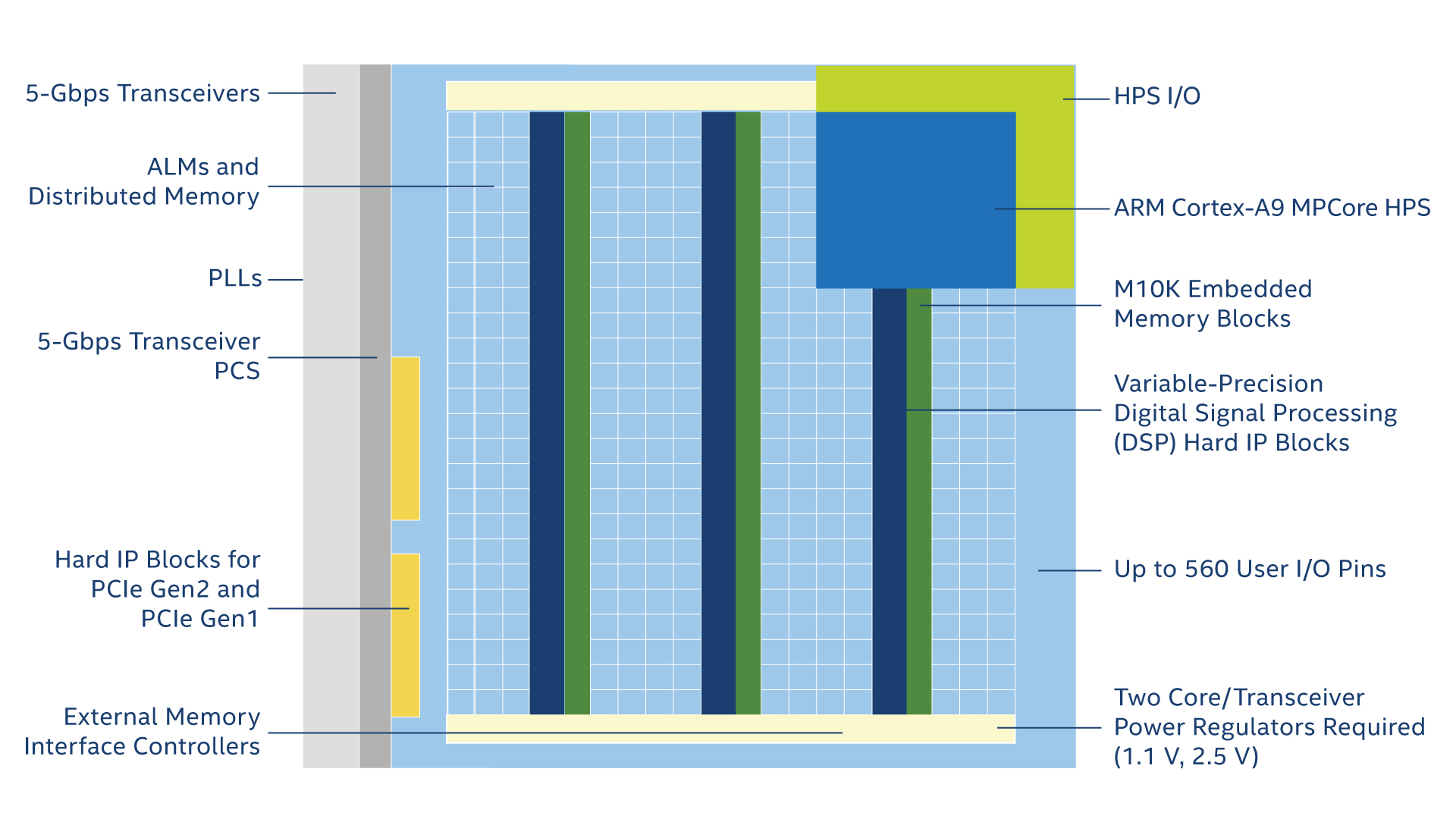

AE2 - Conhecendo os dispositivos lógicos programáveis

| AE2 - Conhecendo os dispositivos lógicos programáveis |

|---|

|

AE3 - Programação do kit Mercurio IV

| AE3 - Programação do kit Mercurio IV |

|---|

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

entity counter is

generic (WIDTH : in natural := 4);

port (

RST : in std_logic;

CLK : in std_logic;

LOAD : in std_logic;

DATA : in std_logic_vector(WIDTH-1 downto 0);

R0 : out std_logic;

Q : out std_logic_vector(WIDTH-1 downto 0));

end entity;

architecture ifsc_v1 of counter is

signal Q_aux : std_logic(WIDTH-1 downto 0);

begin

process(RST,CLK) is

begin

if RST = '1' then

Q_aux <= (others => '0');

elsif rising_edge(CLK) then

if LOAD= '1' then

Q_aux <= DATA;

else

Q_aux <= std_logic_vector(unsigned(Q_aux) + 1);

end if;

end if;

end process;

-- Adaptacao feita devido a matriz de leds acender com ZERO

Q <= not Q_aux;

-- Para acender um led eh necessario colocar ZERO na linha correspondente da matriz.

R0 <= '0';

end architecture;

CLK: PIN_Y17 ou PIN_V21 DATA[3]: PIN_H18 DATA[2]: PIN_H20 DATA[1]: PIN_K21 DATA[0]: PIN_J21 LOAD: PIN_Y22 Q[3]: PIN_J6 Q[2]: PIN_K8 Q[1]: PIN_J8 Q[0]: PIN_L8 RST: PIN_W21 R0: PIN_F10

-- insira na declaração das portas da entity a linha

LCD_BACKLIGHT: out std_logic;

-- insira na architecture a linha

LCD_BACKLIGHT <= '0';

LCD_BACKLIGHT: PIN_V10

entity COUNTER_db is

...

CLK50MHz : in std_logic;

...

end entity

architecture ifsc_v2 of COUNTER_db is

...

signal CLK_db: std_logic := '0';

...

begin

-- debouncer de 10ms

process (CLK50MHz, CLK, RST, CLK_db) is

constant max_cnt: natural := 500000; -- 500000 10ms para clk 20ns

variable cnt_db : integer range 0 to max_cnt-1;

begin

if (RST = '1') then

cnt_db := 0;

CLK_db <= '0';

elsif ((CLK = '0') and (CLK_db = '0')) or

((CLK = '1') and (CLK_db = '1')) then

cnt_db := 0;

elsif (rising_edge(CLK50MHz)) then

if (cnt_db = max_cnt - 1) then

CLK_db <= not CLK_db;

else

cnt_db := cnt_db + 1;

end if;

end if;

end process;

...

-- Troque no process(RST,CLK) a entrada '''CLK''' do circuito anterior pela entrada '''CLK_db'''

CLK50MHz: PIN_T1

create_clock -name CLK50MHz -period 50MHz [get_ports -no_case {clk*}]

|