Mudanças entre as edições de "DLP29006-Engtelecom(2020-2) - Prof. Marcos Moecke"

(→ATUAL) |

|||

| (39 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 4: | Linha 4: | ||

* 3 AULAS | * 3 AULAS | ||

| − | {{collapse top | + | {{collapse top | Unidade 1 - Introdução a disciplina}} |

;Aula 1 (9 Nov): | ;Aula 1 (9 Nov): | ||

| Linha 98: | Linha 98: | ||

===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== | ===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== | ||

* 3 AULAS | * 3 AULAS | ||

| − | {{collapse top| | + | {{collapse top| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS}} |

;Aula 4 (16 nov): | ;Aula 4 (16 nov): | ||

| Linha 330: | Linha 330: | ||

===Unidade 3 - Tipos de Dados e Operadores em VHDL=== | ===Unidade 3 - Tipos de Dados e Operadores em VHDL=== | ||

| − | * | + | * 11 AULAS |

| − | {{collapse top | | + | {{collapse top | Unidade 3 - Tipos de Dados e Operadores em VHDL}} |

;Aula 7 (24 nov): | ;Aula 7 (24 nov): | ||

| Linha 1 448: | Linha 1 448: | ||

* 4 AULAS | * 4 AULAS | ||

| − | {{collapse top | + | {{collapse top| Unidade 4 - Código Concorrente}} |

;Aula 18 (4 fev): | ;Aula 18 (4 fev): | ||

| Linha 1 879: | Linha 1 879: | ||

* Avaliação A1. A avaliação iniciará as 9h20 na [http://meet.google.com/hto-grwk-pzt sala remota]. | * Avaliação A1. A avaliação iniciará as 9h20 na [http://meet.google.com/hto-grwk-pzt sala remota]. | ||

| − | + | ||

;Aula 31 (15 mar): | ;Aula 31 (15 mar): | ||

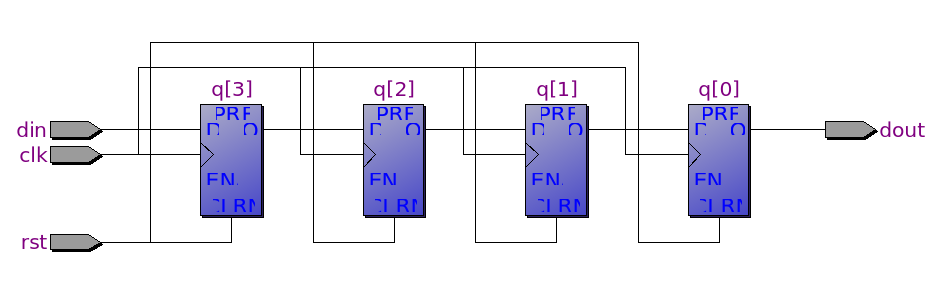

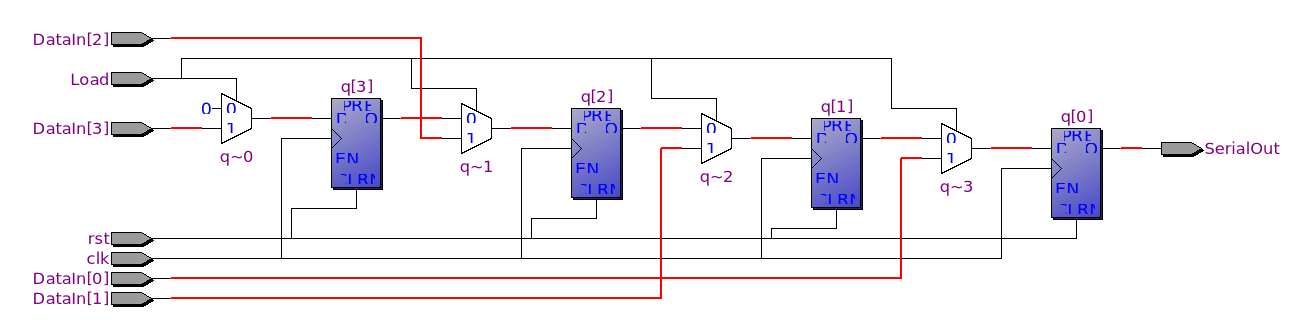

* Registrador de deslocamento (Ex.6.3) | * Registrador de deslocamento (Ex.6.3) | ||

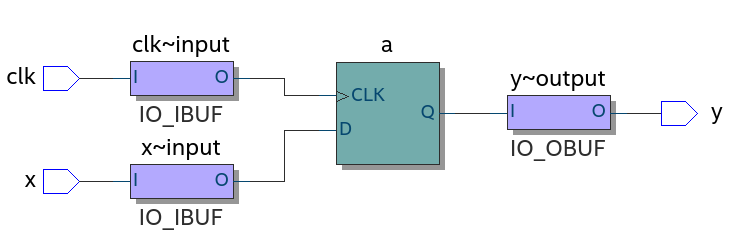

| − | + | {{fig|4.1| RTL do registrador de deslocamento (Ex.6.3) | ShifRegRight.png | 800 px |}} | |

:Versão 1 - Implementação com 4 FF D. | :Versão 1 - Implementação com 4 FF D. | ||

| Linha 1 941: | Linha 1 941: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | Aproveitando a versão 3 ou 2 do Shift Register, projete e faça a simulação dos dois circuitos indicados a seguir: | + | *Simule o Registrador de Deslocamento usando o QSIM, visualizando os sinais internos para perceber o deslocamento. |

| − | + | *Repita a simulação usando o Modelsim. | |

| − | + | ||

| + | ;Aula 32 (18 mar): | ||

| + | |||

| + | Aproveitando a versão 3 ou 2 do Shift Register da aula anterior, projete e faça a simulação dos dois circuitos indicados a seguir: | ||

| + | |||

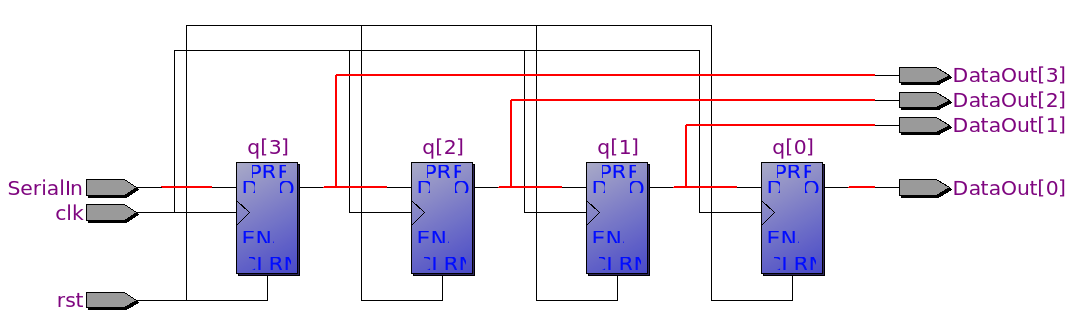

* Embrião de um conversor serial para paralelo. | * Embrião de um conversor serial para paralelo. | ||

| − | |||

| − | |||

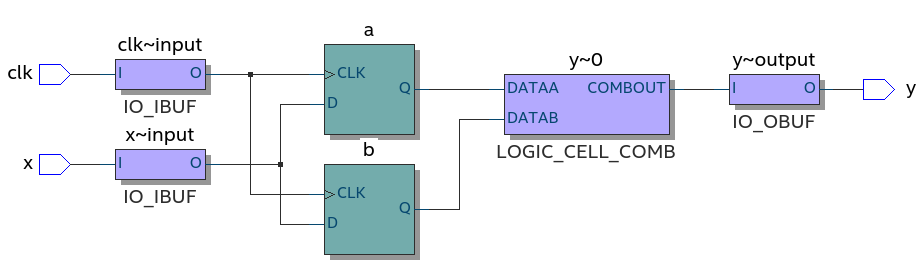

| − | + | {{fig|4.2| RTL do embrião de um conversor serial para paralelo | Serial2Parallel.png | 800 px |}} | |

| + | |||

| + | :Para usar o hardware do ShifRegister como base para um conversor serial para paralelo, basta conectar as saídas dos FFD em portas '''DataOut'''(N-1) até '''DataOut'''(0). Assim, os sinais seriais da entrada '''SerialIn''' estarão disponíveis nestas saídas '''DataOut''' a cada N clocks. | ||

| + | |||

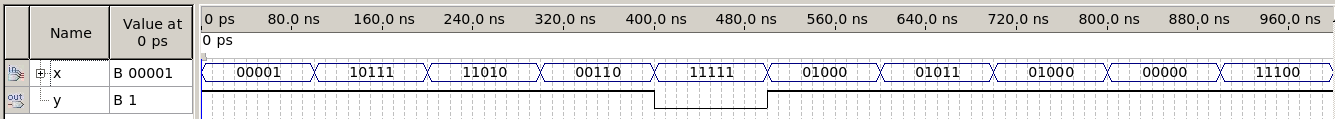

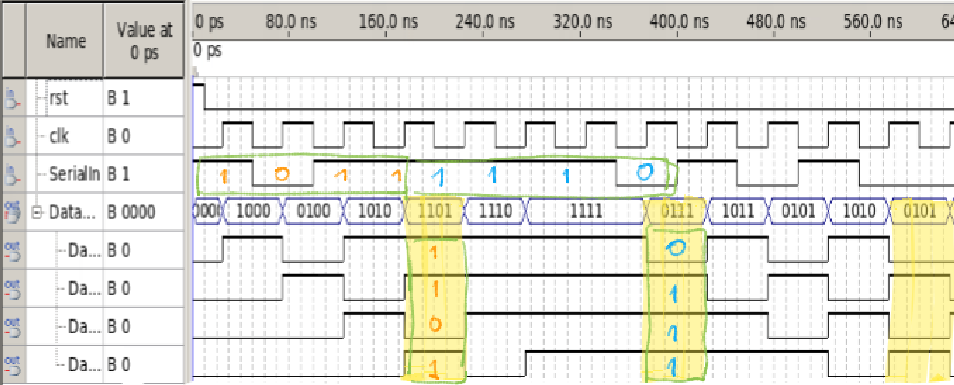

| + | {{fig|4.3| Simulação funcional do embrião de um conversor serial para paralelo | Serial2Parallel_SIM.png | 800 px |}} | ||

| + | |||

:Uma simulação com o QSIM é mostrada na figura acima. | :Uma simulação com o QSIM é mostrada na figura acima. | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 1 967: | Linha 1 974: | ||

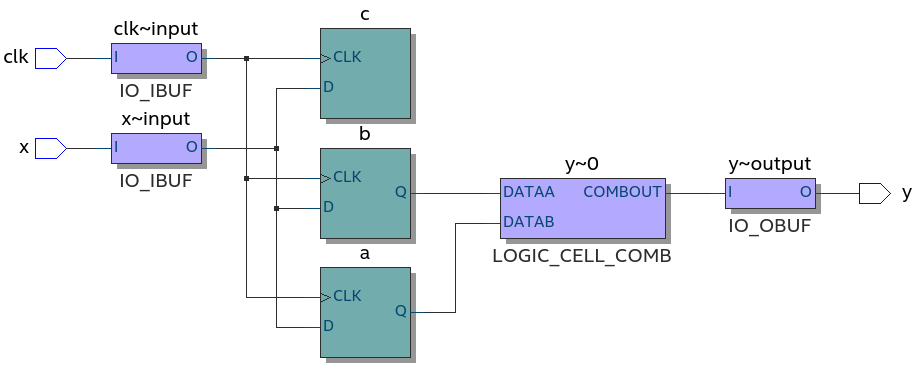

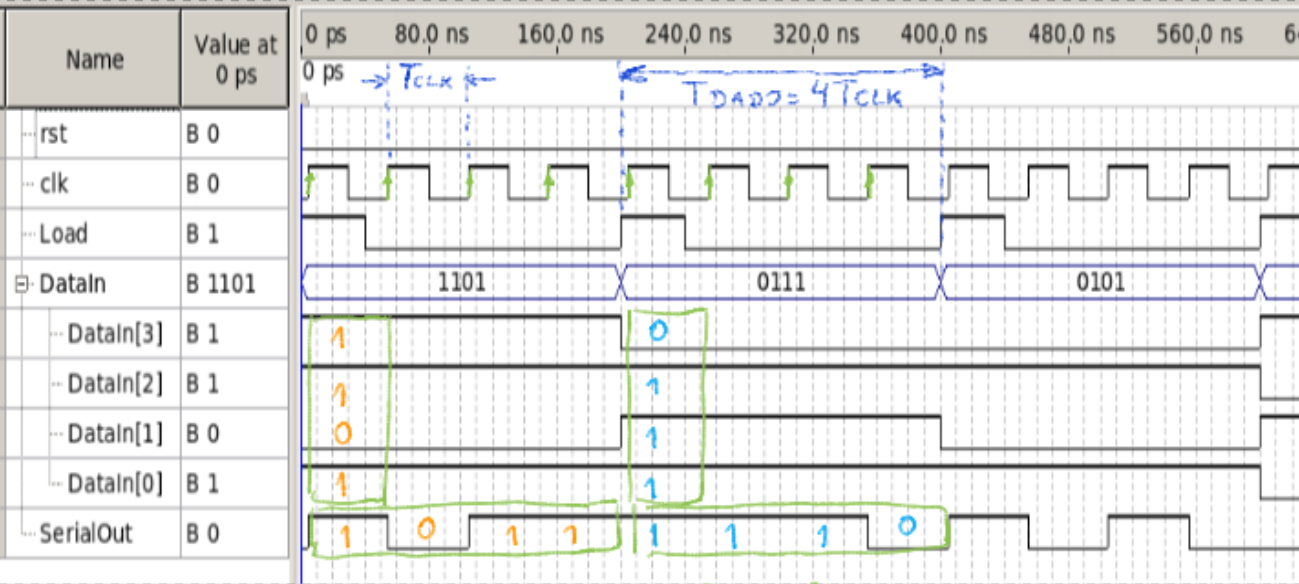

* Embrião de um conversor paralelo para serial. | * Embrião de um conversor paralelo para serial. | ||

| − | + | ||

| + | {{fig|4.4| Simulação funcional do embrião de um conversor paralelo para serial | Paralelo2Serial.png | 800 px |}} | ||

| + | |||

:Para usar o hardware do ShiftRegister como base para um conversor paralelo para serial, é necessário carregar os dados paralelos do '''DataIn''' com o sinal '''Load''' nos FFD e em seguida fazer o deslocamento deles bit por bit durante N clocks. Na saída '''SerialOut''' do ShiftRegister os dados serão seriazados, aparecendo um cada clock. | :Para usar o hardware do ShiftRegister como base para um conversor paralelo para serial, é necessário carregar os dados paralelos do '''DataIn''' com o sinal '''Load''' nos FFD e em seguida fazer o deslocamento deles bit por bit durante N clocks. Na saída '''SerialOut''' do ShiftRegister os dados serão seriazados, aparecendo um cada clock. | ||

| − | + | {{fig|4.5| Simulação funcional do embrião de um conversor paralelo para serial | Paralelo2Serial_SIM.png | 800 px |}} | |

| + | |||

:Uma simulação com o QSIM é mostrada na figura acima. | :Uma simulação com o QSIM é mostrada na figura acima. | ||

| Linha 1 989: | Linha 1 999: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | :*Instruções do tipo '''LOOP''': LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT | + | ;Aula 33 (22 mar): |

| − | + | *Aprendizado prático de simulação com Modelsim | |

| + | |||

| + | ;Aula 34 (23 mar): | ||

| + | |||

| + | Instruções do tipo '''LOOP''': LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT | ||

| + | |||

| + | *Instrução '''LOOP''' incondicional: | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

[rótulo:] LOOP | [rótulo:] LOOP | ||

| Linha 1 999: | Linha 2 015: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | *Instrução '''FOR-LOOP''': | |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

[rótulo:] FOR identificador IN faixa LOOP | [rótulo:] FOR identificador IN faixa LOOP | ||

| Linha 2 008: | Linha 2 024: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | *Instrução '''WHILE-LOOP''': | |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

[rótulo:] WHILE condição LOOP -- Executa as "afirmações enquanto a "condição" for verdadeira | [rótulo:] WHILE condição LOOP -- Executa as "afirmações enquanto a "condição" for verdadeira | ||

| Linha 2 017: | Linha 2 033: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | *Instrução LOOP com '''EXIT''': | |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

[rótulo:] [FOR identificador IN faixa] LOOP | [rótulo:] [FOR identificador IN faixa] LOOP | ||

| Linha 2 027: | Linha 2 043: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | *Instrução LOOP com '''NEXT''': | |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

[rótulo:] [FOR identificador IN faixa] LOOP | [rótulo:] [FOR identificador IN faixa] LOOP | ||

| Linha 2 036: | Linha 2 052: | ||

... | ... | ||

END LOOP [rótulo]; | END LOOP [rótulo]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | *Instrução '''CASE''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] CASE expressão IS | ||

| + | WHEN valor => atribuições; -- valor único | ||

| + | ... | ||

| + | WHEN valor1 | valor2 | ... | valorN => atribuições; -- lista de valores | ||

| + | ... | ||

| + | WHEN valor1 TO valor2 => atribuições; -- faixa de valores | ||

| + | ... | ||

| + | |||

| + | END CASE; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| Linha 2 051: | Linha 2 080: | ||

end entity; | end entity; | ||

| − | architecture | + | architecture ____ of leading_zeros is |

| + | |||

begin | begin | ||

| − | + | process (data) | |

| − | end | + | variable count : integer ____ 0 to N |

| + | begin | ||

| + | count := 0; | ||

| + | for i ___ data'range ____ | ||

| + | case data(i) is | ||

| + | when '0' => count := count + 1; | ||

| + | when _____ => exit; | ||

| + | end ___ | ||

| + | end ____ | ||

| + | zeros <= count; | ||

| + | end process; | ||

| + | end _______; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| Linha 2 062: | Linha 2 103: | ||

*Ver pag. 161 a 164 de <ref name="PEDRONI2010b"/> | *Ver pag. 161 a 164 de <ref name="PEDRONI2010b"/> | ||

| − | |||

* Carry-Ripple Adder (FOR-LOOP) (Ex 6.4) - apenas analisar. | * Carry-Ripple Adder (FOR-LOOP) (Ex 6.4) - apenas analisar. | ||

:* Um somador do tipo carry ripple utiliza o bloco básico '''full adder''' para construir somadores de qualquer número de bits. Os bits carry são adicionados aos blocos posteriores, produzindo um hardware combinário. | :* Um somador do tipo carry ripple utiliza o bloco básico '''full adder''' para construir somadores de qualquer número de bits. Os bits carry são adicionados aos blocos posteriores, produzindo um hardware combinário. | ||

| Linha 2 097: | Linha 2 137: | ||

end process; | end process; | ||

end architecture; | end architecture; | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

</syntaxhighlight> | </syntaxhighlight> | ||

| Linha 2 123: | Linha 2 150: | ||

:Algumas instruções de '''WAIT''' serão utilizadas na criação de '''TestBench''' em VHDL para a simulação com o '''MODELSIM'''. | :Algumas instruções de '''WAIT''' serão utilizadas na criação de '''TestBench''' em VHDL para a simulação com o '''MODELSIM'''. | ||

| + | ;Aula 35 (25 mar): | ||

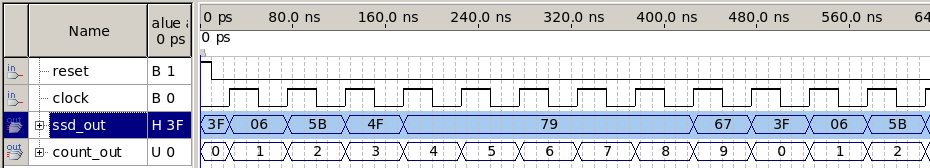

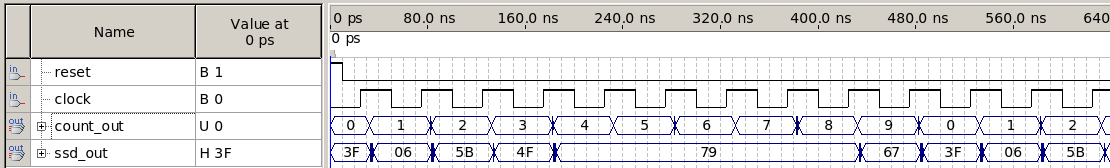

* Exemplo: Timer de 0 a 9 segundos com saída SSD (Ex 6.6). | * Exemplo: Timer de 0 a 9 segundos com saída SSD (Ex 6.6). | ||

:* Unir o código de um contador de 0 a 9 (código sequencial), e um conversor de binário para sete segmentos em código sequencial (usando CASE). | :* Unir o código de um contador de 0 a 9 (código sequencial), e um conversor de binário para sete segmentos em código sequencial (usando CASE). | ||

| Linha 2 150: | Linha 2 178: | ||

A simulação funcional do circuito deverá produzir uma saída semelhante a mostrada abaixo: | A simulação funcional do circuito deverá produzir uma saída semelhante a mostrada abaixo: | ||

| − | + | {{fig|4.6| simulação funcional do timer0_9 | Timer0_9_SIM_FUNC.png | 600 px | }} | |

A simulação com timing do circuito deverá produzir uma saída semelhante a mostrada abaixo: | A simulação com timing do circuito deverá produzir uma saída semelhante a mostrada abaixo: | ||

| − | + | {{fig|4.7| simulação com timing do timer0_9 | Timer0_9_SIM_TIME.png | 600 px | }} | |

| − | + | Depois acrescentar a esse circuito um módulo que permita a partir de um sinal de clock com frequência de fclk = 50MHz (T = 20 ns), obter um clock de f = 1 Hz (T = 1 s) | |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | process (rst, clk50MHz) | |

| − | + | -- processo do divisor de clock de 50MHz para 1 Hz | |

| − | + | end process; | |

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | Implementar no FPGA o circuito com contador de 0 a 9 segundos com saída SSD e clk de entrada de 50MHz. | |

| − | + | * PROBLEMA: Uso de um período de clock de 20 ns => 50 MHz, verificar a impossibilidade prática de uma simulação deste circuito (1 segundo => 5 minutos de simulação), devido ao tamanho do contador (count1) que conta de 0 a 50M-1. | |

| − | + | * SOLUÇÃO: modificar o contador para um valor máximo menor (0 a 50-1). Notar que a simulação é extremamente rápida neste caso. | |

| − | + | * Após verificar que o circuito funciona "simulado", configurar o FPGA do '''kit Mercúrio IV''' para implementar este circuito. | |

| − | + | * As informações necessárias para configurar o dispositivo e seus pinos estão em [[Preparando para gravar o circuito lógico no FPGA]]. | |

| + | * Utilize os pinos (clk = CLOCK_50MHz: PIN_T1, led = DISP0_D[7] : PIN_W1, ssd = DISP0_D[0-6]: PIN_V2 - PIN_W2). | ||

| + | * Como o conversor de binário para ssd realizado anteriormente tinha lógica negativa ('0' acende, '1' apaga), será necessário inverter todas as saídas | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | ssd_out <= not ssd; | |

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | * Se quiser usar algum led na matriz de led do kit Mercúrio é necessário colocar '0' da coluna do Led e '1' na linha correspondente, ou seja utilizar um segundo pino para acender o led. | |

| + | |||

| + | Uso do Modelsim para simulação funcional. | ||

| − | + | * Use o Modelsim para fazer a simulação do circuito do timer de 0 a 9 segundos. | |

| − | * | + | * Ver [[Seguindo o tutorial da ALTERA para o MODELSIM]], para utilizar o básico do MODELSIM. |

| + | * [http://www.vhdl.us Pedroni VHDL 2ed Tutorial of ModelSim 10.1d] | ||

| + | * [[Media:modelsim_tut.pdf |ModelSim® Tutorial]] -v10.0d | ||

| + | * [[Documentação do ModelSim]], para conhecer mais a fundo o MODELSIM. | ||

| + | ;Aula 36 (29 mar): | ||

| + | ====AE5 ==== | ||

| + | {{collapse top| bg=lightyellow | AE5 - Laboratório de programação de FPGA - Timer 00 a 99 segundos sem o uso de componente - versão 1}} | ||

| − | + | *[https://moodle.ifsc.edu.br/mod/assign/view.php?id=357699 AE5 - Laboratório de programação de FPGA - Timer 00 a 99 segundos em componente versão 1] | |

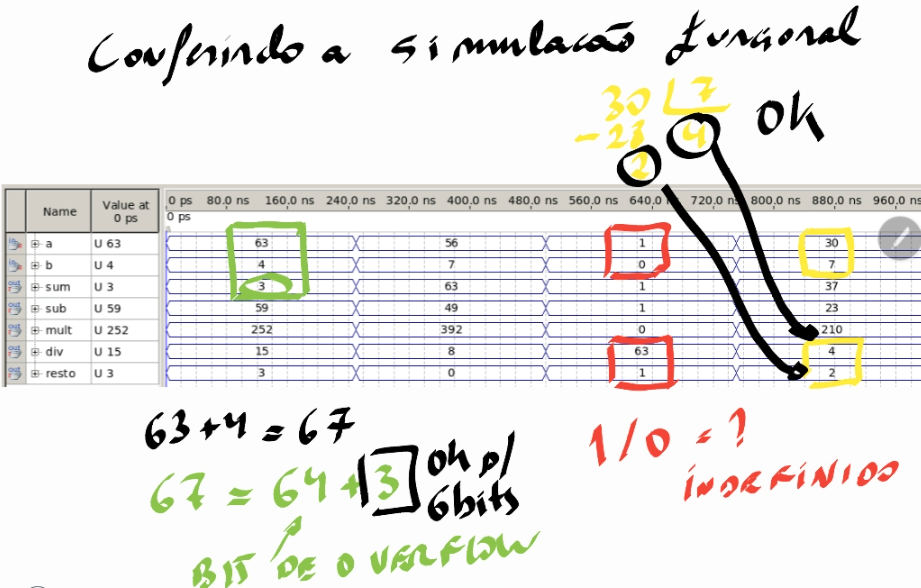

| − | + | Projete um contador BCD de 00 a 99 configurável com saída em 2 mostradores de 7 segmentos. | |

| − | + | *Utilize o timer 0 a 9 desenvolvido em aula como base, substituindo o contador 0 a 9 pelo contador BCD 00 a 99. | |

| − | + | *O contador deve ser configurável para contar qualquer valor entre 01 até 99. | |

| − | + | *Efetue a simulação funcional (Usando Modelsim) fazendo a contagem de 00 a 11 e também de 00 a 23 (para hora), de 00 a 59 (para minutos e segundos), e de 00 a 99. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

entity Timer00_99seg is | entity Timer00_99seg is | ||

| Linha 2 215: | Linha 2 234: | ||

end entity; | end entity; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | ||

| − | *Projeto e simulação com Modelsim do sistema Timer00-99 com display de 7 segmentos e divisor de clock. | + | * Configure o FPGA do kit Mercúrio IV para implementar este circuito. Utilize os mostradores ssd DISP0_D e DISP1_D. |

| − | *Na simulação definir o clk50MHz como 100ms para produzir um clk1sec com duração de 1 segundo. | + | * Após verificar que o circuito funciona "simulado", configurar o FPGA do '''kit Mercúrio IV''' para implementar este circuito. |

| − | *Corrigir o primeiro período de clock de clk1sec. É necessário fazer com que o sinal seja alto primeiro e depois vá para baixo de modo a garantir que a transição positiva ocorra depois de 1 segundo. | + | * As informações necessárias para configurar o dispositivo e seus pinos estão em [[Preparando para gravar o circuito lógico no FPGA]]. |

| + | * Projeto e simulação com Modelsim do sistema Timer00-99 com display de 7 segmentos e divisor de clock. | ||

| + | * Na simulação definir o clk50MHz como 100ms para produzir um clk1sec com duração de 1 segundo. | ||

| + | * Corrigir o primeiro período de clock de clk1sec. É necessário fazer com que o sinal seja alto primeiro e depois vá para baixo de modo a garantir que a transição positiva ocorra depois de 1 segundo. | ||

*'''IMPORTANTE''': Também é necessário incluir um RESET em cada circuito que seja sequencial. Também é necessário iniciar o circuito com um reset de 10 ps na simulação. | *'''IMPORTANTE''': Também é necessário incluir um RESET em cada circuito que seja sequencial. Também é necessário iniciar o circuito com um reset de 10 ps na simulação. | ||

| − | *Perceber a necessidade de parametrizar o conversor de bcd2ssd para permitir displays do tipo CA e AA. (ler [[Display de 7 segmentos]]) | + | * Perceber a necessidade de parametrizar o conversor de bcd2ssd para permitir displays do tipo CA e AA. (ler [[Display de 7 segmentos]]) |

| − | *Perceber a necessidade de incluir um sinal que indique o final da contagem no counter00_99. Esse sinal poderá ser usado como clock no relógio a ser projetado. | + | * Perceber a necessidade de incluir um sinal que indique o final da contagem no counter00_99. Esse sinal poderá ser usado como clock no relógio a ser projetado. |

| − | |||

| − | |||

| − | ==Avaliações== | + | ;Bonus: |

| − | Nas avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues: | + | *(1 pontos na avaliação A2) para o primeiro estudante que entregar o QAR com o código e as simulações feitas |

| − | <!-- | + | *(0.5 pontos na avaliação A2) para o primeiro estudante que entregar o arquivo SOF fazendo a contagem corretamente no kit da Macnica Mercúrio IV. |

| − | *[[Media:VHDL_QRC-Qualis.pdf | VHDL QUICK REFERENCE CARD]] - Qualis | + | *(1 ponto na avaliação A2) para o primeiro estudante que entregar o arquivo SOF que além de fazer a contagem, mostre a matriz de leds indicando o valor BCD da dezena na primeira linha e o valor BCD da unidade na segunda linha. Dicas de como fazer ver [[Como utilizar a matriz de leds do kit Mercurio IV da Macnica]] |

| − | *[[Media:VHDL1164_QRC-Qualis.pdf | VHDL 1164 PACKAGES QUICK REFERENCE CARD]] Qualis | + | <center> {{#ev:youtube|orjy0GURH_U}} </center> |

| − | --> | + | |

| − | *[[Media:VHDL_QRC-SynthWorks.pdf | VHDL Quick Reference]] - SynthWorks | + | {{collapse bottom}} |

| − | *[[Media:VHDL_Type_Operators_QR-SynthWorks.pdf | VHDL Types and Operators Quick Reference]] - SynthWorks | + | |

| − | *[[Media:ModelSim_QR-SynthWorks.pdf |ModelSim Quick Reference]] - SynthWorks | + | {{collapse bottom}} |

| − | *[[Media:Tabelas_Pedroni.pdf | Tabelas das figuras 3.6, 3.10 e 4.1]] do livro do Pedroni. | + | ===Unidade 6 - Projeto a nível de Sistema=== |

| − | *[[Arquivo:Numeric_std_conversions.png | Diagrama de conversões de tipos numéricos no pacote Numeric_std ]] | + | * 4 AULAS |

| − | ::Dica use também como fonte de consulta os '''templates''' do Quartus. | + | {{collapse top| expand=true | Unidade 6 - Projeto a nível de Sistema}} |

| + | |||

| + | ; Aula 37 (1 abr): | ||

| + | *Projeto a nível de Sistema. | ||

| + | :* O '''PACKAGE''' e '''PACKAGE BODY''': onde declarar e como usar. | ||

| + | :* O '''COMPONENT''': declaração (cópia da '''ENTITY''') e instanciação. | ||

| + | Assim a entity Timer00_99 | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | ENTITY timer00_99seg | ||

| + | GENERIC (D : INTEGER; | ||

| + | fclock : INTEGER; | ||

| + | U : INTEGER); | ||

| + | PORT (clk50MHz : IN STD_LOGIC; | ||

| + | RST : IN STD_LOGIC; | ||

| + | clk1seg : OUT STD_LOGIC; | ||

| + | SSD_Dseg : OUT STD_LOGIC_VECTOR(0 TO 6); | ||

| + | SSD_Useg : OUT STD_LOGIC_VECTOR(0 TO 6)); | ||

| + | END ENTITY; | ||

| + | </syntaxhighlight> | ||

| + | Será declarada como um COMPONENT | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | COMPONENT timer00_99seg | ||

| + | GENERIC (D : INTEGER; | ||

| + | fclock : INTEGER; | ||

| + | U : INTEGER); | ||

| + | PORT (clk50MHz : IN STD_LOGIC; | ||

| + | RST : IN STD_LOGIC; | ||

| + | clk1seg : OUT STD_LOGIC; | ||

| + | SSD_Dseg : OUT STD_LOGIC_VECTOR(0 TO 6); | ||

| + | SSD_Useg : OUT STD_LOGIC_VECTOR(0 TO 6)); | ||

| + | END COMPONENT; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | * Associação dos nomes das portas aos sinais. PORT -> '''PORT MAP''': | ||

| + | * Mapeamento por posição e nominal. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | comp1 : timer00_99seg | ||

| + | GENERIC MAP (2, 10, 3) | ||

| + | PORT MAP (clk50MHz,RST, clk1seg, SSD_Dseg, SSD_Useg); | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | comp1 : timer00_99seg | ||

| + | GENERIC MAP ( D => 2, U => 3, | ||

| + | fclock => 10, | ||

| + | PORT MAP ( clk50MHz => clk50MHz, | ||

| + | RST => RST, | ||

| + | clk1seg => clk1seg, | ||

| + | SSD_Dseg => SSD_Dseg, | ||

| + | SSD_Useg => SSD_Useg); | ||

| + | </syntaxhighlight> | ||

| + | * Métodos de declaração de '''COMPONENT'''. | ||

| + | :* Exemplo: Porta NAND de 3 entradas. | ||

| + | |||

| + | * Criação de '''COMPONENT''' redimensionáveis. GENERIC -> '''GENERIC MAP''' | ||

| + | :* Exemplo: Registrador de deslocamento. | ||

| + | |||

| + | *Ver outros exemplos | ||

| + | :*Exemplo: Registrador Circular Ex. 8.2 | ||

| + | :*Exemplo: Porta E com N entradas. | ||

| + | :*Exemplo: Detector de Paridade Ex. 8.3 | ||

| + | :* Ver pag. 201 a 213 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | ; Aula 38 (5 abr): | ||

| + | :* Instanciação de '''COMPONENT''' com '''GENERATE'''. | ||

| + | |||

| + | :* Uso da instrução '''CONFIGURATION'''. | ||

| + | ::* Ligação direta: ARCHITECTURE-ENTITY. | ||

| + | ::* Ligação da instanciação dos componentes: COMPONENT-ENTITY(ARCHITECTURE). | ||

| + | |||

| + | |||

| + | ====AE6 ==== | ||

| + | {{collapse top| bg=lightyellow | AE6 - Laboratório de programação de FPGA - Timer 00 a 99 segundos com componente - versão 2}} | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity timer00_99seg IS | ||

| + | generic (fclk2 : natural := 50, D : natural := 5; U : natural := 9); | ||

| + | port | ||

| + | ( | ||

| + | clk50MHz : in STD_LOGIC; | ||

| + | clk_1seg: out STD_LOGIC; | ||

| + | ssd_D : out STD_LOGIC_VECTOR(0 TO 6); | ||

| + | ssd_U : out STD_LOGIC_VECTOR(0 TO 6) | ||

| + | ); | ||

| + | end entity; | ||

| + | </syntaxhighlight> | ||

| + | ;OBS: | ||

| + | *O valor do fclk2 corresponde a metade do período do clock de entrada em Hz. | ||

| + | *Os valores D e U correspondem ao último valor do timer, depois desse valor o timer dever reiniciar a contagem. | ||

| + | |||

| + | : Componente 1 - Divisor de Clock, com o valor da divisão configurável pelo parâmetro '''fclk2''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | component div_clk is | ||

| + | generic (fclk2 : natural := 50); -- frequecia para simulacao | ||

| + | port ( | ||

| + | clk : in std_logic; | ||

| + | clk_out : out std_logic | ||

| + | ); | ||

| + | end component; | ||

| + | ;OBS: | ||

| + | *O valor do fclk2 corresponde a metade do período do clock de entrada em Hz. | ||

| + | |||

| + | </syntaxhighlight> | ||

| + | : Componente 2 - Contador de 00 a 99 com saída em BCD, com o valor final configurável pelos parâmetros '''D e U''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | component count00_99 is | ||

| + | generic (D : natural := 9; U : natural := 9); | ||

| + | port ( | ||

| + | clk : in std_logic; | ||

| + | clk_out : out std_logic; | ||

| + | bcd_U : out std_logic_vector(3 downto 0); | ||

| + | bcd_D : out std_logic_vector(3 downto 0) | ||

| + | ); | ||

| + | end component; | ||

| + | </syntaxhighlight> | ||

| + | ;OBS: | ||

| + | *Os valores D e U correspondem ao último valor do timer, depois desse valor o timer dever reiniciar a contagem. | ||

| + | |||

| + | : Componente 3 - Conversor de BIN para SSD, com um parâmetro configurável '''ac_ccn''' para selecionar Anodo ou Catodo Comum. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | component bin2ssd is | ||

| + | generic (ac_ccn : natural := 0); | ||

| + | port ( | ||

| + | bin_in : in std_logic_vector(3 downto 0); | ||

| + | ssd_out : out std_logic_vector(0 to 6) | ||

| + | ); | ||

| + | end component; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ;OBS: | ||

| + | *O valor ac_ccn é utilizado para configurar o circuito entre ativo alto para display de catodo comum (ac_ccn=0), ou ativo baixo para display de anodo comum (ac_ccn=1). | ||

| + | |||

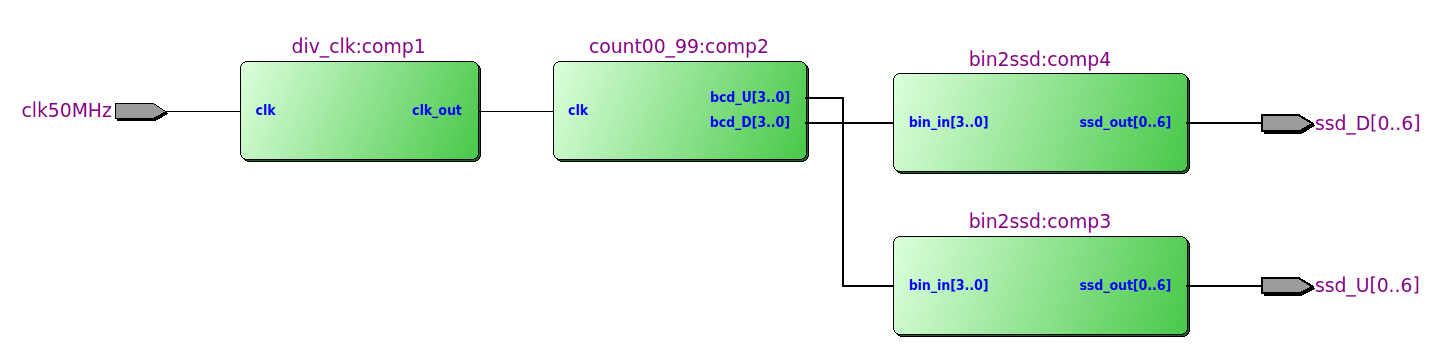

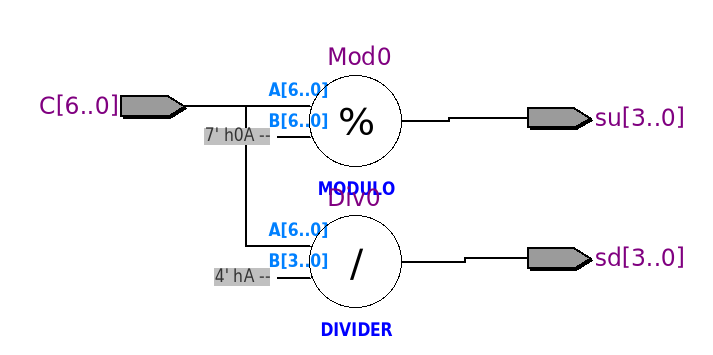

| + | O timer deve utilizar os componentes acima de modo a resultar em um RTL semelhante ao mostrado abaixo. | ||

| + | |||

| + | {{fig|5.1| RTL do timer 00 a 99 segundos | rtl_timer99sec.png | 600 px | }} | ||

| + | |||

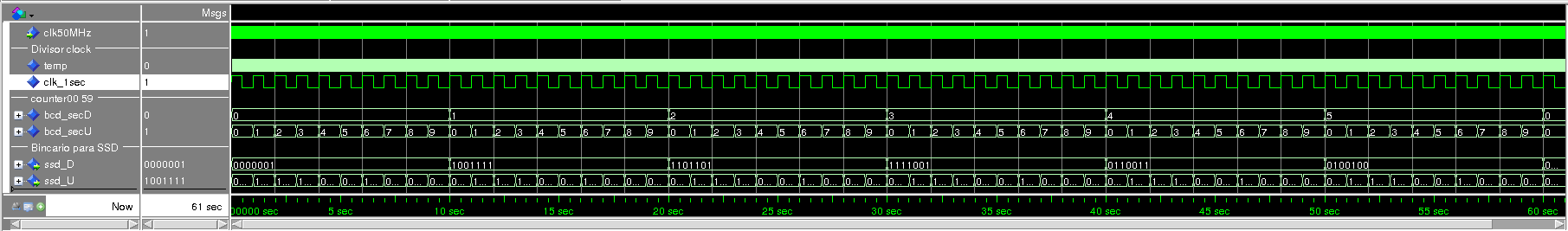

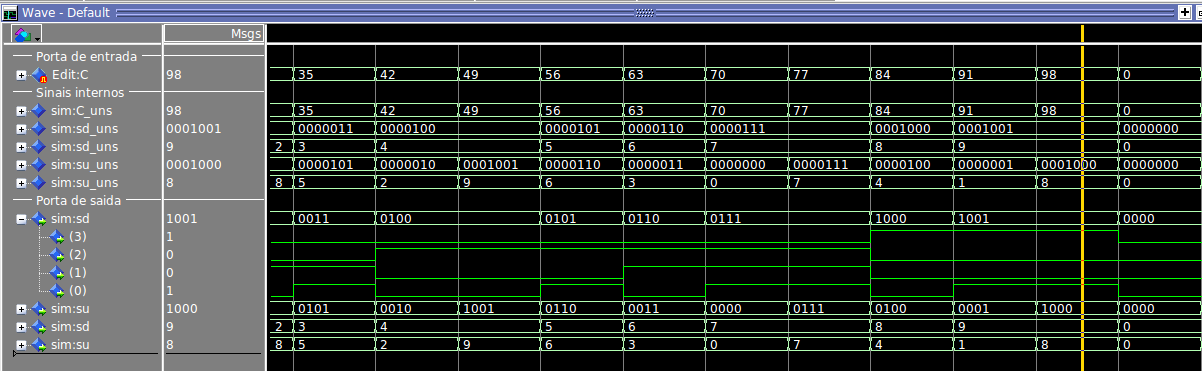

| + | * Simulação do timer com ModelSim. Na simulação definir o clk50MHz com duração de 10 ms. Faça uma simulação de pelo menos 60 segundos. | ||

| + | |||

| + | {{fig|5.2| Simulação do timer 00 a 99 segundos | sim_timer99sec.png | 800 px | }} | ||

| + | |||

| + | OBS: É recomendável inserir um sinal de RESET em todos os circuitos sequenciais e ao iniciar a simulação do circuito começar com RESET ativo durante 10 ps. | ||

| + | |||

| + | *Após verificar que a simulação do circuito está funcionando, configurar um FPGA para implementar este circuito. Existem duas opções de kit disponíveis com displays de sete segmentos. As informações necessárias estão em [[Preparando para gravar o circuito lógico no FPGA]]. | ||

| + | :* Ao utilizar o kit DE2-115 da TERASIC, utilize os pinos (clk = CLOCK_50: PIN_Y2, rst = KEY[0]: PIN_M23, ssd = HEX0-5[0-6]: PIN_G18 - PIN_H22 ...). | ||

| + | {{collapse top| definição dos pinos}} | ||

| + | <pre> | ||

| + | </pre> | ||

| + | {{collapse bottom}} | ||

| + | :*Ao utilizar o kit Mercúrio IV da MACNICA, utilize os pinos (clk = CLOCK_50MHz: PIN_T1, led = DISP0_D[7] : PIN_W1, ssd = DISP0_D[0-6]: PIN_V2 - PIN_W2). | ||

| + | {{collapse top| definição dos pinos}} | ||

| + | <pre> | ||

| + | set_location_assignment PIN_T1 -to clk50MHz | ||

| + | set_location_assignment PIN_V21 -to rst_in | ||

| + | set_location_assignment PIN_R5 -to ssd_D[0] | ||

| + | set_location_assignment PIN_T5 -to ssd_D[1] | ||

| + | set_location_assignment PIN_T3 -to ssd_D[2] | ||

| + | set_location_assignment PIN_T4 -to ssd_D[3] | ||

| + | set_location_assignment PIN_M6 -to ssd_D[4] | ||

| + | set_location_assignment PIN_N7 -to ssd_D[5] | ||

| + | set_location_assignment PIN_N6 -to ssd_D[6] | ||

| + | set_location_assignment PIN_V2 -to ssd_U[0] | ||

| + | set_location_assignment PIN_V1 -to ssd_U[1] | ||

| + | set_location_assignment PIN_U2 -to ssd_U[2] | ||

| + | set_location_assignment PIN_U1 -to ssd_U[3] | ||

| + | set_location_assignment PIN_Y2 -to ssd_U[4] | ||

| + | set_location_assignment PIN_Y1 -to ssd_U[5] | ||

| + | set_location_assignment PIN_W2 -to ssd_U[6] | ||

| + | set_location_assignment PIN_W1 -to clk_1seg | ||

| + | </pre> | ||

| + | {{collapse bottom}} | ||

| + | :* Analise o diagrama esquemático como funcionam as chaves e também o tipo de display. Note que no projeto o signal RST foi descrito como normalmente ALTO, podendo ser necessário acrescentar um inversor para ter o funcionamento correto. O [[Display de 7 segmentos]] da DE2-115 é do tipo cátodo comum, enquanto que na MERCURIO IV ele é do tipo ânodo comum. | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | ; Aula 39 (6 abr): | ||

| + | |||

| + | FUNCTION e PROCEDURE (são chamados de subprogramas), e podem ser construídos em um PACKAGE, ENTITY, ARCHITECTURE, ou PROCESS. | ||

| + | |||

| + | A instrução '''ASSERT''' é útil para verificar as entradas de um subprograma. Seu propósito não é criar circuito, mas assegurar que certos requisitos são atendidos durante a síntese e/ou simulação. Pode ser condicional ou incondicional (condição_booleana = FALSE). A sintaxe da instrução é: | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] assert condição_booleana | ||

| + | [report mensagem] | ||

| + | [severity nivel_severidade]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | A mensagem pode ser criada usando STRINGs que podem ser concatenadas. | ||

| + | |||

| + | O nível de severidade pode ser NOTE (para passar informação para o compilador/simulator), WARNING (para informar que algo não usual ocorreu), ERROR (para informar que alguma condição não usual "sério" ocorreu), ou FAILURE (para informar que uma condição não aceitável ocorreu). Normalmente o compilador para quando ocorre um ERROR ou FAILURE. ERROR é o valor "default" [https://www.ics.uci.edu/~jmoorkan/vhdlref/assert.html]. | ||

| + | |||

| + | :* A '''FUNCTION''': declaração, uso, mapeamento posicional x nominal, PURE x IMPURE. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | function nome_funçao (lista_parametros_entrada) return tipo_saida is | ||

| + | declarações | ||

| + | begin | ||

| + | afirmações sequenciais | ||

| + | end function; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :* Uso de '''FUNCTION''' e '''ASSERT'''. | ||

| + | |||

| + | Abaixo segue um exemplo de cálculo do '''log2''' de um número inteiro. Pode ser usado para determinar o número de bits necessário para um número natural. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | function log2c (n : integer) return integer is | ||

| + | variable m , p : integer; | ||

| + | begin | ||

| + | m := 0; | ||

| + | p : = 1; | ||

| + | while p < n loop | ||

| + | m : = m + 1; | ||

| + | p := p * 2; | ||

| + | end loop; | ||

| + | return m; | ||

| + | end log2c; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :*Uso de '''PROCEDURE'''. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | procedure nome_procedimento (lista_parâmetros_entrada, lista_parâmetros_saída) is | ||

| + | declarações | ||

| + | begin | ||

| + | afirmações sequenciais | ||

| + | end procedure; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ;Exemplos de uso ASSERT, FUNCTION e PROCEDURE: | ||

| + | |||

| + | * Exemplo: Declaração de FUNCTION em ARCHITECTURE Ex.9.1 | ||

| + | :*Aplicação no projeto do '''timer0_9''' | ||

| + | |||

| + | * Exemplo: Declaração em FUNCTION PACKAGE Ex. 9.2 | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- FILE: comparator.vhd | ||

| + | -- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010. | ||

| + | |||

| + | library ieee; | ||

| + | use ieee.numeric_std.all; | ||

| + | use work.my_package.all; | ||

| + | entity organizer is | ||

| + | generic (size : natural := 3); | ||

| + | port | ||

| + | ( | ||

| + | x : in UNSIGNED(2 to 5); | ||

| + | y : out UNSIGNED(size - 1 downto 0) | ||

| + | ); | ||

| + | end entity; | ||

| + | architecture organizer of organizer is | ||

| + | begin | ||

| + | y <= order_and_fill(x, size); | ||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- FILE: my_pkg.vhd | ||

| + | -- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 | ||

| + | |||

| + | library ieee; | ||

| + | use ieee.numeric_std.all; | ||

| + | package my_package is | ||

| + | function order_and_fill (input : UNSIGNED; bits : natural) return UNSIGNED; | ||

| + | end package; | ||

| + | |||

| + | package body my_package is | ||

| + | function order_and_fill (input : UNSIGNED; bits : natural) return UNSIGNED is | ||

| + | variable a : UNSIGNED(input'LENGTH - 1 downto 0); | ||

| + | variable result : UNSIGNED(bits - 1 downto 0); | ||

| + | begin | ||

| + | assert (input'LENGTH <= bits) | ||

| + | report "Improper input size!" | ||

| + | severity FAILURE; | ||

| + | if (input'LEFT > input'RIGHT) then | ||

| + | a := input; | ||

| + | else | ||

| + | for i in a'range loop | ||

| + | a(i) := input(input'LEFT + i); | ||

| + | end loop; | ||

| + | end if; | ||

| + | if (a'LENGTH < bits) then | ||

| + | result(bits - 1 downto a'LENGTH) := (others => '0'); | ||

| + | result(a'LENGTH - 1 downto 0) := a; | ||

| + | else | ||

| + | result := a; | ||

| + | end if; | ||

| + | return result; | ||

| + | end function; | ||

| + | end package body; | ||

| + | </syntaxhighlight> | ||

| + | |||

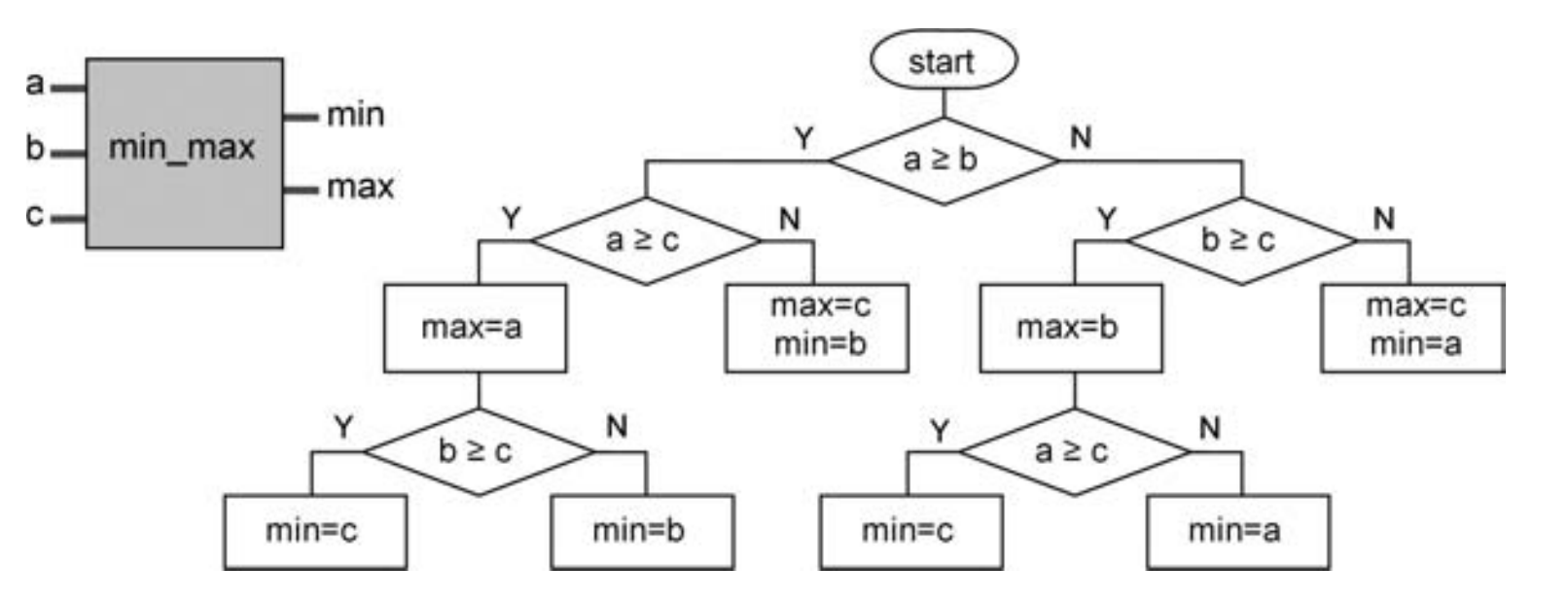

| + | * Exemplo: min_max Ex.9.4 | ||

| + | {{fig|6.1|Fluxograma da PROCEDURE min_max| fluxogramMinMax.png| 600 px | pag. 232 de <ref name="PEDRONI2010b"/> }} | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- FILE: comparator.vhd | ||

| + | -- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010. | ||

| + | |||

| + | use work.my_package.all; | ||

| + | |||

| + | entity comparator is | ||

| + | port | ||

| + | ( | ||

| + | a, b, c : in integer range 0 to 255; | ||

| + | min, max : out integer range 0 to 255 | ||

| + | ); | ||

| + | end entity; | ||

| + | |||

| + | architecture comparator of comparator is | ||

| + | begin | ||

| + | min_max(a, b, c, min, max); | ||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- FILE: my_pkg.vhd | ||

| + | -- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010. | ||

| + | |||

| + | |||

| + | package my_package is | ||

| + | procedure min_max ( | ||

| + | signal a, b, c : in integer; | ||

| + | signal min, max : out integer | ||

| + | ); | ||

| + | end package; | ||

| + | package body my_package is | ||

| + | procedure min_max ( | ||

| + | signal a, b, c : in integer range 0 to 255; | ||

| + | signal min, max : out integer range 0 to 255) is | ||

| + | begin | ||

| + | if (a >= b) then | ||

| + | if (a >= c) then | ||

| + | max <= a; | ||

| + | if (b >= c) then | ||

| + | min <= c; | ||

| + | else | ||

| + | min <= b; | ||

| + | end if; | ||

| + | else | ||

| + | max <= c; | ||

| + | min <= b; | ||

| + | end if; | ||

| + | else | ||

| + | if (b >= c) then | ||

| + | max <= b; | ||

| + | if (a >= c) then | ||

| + | min <= c; | ||

| + | else min <= a; | ||

| + | end if; | ||

| + | else | ||

| + | max <= c; | ||

| + | min <= a; | ||

| + | end if; | ||

| + | end if; | ||

| + | end procedure; | ||

| + | end package body; | ||

| + | |||

| + | </syntaxhighlight> | ||

| + | |||

| + | ::* Exercícios: 9.1 a 9.4, 9.6 a 9.9 | ||

| + | :* Ver pag. 213 a 239 de <ref name="PEDRONI2010b"/>) | ||

| + | |||

| + | <!-- | ||

| + | ;Aula XX e XX (24 e 26 jun): | ||

| + | * Implementação de um serializador e um deserializador usando componentes. | ||

| + | |||

| + | : Componente 1 - Divisor de Clock, con o valor da divisão configurável pelo '''generic N''' | ||

| + | entity div_clk is | ||

| + | entrada clk_in | ||

| + | saída clk_out | ||

| + | : Componente 2 - Registrador de deslocamento com entrada serial e paralelo e saída serial e paralelo com N FF, configurável pelo '''generic N''' | ||

| + | entity shift_reg is | ||

| + | entradas clk_in, rst_in, ena_in, d_in[N-1..0], s_in | ||

| + | saídas d_out[N-1..0], s_out | ||

| + | |||

| + | : Componente 3 - Porta paralela com N entradas, configurável pelo '''generic N'''. | ||

| + | entity parallel_reg is | ||

| + | entradas clk_in, rst, ena, d_in[N-1..0] | ||

| + | saídas d_out[N-1..0] | ||

| + | |||

| + | : Outros componentes necessários. | ||

| + | |||

| + | * Simular o serializador e deserializador com ModelSim. | ||

| + | * Implementar em um kit FPGA (Mercurio IV) usando o '''lab home office'''. | ||

| + | |||

| + | ;Aula XX XX (1 e 3 jul): | ||

| + | * Atividade extraclasse, ficou dividida em: | ||

| + | :*Equipe 1: Detalhar a '''architecture''' do componente '''div_clk''' e fazer sua simulação. | ||

| + | ::-Verificar se o '''clk_out''' está alto durante apenas um período do '''clk_in'''. Esse período deve ser entre duas bordas de descida do '''clk_in'''. | ||

| + | :*Equipe 1: Detalhar a '''architecture''' do componente '''parallel_reg''' e fazer sua simulação. | ||

| + | :*Equipe 2: Detalhar a '''architecture''' do componente '''shift_reg''', e fazer a simulação. | ||

| + | ::-Verificar a transferência dos dados da entrada serial para a saída paralela (função Desserializador). | ||

| + | ::-Verificar a transferência dos dados da entrada paralela para a saída serial (função Serializador). | ||

| + | ::-Verificar a transferência dos dados da entrada serial para a saída serial (função Delay). | ||

| + | ::-Verificar a transferência dos dados da entrada paralela para a saída paralela (função porta Paralela). | ||

| + | ::-Verificar a possibilidade de utilizar esse componente no lugar do '''parallel_reg'''. | ||

| + | * As equipes devem terminar de simular os componentes e integrá-los no projeto. | ||

| + | * Após a integração deverá ser feita a simulação do sistema completo. | ||

| + | * Mapear os pinos do FPGA para fazer o teste de funcionamento com um baud-rate de 1bit/s, entrada chaves, saídas leds. | ||

| + | --> | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | ===Unidade 7 - Maquinas de Estado Finitas=== | ||

| + | {{collapse top| expand=true | Unidade 7 - Maquinas de Estado Finitas}} | ||

| + | * 3 AULAS | ||

| + | |||

| + | ; Aula 40 (8 abr): | ||

| + | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

| + | :* O que é uma FSM - Finite State Machine | ||

| + | :* Modelo de FSM | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | LIBRARY ieee; | ||

| + | USE ieee.std_logic_1164.ALL; | ||

| + | ---------------------------------------------------------- | ||

| + | ENTITY < entity_name > IS | ||

| + | PORT ( | ||

| + | clk, rst : IN STD_LOGIC; | ||

| + | input : IN < data_type > ; | ||

| + | output : OUT < data_type >); | ||

| + | END < entity_name > ; | ||

| + | ---------------------------------------------------------- | ||

| + | ARCHITECTURE < architecture_name > OF < entity_name > IS | ||

| + | TYPE state IS (A, B, C, ...); | ||

| + | SIGNAL pr_state, nx_state : state; | ||

| + | -- ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute | ||

| + | -- ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential"; | ||

| + | -- ATTRIBUTE SYN_ENCODING OF state : TYPE IS "safe"; | ||

| + | BEGIN | ||

| + | ------Logica Sequencial da FSM:------------ | ||

| + | PROCESS (clk, rst) | ||

| + | BEGIN | ||

| + | IF (rst = '1') THEN | ||

| + | pr_state <= A; | ||

| + | ELSIF (clk'EVENT AND clk = '1') THEN | ||

| + | pr_state <= nx_state; | ||

| + | END IF; | ||

| + | END PROCESS; | ||

| + | ------Logica Combinacional da FSM:------------ | ||

| + | PROCESS (pr_state, input) | ||

| + | BEGIN | ||

| + | ------Valores default das saidas------------ | ||

| + | output <= < value > ; | ||

| + | CASE pr_state IS | ||

| + | WHEN A => | ||

| + | output <= < value > ; -- apenas se diferente do valor default | ||

| + | IF (input =< value >) THEN | ||

| + | nx_state <= B; | ||

| + | ... | ||

| + | ELSE | ||

| + | nx_state <= A; | ||

| + | END IF; | ||

| + | WHEN B => | ||

| + | output <= < value > ; -- apenas se diferente do valor default | ||

| + | IF (input =< value >) THEN | ||

| + | nx_state <= C; | ||

| + | ... | ||

| + | ELSE | ||

| + | nx_state <= B; | ||

| + | END IF; | ||

| + | WHEN ... | ||

| + | END CASE; | ||

| + | END PROCESS; | ||

| + | ------Seção de Saída (opcional):------- | ||

| + | PROCESS (clk, rst) | ||

| + | BEGIN | ||

| + | IF (rst = '1') THEN | ||

| + | new_output <= < value > ; | ||

| + | ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0' | ||

| + | new_output <= output; | ||

| + | END IF; | ||

| + | END PROCESS; | ||

| + | END < architecture_name > ; | ||

| + | </syntaxhighlight> | ||

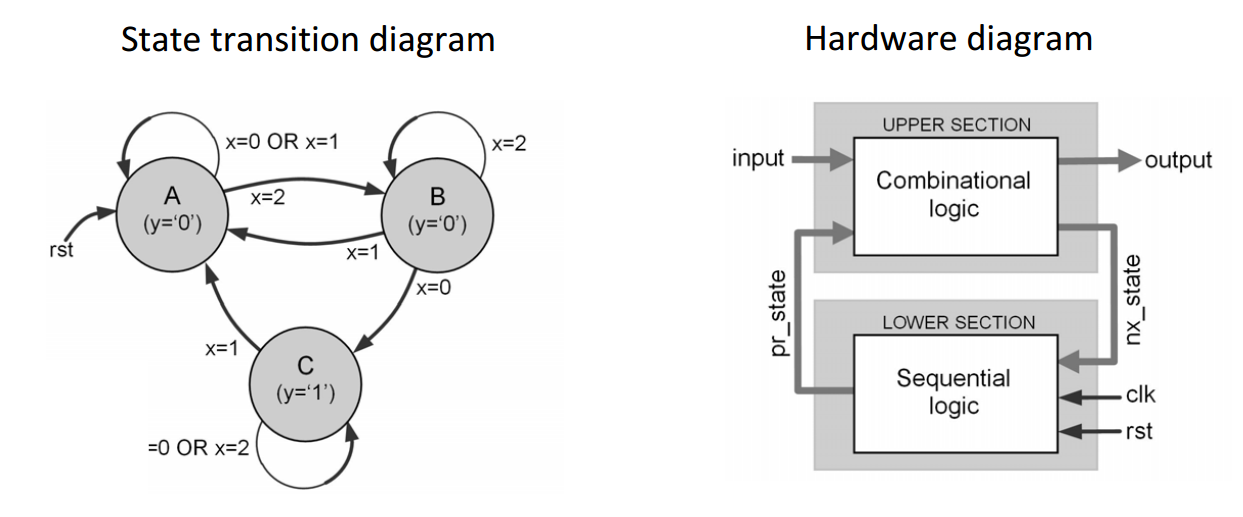

| + | :* Usando o template acima descreva em VHDL a FSM indicada na Figura 11.1. | ||

| + | {{fig|7.1|Exemplo de diagrama de estados de uma FSM Fig11.1(a) e implementação em hardware da FSM Fig11.2(a)|Fig11_1_FSM.png|800 px|Figura 11.1 e 11.2 de <ref name="PEDRONI2010b"/>}} | ||

| + | :* Faça a simulação da FSM com Modelsim utilizando um testbench em VHDL que faça a FSM seguir os estados | ||

| + | :rst -> A -(x=0)-> A -(x=1)-> A -(x=2)-> B -(x=2)-> B -(x=0)-> C -(x=0)-> C -(x=2)-> C -(x=1)-> A -(x=2)-> B -(x=1)-> A. | ||

| + | :: Ver pag. 277 a 280 de <ref name="PEDRONI2010b"/> | ||

| + | :: Ver [https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/qts/archives/quartusii_handbook_archive_131.pdf Quartus II Handbook Version 13.1: Manually Specifying Enumerated Types Using the enum_encoding Attribute, pag 16-37] sobre a atribuição manual do enum_encoding. | ||

| + | :: Note que o uso desse atributo faz com que o compilar do Quartus não reconheça a FSM, mas use logica regular para representar o sistema. | ||

| + | :: Ver [https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/qts/archives/quartusii_handbook_archive_131.pdf Quartus II Handbook Version 13.1: Safe State Machines, pag 16-38]. | ||

| + | |||

| + | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

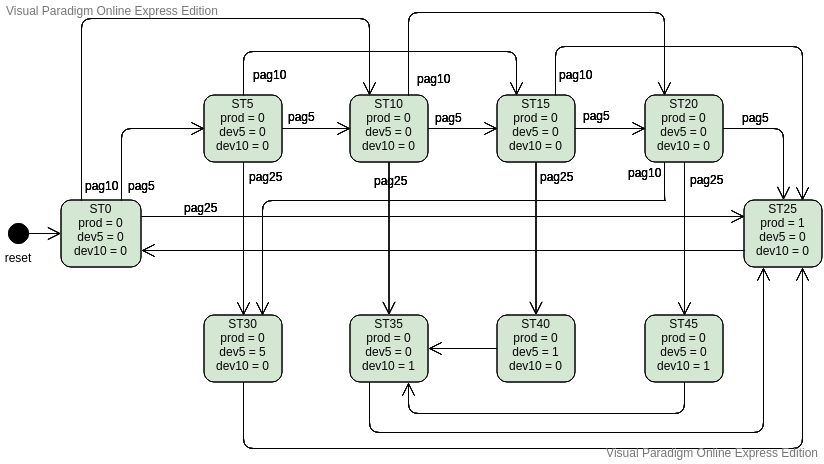

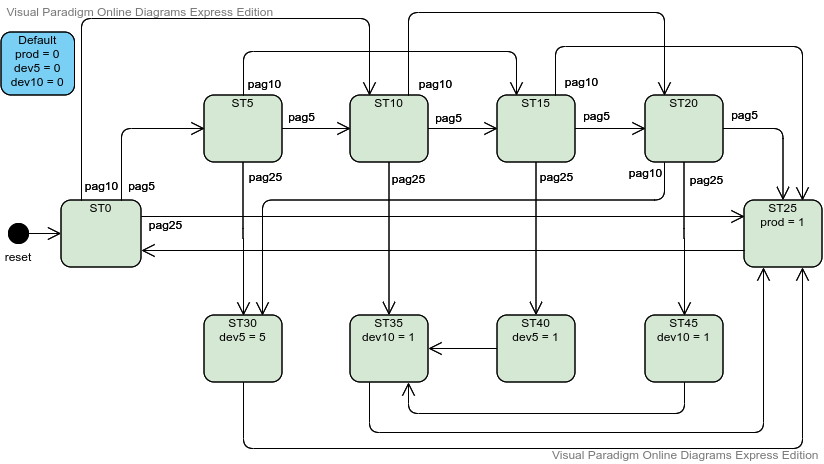

| + | :* Máquina de vender doces | ||

| + | ::*Use o template da FSM para modelar o sistema mostrado na figurar a seguir. | ||

| + | |||

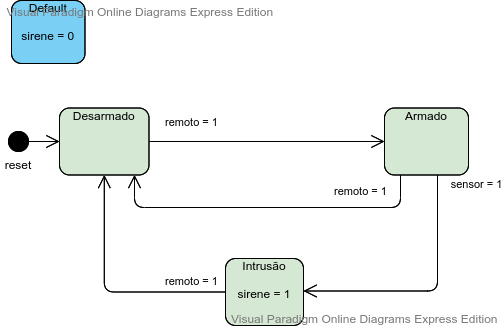

| + | {{fig|7.2|FSM - Máquina de vender doces (diagrama de estados)|FSM_MVD.png|800 px|Adaptado da Figura 11.3 de <ref name="PEDRONI2010b"/> }} | ||

| + | |||

| + | {{fig|7.3|FSM - Máquina de vender doces (diagrama de estados com default |FSM_MVD_default.png|800 px|}} | ||

| + | |||

| + | ::*Simule a FSM com Modelsim utilizando um testbench em VHDL para gerar o teste mostrado na figura abaixo. | ||

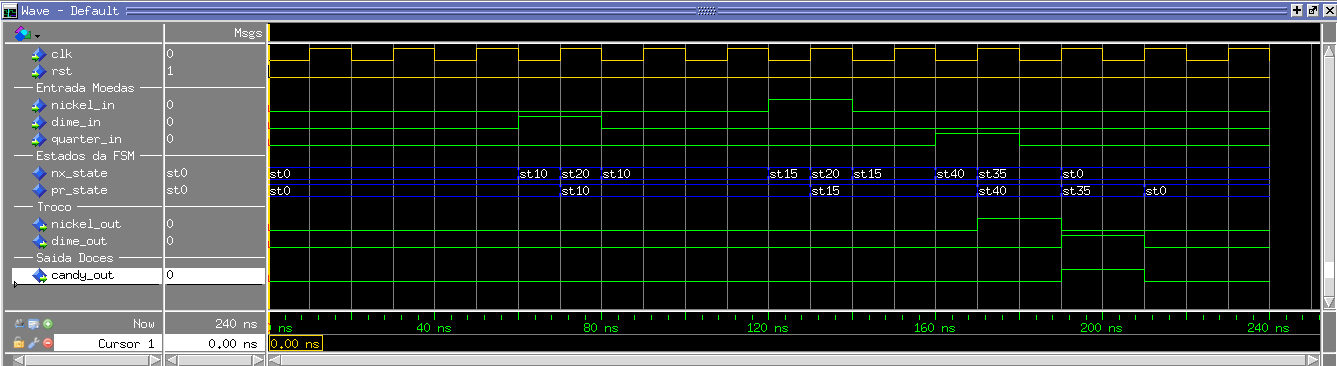

| + | {{fig|7.4|FSM - Máquina de vender doces (simulação)|FSM_tb40.png|800 px|}} | ||

| + | |||

| + | :* Exercício: Altere a FSM para vender doces que custam 30 centavos. Considere que as moedas aceitas são 5, 10, 25 e 50 centavos. Desenho primeiro a FSM e em seguida implemente-a em VHDL e faça a simulação. | ||

| + | :: Ver pag. 281 a 282 de <ref name="PEDRONI2010b"/> | ||

| + | :: '''Dica''': para desenhar a FSM recomendo utilizar um software on-line para tal finalidade. Por Ex. [https://online.visual-paradigm.com/pt/ Visual Paradigm]. | ||

| + | |||

| + | ; Aula 41 (12 abr): | ||

| + | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

| + | :* O problema de oscilando entre os estados em FSM. | ||

| + | |||

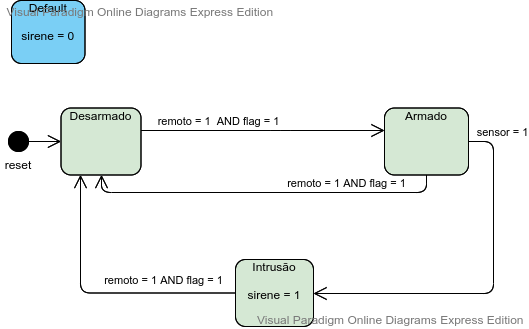

| + | {{fig|7.5| FSM - alarme (oscilando entre os estados quando remoto é 1) |alarme_erro.png|500 px|Adaptado de Figura 11.9(a) de <ref name="PEDRONI2010b"/>}} | ||

| + | |||

| + | ::* Solução através do uso de FLAG | ||

| + | |||

| + | {{fig|7.6| FSM - alarme (solução com flag) |alarme_flag.png|500 px|Adaptado de Figura 11.9(b) de <ref name="PEDRONI2010b"/>}} | ||

| + | |||

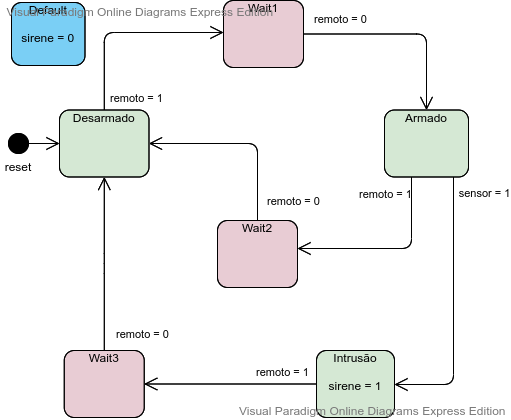

| + | ::* Solução através do uso de estados de WAIT adicionais. | ||

| + | |||

| + | {{fig|7.7| FSM - alarme (solução com estados de WAIT) |alarme_wait.png|500 px|Adaptado de Figura 11.9(c) de <ref name="PEDRONI2010b"/>}} | ||

| + | |||

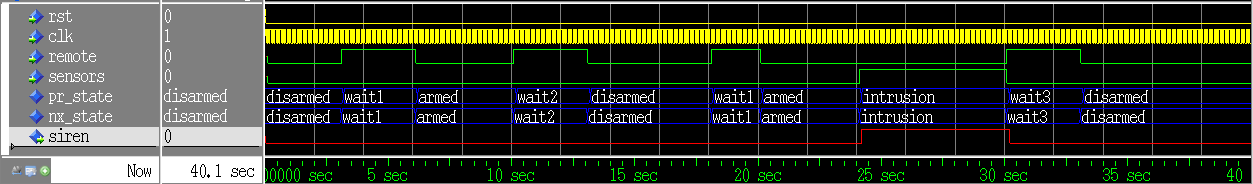

| + | {{fig|7.8| Simulação da FSM - alarme (solução com estados de WAIT) |simulation_alarme_wait.png|800 px|}} | ||

| + | |||

| + | :: Ver pag. 292 a 297 de <ref name="PEDRONI2010b"/> | ||

| + | *Exercício: Faça o download do arquivo simple_car_alarm.qar, disponível no Moodle da disciplina e realize as seguintes avaliações: | ||

| + | :#Perceba que existem 4 versões para o mesmo Alarme de Carro. Realize a simulação no ModelSim das 4 versões e perceba qual é a diferença de funcionamento desses circuitos. | ||

| + | :#Anote o número de elementos em cada versão. | ||

| + | :#Qual versão é a mais adequada na sua opinião? | ||

| + | :#Modifique a sua escolha para que o alarme não possa ser ativado se o "sensor" estiver em "1". | ||

| + | :#Analise o arquivo tb_vX.do e modifique-o para testar também essa nova condição. A simulação deve obrigatoriamente fazer o sistema passar por todos os estados e todas as transições. | ||

| + | :#Implemente a nova versão como uma nova arquitetura "fsm_v5", e escrever o arquivo de simulação "tbv5.do". | ||

| + | :#Salve as telas da simulação ("v5_sim.png"), tela da fsm ("v5_fsm.png"), tela do RTL ("v5_rtl.png"). | ||

| + | :#Acrescente os novos arquivos no projeto e salve o novo .qar | ||

| + | |||

| + | ====ATUAL==== | ||

| + | ;Aula 42 (15 abr): | ||

| + | |||

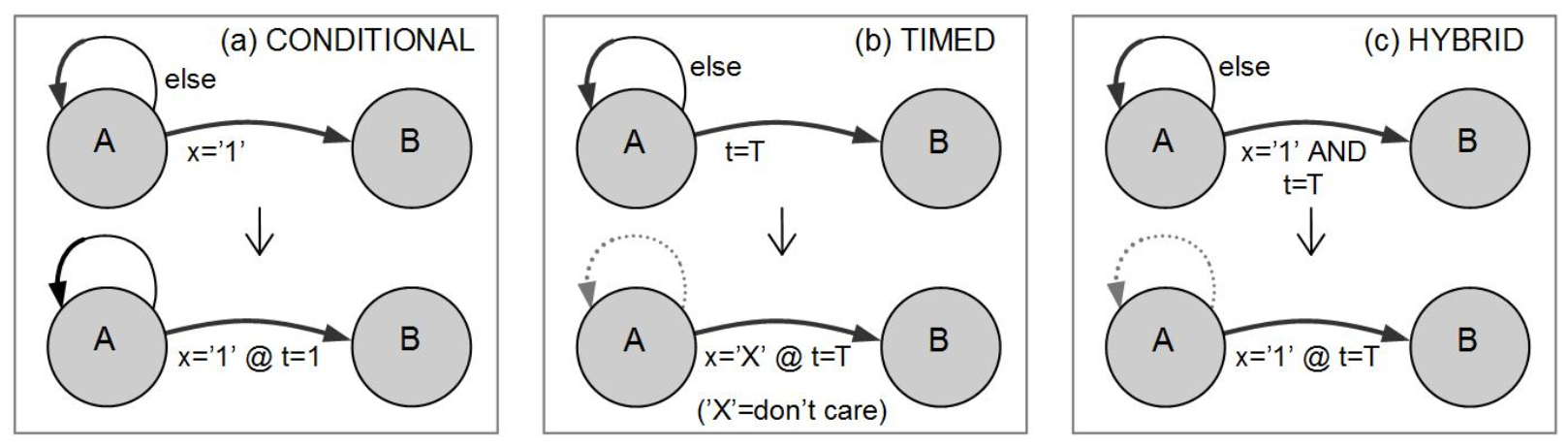

| + | * Projeto de FSM temporizadas (nas quais as transições são ativadas também pelo tempo). | ||

| + | {{fig|7.9| Tipos de FSM (Condicional, Temporizada e Hibrida) |FSM_type.png|800 px|Figura 11.12 de <ref name="PEDRONI2010b"/>}} | ||

| + | |||

| + | * Modelo de FSM temporizada | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | LIBRARY ieee; | ||

| + | USE ieee.std_logic_1164.ALL; | ||

| + | ---------------------------------------------------------- | ||

| + | ENTITY < entity_name > IS | ||

| + | PORT ( | ||

| + | clk, rst : IN STD_LOGIC; | ||

| + | input : IN < data_type > ; | ||

| + | output : OUT < data_type >); | ||

| + | END < entity_name > ; | ||

| + | ---------------------------------------------------------- | ||

| + | ARCHITECTURE < architecture_name > OF < entity_name > IS | ||

| + | TYPE state IS (A, B, C, ...); | ||

| + | SIGNAL pr_state, nx_state : state; | ||

| + | signal timer: integer range 0 to MAX; | ||

| + | -- ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute | ||

| + | -- ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential"; | ||

| + | BEGIN | ||

| + | ------Logica Sequencial da FSM:------------ | ||

| + | PROCESS (clk, rst) | ||

| + | variable count: integer range o to MAX; | ||

| + | BEGIN | ||

| + | IF (rst = '1') THEN | ||

| + | pr_state <= A; | ||

| + | count := 0; | ||

| + | ELSIF (clk'EVENT AND clk = '1') THEN | ||

| + | count := count + 1; | ||

| + | if (count >= timer) then | ||

| + | pr_state <= nx_state; | ||

| + | count := 0; | ||

| + | end if; | ||

| + | END IF; | ||

| + | END PROCESS; | ||

| + | ------Logica Combinacional da FSM:------------ | ||

| + | PROCESS (pr_state, input) | ||

| + | BEGIN | ||

| + | ------Valores default das saidas------------ | ||

| + | output <= < value >; | ||

| + | ------Valores default do timer------------ | ||

| + | timer <= <value>; | ||

| + | CASE pr_state IS | ||

| + | WHEN A => | ||

| + | output <= < value > ; -- apenas se diferente do valor default | ||

| + | IF (input =< value >) THEN | ||

| + | timer <= <value>; -- apenas se diferente do valor default | ||

| + | nx_state <= B; | ||

| + | ... | ||

| + | ELSE | ||

| + | timer <= <value>; -- apenas se diferente do valor default | ||

| + | nx_state <= A; | ||

| + | END IF; | ||

| + | WHEN B => | ||

| + | output <= < value > ; -- apenas se diferente do valor default | ||

| + | IF (input =< value >) THEN | ||

| + | timer <= <value>; -- apenas se diferente do valor default | ||

| + | nx_state <= C; | ||

| + | ... | ||

| + | ELSE | ||

| + | timer <= <value>; -- apenas se diferente do valor default | ||

| + | nx_state <= B; | ||

| + | END IF; | ||

| + | WHEN ... | ||

| + | END CASE; | ||

| + | END PROCESS; | ||

| + | ------Seção de Saída (opcional):------- | ||

| + | PROCESS (clk, rst) | ||

| + | BEGIN | ||

| + | IF (rst = '1') THEN | ||

| + | new_output <= < value > ; | ||

| + | ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0' | ||

| + | new_output <= output; | ||

| + | END IF; | ||

| + | END PROCESS; | ||

| + | END < architecture_name > ; | ||

| + | </syntaxhighlight> | ||

| + | :Ver pag. 298 a 301 de <ref name="PEDRONI2010b"/> | ||

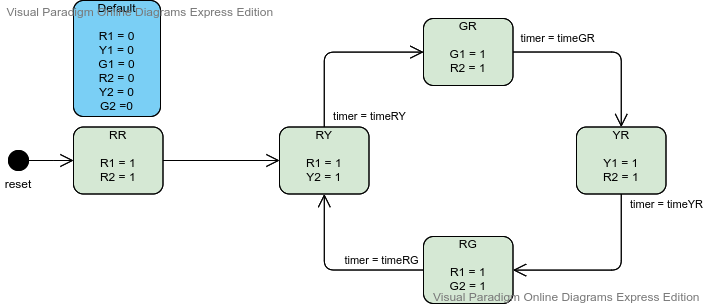

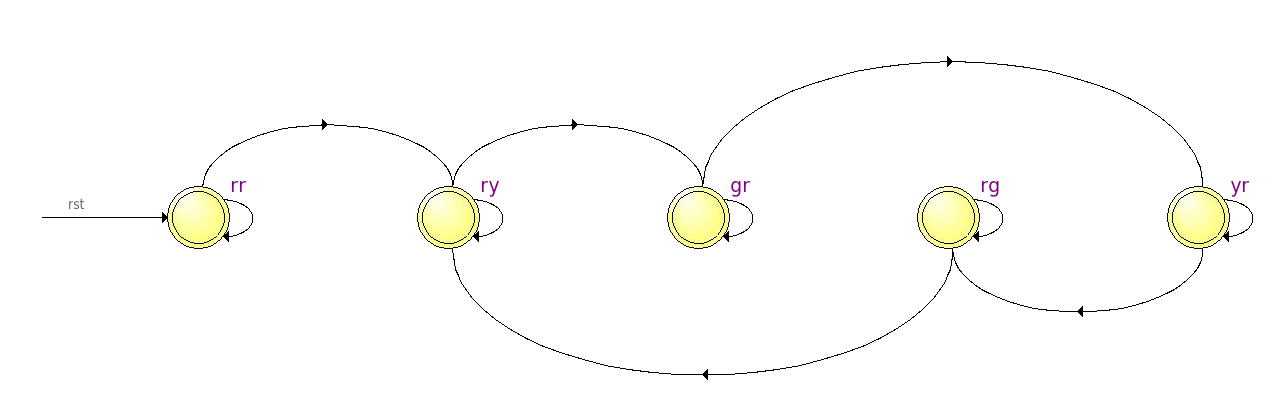

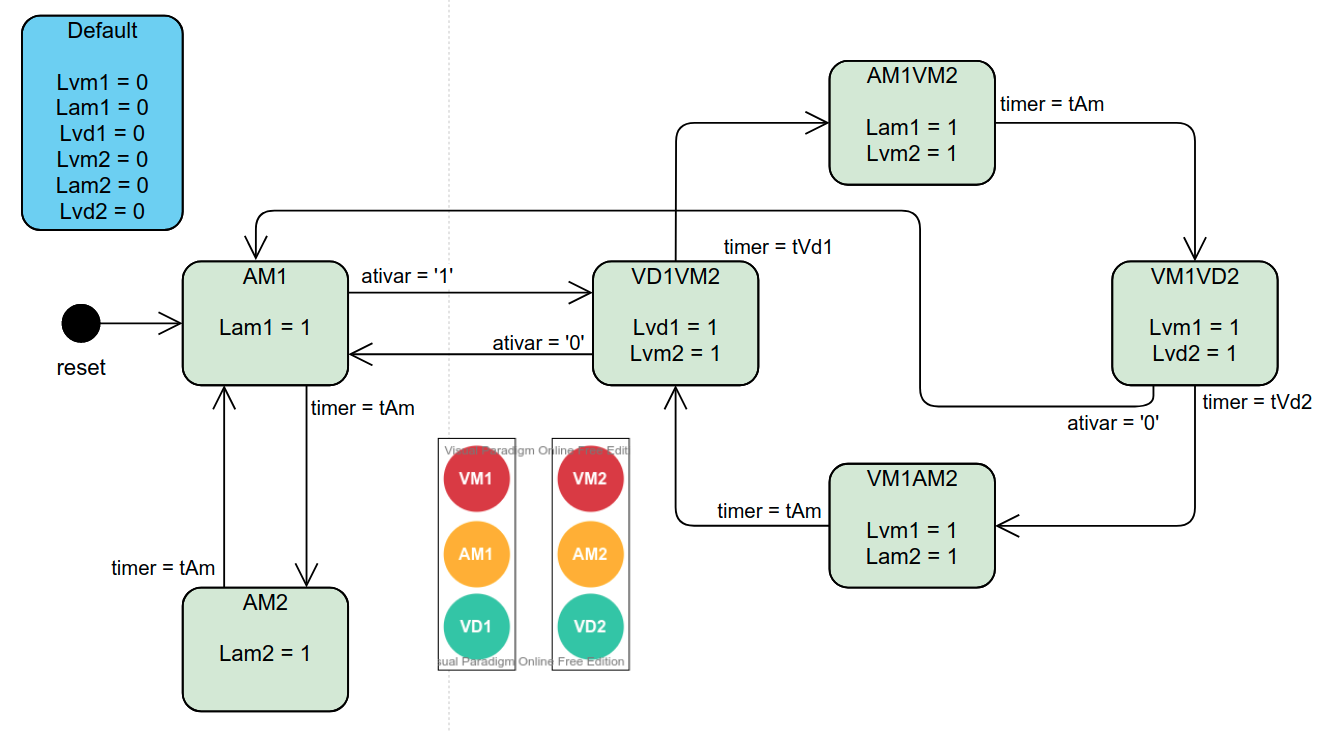

| + | ;Exemplo de FSM temporizada - semáforo temporizado: | ||

| + | * Usando o template acima descreva em VHDL a FSM de um controlador de semáforo Regular indicado pela FSM da figura abaixo: | ||

| + | {{fig|7.10| Diagrama de estados do controlador de semáforo |Semaforo_FSM_v2.png|800 px|}} | ||

| + | |||

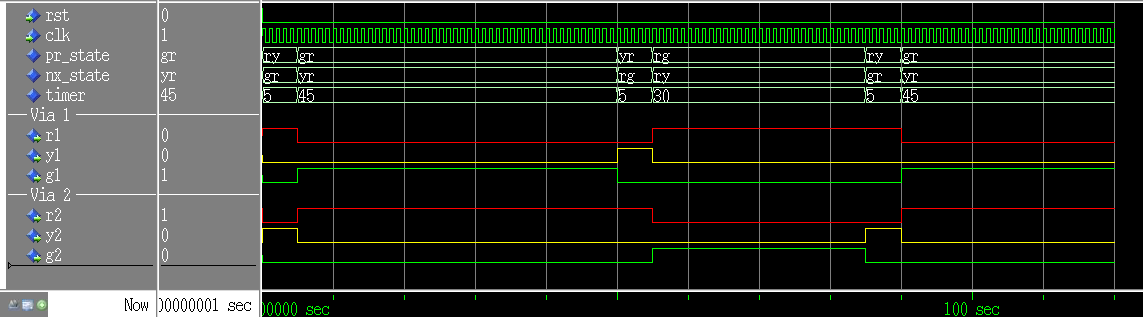

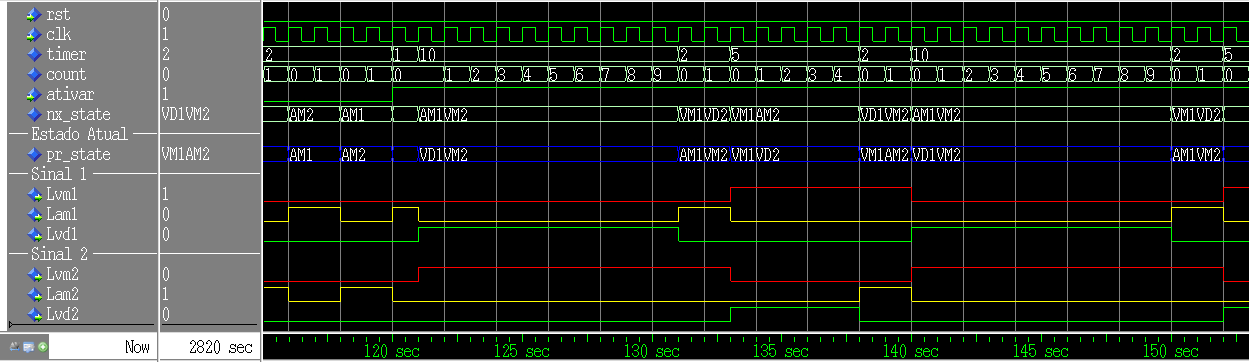

| + | {{fig|7.11| Simulação do controlador de semáforo no Modelsim |Semaforo_FSM_v2_ModelSim.png|800 px|}} | ||

| + | |||

| + | {{collapse top| bg=lightyellow | Exercício - Semaforo}} | ||

| + | * Usando o template acima descreva em VHDL a FSM de um controlador de semáforo Regular da Figura 11.15 (pag. 304 de <ref name="PEDRONI2010b"/>). | ||

| + | {{fig|7.12| Diagrama de estados do controlador de semáforo |Semaforo_FSM_VD.png|800 px| Adaptado de Figura 11.15 de <ref name="PEDRONI2010b"/>}} | ||

| + | |||

| + | {{fig|7.13| Diagrama de estados do Quartus do controlador de semáforo |Semaforo_FSM.png|800 px|}} | ||

| + | |||

| + | * Para definir as temporizações utilize GENERICs que permitam instanciar diferentes semáforos em um projeto de controle de tráfego de uma avenida. | ||

| + | : Para uma instância do semáforo S1 use (timeRY = 2 segundos; timeGR = 40 segundos; timeYR = 2 segundos; timeRG = 15 segundos. | ||

| + | : Para uma instância do semáforo S2 use (timeRY = 5 segundos; timeGR = 90 segundos; timeYR = 5 segundos; timeRG = 30 segundos. | ||

| + | * Considere que o sinal de clock tem período de 1 segundo. | ||

| + | * Realize a simulação dos semáforos S1 e S2, destacando as saídas com as cores correspondentes, conforme mostrado abaixo: | ||

| + | {{fig|7.14| Simulação do controlador de semáforo no Modelsim |Semaforo_ModelSim.png|800 px|}} | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | {{collapse bottom}} | ||

| + | |||

| + | ==Avaliações== | ||

| + | Nas avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues: | ||

| + | <!-- | ||

| + | *[[Media:VHDL_QRC-Qualis.pdf | VHDL QUICK REFERENCE CARD]] - Qualis | ||

| + | *[[Media:VHDL1164_QRC-Qualis.pdf | VHDL 1164 PACKAGES QUICK REFERENCE CARD]] Qualis | ||

| + | --> | ||

| + | *[[Media:VHDL_QRC-SynthWorks.pdf | VHDL Quick Reference]] - SynthWorks | ||

| + | *[[Media:VHDL_Type_Operators_QR-SynthWorks.pdf | VHDL Types and Operators Quick Reference]] - SynthWorks | ||

| + | *[[Media:ModelSim_QR-SynthWorks.pdf |ModelSim Quick Reference]] - SynthWorks | ||

| + | *[[Media:Tabelas_Pedroni.pdf | Tabelas das figuras 3.6, 3.10 e 4.1]] do livro do Pedroni. | ||

| + | *[[Arquivo:Numeric_std_conversions.png | Diagrama de conversões de tipos numéricos no pacote Numeric_std ]] | ||

| + | ::Dica use também como fonte de consulta os '''templates''' do Quartus. | ||

::Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados. | ::Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados. | ||

| + | |||

| + | ===Projeto Final (PF)=== | ||

| + | * O projeto final é uma atividade de avaliação que será desenvolvida de forma individual. Consiste no desenvolvimento de um sistema que aplica os conhecimento adquiridos durante o semestre. A avaliação do projeto final corresponde a 36% do peso no conceito final. São avaliados no projeto final os quesitos: | ||

| + | :1) Sistema desenvolvido (projeto, simulação e realização, demonstração do hardware); (18%) | ||

| + | :2) Relatório com a documentação completa do projeto; (18%) | ||

| + | |||

| + | {{collapse top | expand = true | APF - Projeto Final - Sistema de controle de veículos em uma Avenida(Entrega e prazos ver Moodle)}} | ||

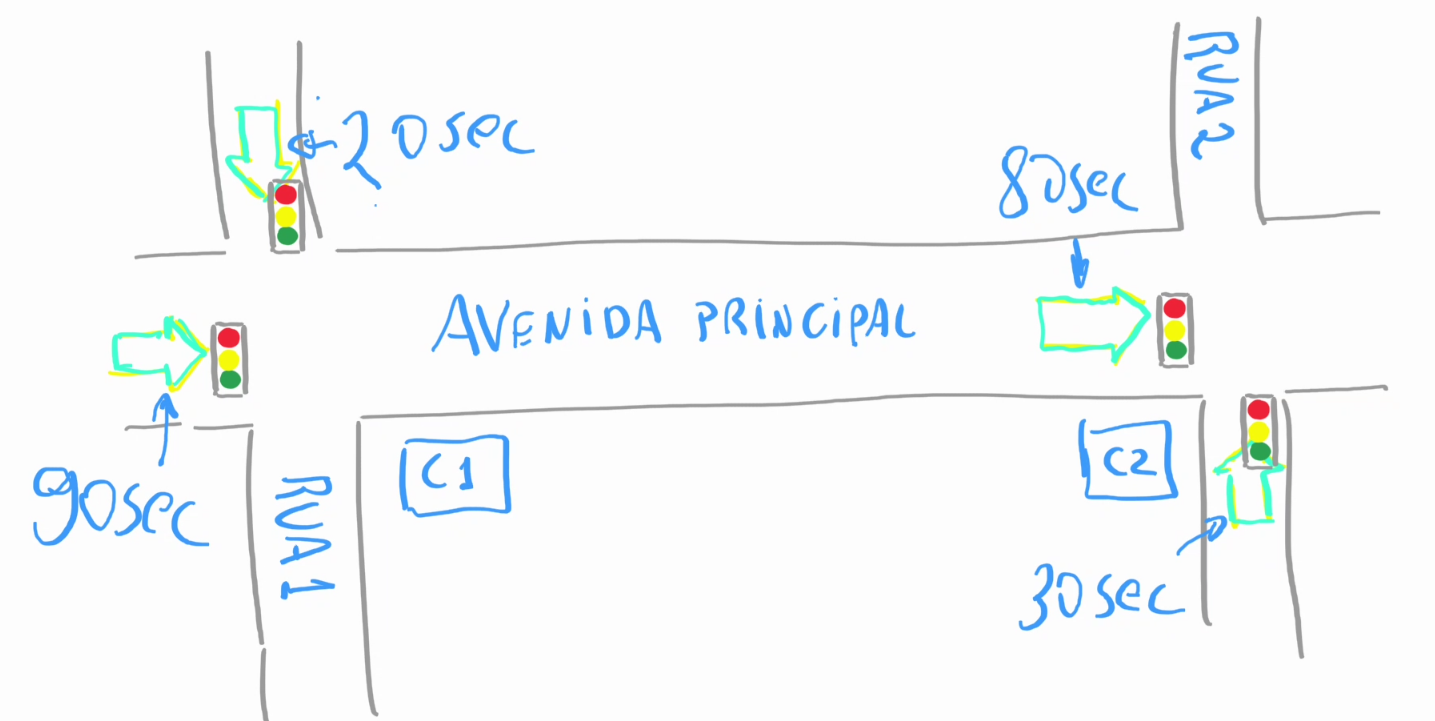

| + | * O projeto deverá desenvolver um sistema de controle de veículos para o sistema viário indicado na figura abaixo | ||

| + | {{fig|PF.1| Sistema viário para implantação de semáforos para controle de veículos |SemaforoAvenida2020-2.png|600 px| }} | ||

| + | |||

| + | * A descrição exata do funcionamento foi dada na aula do dia 20 abril, e dúvidas podem ser esclarecidas pelo Slack da turma. | ||

| + | |||

| + | ;Resumo de algumas especificações mínimas que o projeto devem atender: | ||

| + | |||

| + | * Serão implementados dois controladores de semáforos, cada um com dois grupos focais simples ("sinaleira de 3 lâmpadas") e um mostrador de dois dígitos que deverá mostrar o tempo de verde restante na '''Avenida Principal'''. | ||

| + | * Bônus (1 ponto) Mostrar o tempo restante de vermelho na avenida no mesmo mostrador. | ||

| + | * O tempo de verde da '''Avenida Principal''' é de 90 segundos no cruzamento com a Rua 1 e de 80 segundos no cruzamento com a Rua 2. | ||

| + | * O tempo de verde da '''Rua 1''' é de 20 segundos. | ||

| + | * O tempo de verde da '''Rua 2''' é de 20 segundos. | ||

| + | * O tempo de amarelo de todos grupos focais é de 2 segundos. | ||

| + | * Pode ser utilizado o amarelo piscante quando o semáforo estiver desativado, mas não é necessário. | ||

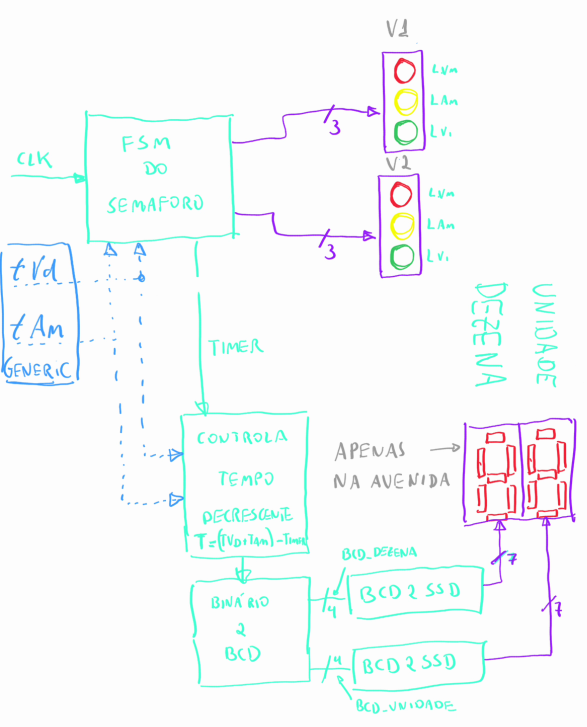

| + | * O controlador dos semáforos deverá ser descrito através de máquinas de estado finita com temporização (FSMt). | ||

| + | * Recomenda-se utilizar a temporização da FSM para calcular o tempo restante a ser mostrado nos mostradores de sete segmentos. | ||

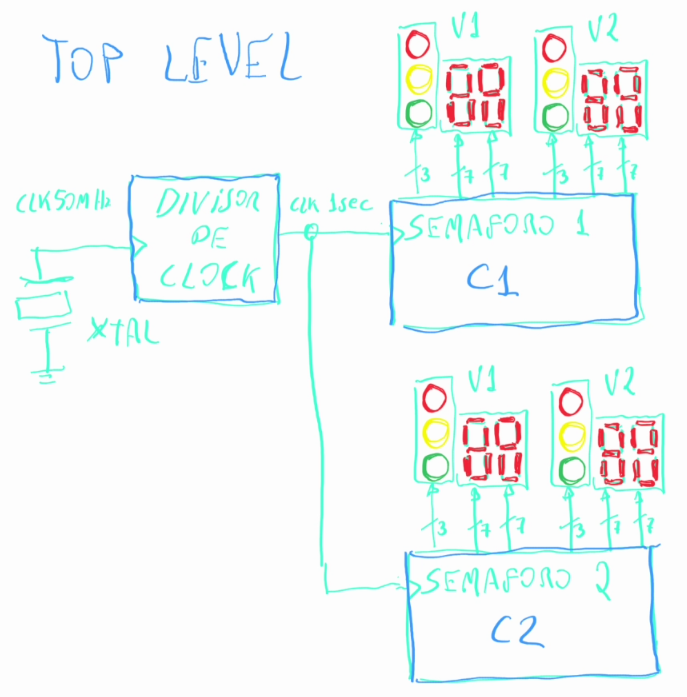

| + | * O projeto deverá ser estruturado em pelo menos dois níveis hierárquicos, conforme mostram as figuras a seguir. | ||

| + | {{fig|PF.2| Top Level do Sistema de controle de veículos |TL_SemaforoAvenida2020-2.png|400 px| }} | ||

| + | {{fig|PF.3| Detalhamento do componente Semáforo |Comp_SemaforoAvenida2020-2.png|400 px| }} | ||

| + | |||

| + | ;Testes mínimos: | ||

| + | * O sistema deverá ser simulado de modo a mostrar o correto funcionamento do semáforo. | ||

| + | * Deverá ser feita uma simulação do componente Semáforo, e uma simulação do projeto completo. | ||

| + | |||

| + | ;Entregas: | ||

| + | * Arquivo QAR do projeto, contendo todos os arquivos necessário para reproduzir o projeto. | ||

| + | * Arquivos .do com os testbench para o MODELSIM; | ||

| + | * Relatório técnico contendo os resultados em no máximo 20 paginas A4, em fonte 12pt. O relatório além das tabelas com os dados de '''frequência máxima''', número de '''elementos lógicos''', número de '''pinos''', deverá conter a figura dos circuitos RTL da ENTITY top level e do componente semáforo, bem como uma explicação do seu funcionamento. Também devem ser apresentadas as simulações funcionais e uma análise textual dos resultados obtidos. | ||

| + | |||

| + | |||

| + | ;Prazos das entregas do projeto: | ||

| + | *(28/abr) Entrega final do projeto: arquivos do projeto. | ||

| + | *(29/abr) Entrega do relatório final. | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | ==Referências== | ||

Edição atual tal como às 14h42min de 20 de abril de 2021

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 3 AULAS

| Unidade 1 - Introdução a disciplina | ||||

|---|---|---|---|---|

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 3 AULAS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Figura 2.1 - Fluxo simplificado do projeto de FPGA

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

Figura 2.2 - Código RTL do Exemplo 2.2

Figura 2.3 - Technology Map do Exemplo 2.2

Figura 2.4 - Chip Planner do Exemplo 2.2

Figura 2.5 - RTL 4 FF

Figura 2.6 - Simulação Funcional de 4 FF 100ns  Figura 2.7 - Simulação Temporal de 4 FF 100ns  Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possível verificar se o circuito atende as restrições de tempo.

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/std

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/ieee

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/mentor/arithmetic (Mentor Graphics) ls /opt/altera/13.0sp1/quartus/libraries/vhdl/synopsys/ieee (Synopsys)

ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END;

ARCHITECTURE circuit OF registered_comp_add IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END;

Figura 2.10 - Código RTL do Exemplo 2.3  Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso nestas mudanças. IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possivel verificar se o circuito atende as restrições de tempo.

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

Video motivational para apreender FPGA, VHDL Microsoft's Bing* Intelligent Search with Intel® FPGAs |

Unidade 3 - Tipos de Dados e Operadores em VHDL

- 11 AULAS

| Unidade 3 - Tipos de Dados e Operadores em VHDL | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

-- Isso eh uma linha de comentario y <= a * b ; --o sinal y recebe o resultado da multiplicacao a x b

caracter: 'A' 'x' '#' (com aspas simples)

string: "IFSC" "teste" "teste123"

elemento ("bit") único: '0' '1' 'Z' (entre aspas simples)

vetor de elementos ("bits"): "0110" "101001Z" (entre aspas duplas)

vetor de 1 elemento ("bit"): "0" "1" (entre aspas duplas)

inteiros: 5 1101 1102 (sem aspas)

0 -> '0' 7 (em base 2) -> "0111" ou b"0111" ou B"0111" 1023 (em base 2) -> "001111111111" ou b"1111111111" ou B"1111111111"

44 (em base 8) -> 5*8^1 + 4*8^0 -> O"54" ou o"54" 1023 (em base 8)-> 1*8^3 + 7*8^2 + 7*8^1 + 7*8^0 -> o"1777" 8#1777#

1023 (em base 16) -> 3*16^2 + 15*16^1 + 15*16^0 = X"3FF" ou x"3FF" 16#3FF#

1023 -> 1023 ou 1_023 1000 -> 1000 ou 1_000 ou 1E3

85 (em base 5) -> (3*5^2 + 2*5^1 + 0*5^0) -> 5#320# 1539 (em base 3) -> (2*3^2+0*3^1+1*3^0)*3^4 -> 3#201#E4

constant <constant_name> : <type> := <constant_value>;

A constant pode ser declarado na parte declarativa da ENTITY, ARCHITECTURE, PACKAGE, PACKAGE_BODY, BLOCK, GENERATE, PROCESS, FUNCTION e PROCEDURE. -- Signal sem valor default

-- Para atribuir um valor a um signal use "<=" como operador.

signal <name> : <type>;

-- Signal com valor default

signal <name> : <type> := <default_value>;

-- Declarações comuns de signals

signal <name> : std_logic;

signal <name> : std_logic_vector(<msb_index> downto <lsb_index>);

signal <name> : integer;

signal <name> : integer range <low> to <high>;

O signal pode ser declarado na parte declarativa da ENTITY, ARCHITECTURE, PACKAGE, BLOCK, GENERATE. Os sinais não podem ser declarados no código sequencial (PROCESS, FUNCTION e PROCEDURE), mas podem ser usados. -- Variables devem ser declarada em process ou subprogramas.

-- Para atribuir um valor a um variable use ":=" como operador.

-- Variable sem valor default.

variable <name> : <type>;

-- Variable com valor default.

variable <name> : <type> := <default_value>;

-- Declarações comuns de variables

variable <name> : std_logic;

variable <name> : std_logic_vector(<msb_index> downto <lsb_index>);

variable <name> : integer;

variable <name> : integer range <low> to <high>;

O variable (variável) só pode ser declarada e usada dentro do escopo no código sequencial (PROCESS, FUNCTION e PROCEDURE).

Exemplos de declaração de CONSTANT, SIGNAL, VARIABLE, inicializando o valor usando o agregados CONSTANT a: BIT_VECTOR(5 DOWNTO 0) := (OTHERS => '0'); -- "000000"

CONSTANT b: BIT_VECTOR(7 DOWNTO 0) := (7 => '0', OTHERS => '1'); -- "01111111"

CONSTANT c: BIT_VECTOR(7 DOWNTO 0) := (7 => '0', 6 DOWNTO 0 => '1'); -- "01111111"

CONSTANT d: BIT_VECTOR(7 DOWNTO 0) := "01111111";

SIGNAL e: STD_LOGIC_VECTOR(7 DOWNTO 0); -- Not initialized

SIGNAL f: STD_LOGIC_VECTOR(1 TO 8) := (2|3|8 => '1', 4 => 'Z', OTHERS => '0' ); -- "011Z0001"

VARIABLE g: BIT_VECTOR(1 TO 16); -- Not initialized

VARIABLE h: BIT_VECTOR(1 TO 16) := (1 TO 8 => '1', OTHERS => '0'); -- "1111111100000000"

A biblioteca standard.vhd define os tipos BIT, BIT_VECTOR, BOOLEAN, INTEGER, NATURAL, POSITIVE, CHARACTER, STRING. package standard is

type boolean is (false,true);

type bit is ('0', '1');

type severity_level is (note, warning, error, failure);

type integer is range -2147483647 to 2147483647;

type real is range -1.0E308 to 1.0E308;

type time is range -2147483648 to 2147483647

units

fs;

ps = 1000 fs;

ns = 1000 ps;

us = 1000 ns;

ms = 1000 us;

sec = 1000 ms;

min = 60 sec;

hr = 60 min;

end units;

subtype natural is integer range 0 to integer'high;

subtype positive is integer range 1 to integer'high;

type string is array (positive range <>) of character;

type bit_vector is array (natural range <>) of bit;

A biblioteca Std logic 1164.vhd define os tipos STD_(U)LOGIG, STD_(U)LOGIG_VECTOR. PACKAGE std_logic_1164 IS

TYPE std_ulogic IS ( 'U', -- Uninitialized

'X', -- Forcing Unknown

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak Unknown

'L', -- Weak 0

'H', -- Weak 1

'-' -- Don't care

);

TYPE std_ulogic_vector IS ARRAY ( NATURAL RANGE <> ) OF std_ulogic;

SUBTYPE std_logic IS resolved std_ulogic;

TYPE std_logic_vector IS ARRAY ( NATURAL RANGE <>) OF std_logic;

A biblioteca Std logic 1164.vhd ainda define algumas funções importantes como a rising_edge que determina se um sinal está na borda de subida (usado em sinais de clock). -------------------------------------------------------------------

-- conversion functions

-------------------------------------------------------------------

FUNCTION To_bit ( s : std_ulogic; xmap : BIT := '0') RETURN BIT;

FUNCTION To_bitvector ( s : std_logic_vector ; xmap : BIT := '0') RETURN BIT_VECTOR;

FUNCTION To_StdULogic ( b : BIT ) RETURN std_ulogic;

FUNCTION To_StdLogicVector ( b : BIT_VECTOR ) RETURN std_logic_vector;

-------------------------------------------------------------------

-- edge detection

-------------------------------------------------------------------

FUNCTION rising_edge (SIGNAL s : std_ulogic) RETURN BOOLEAN;

FUNCTION falling_edge (SIGNAL s : std_ulogic) RETURN BOOLEAN;

-------------------------------------------------------------------

-- edge detection

-------------------------------------------------------------------

FUNCTION rising_edge (SIGNAL s : std_ulogic) RETURN BOOLEAN IS

-- altera built_in builtin_rising_edge

BEGIN

RETURN (s'EVENT AND (To_X01(s) = '1') AND

(To_X01(s'LAST_VALUE) = '0'));

END;

A biblioteca Numeric std.vhd define os tipos UNSIGNED e SIGNED. package NUMERIC_STD is

type UNSIGNED is array (NATURAL range <>) of STD_LOGIC;

type SIGNED is array (NATURAL range <>) of STD_LOGIC;

A biblioteca Numeric std.vhd ainda define os operadores (abs, "+", "-", "*", "\", rem, mod, sll, slr, ror, rol), comparações ("=", '/=', ">", ">=", "<", "<=") e operadores lógicos (not, and, nand, or, nor, xor, xnor) para os tipos SIGNED e UNSIGNED. Além disso também define algumas funções muito utilizadas como: --============================================================================

-- RESIZE Functions

--============================================================================

function RESIZE (ARG: SIGNED; NEW_SIZE: NATURAL) return SIGNED;

function RESIZE (ARG: UNSIGNED; NEW_SIZE: NATURAL) return UNSIGNED;

--============================================================================

-- Conversion Functions

--============================================================================

function TO_INTEGER (ARG: UNSIGNED) return NATURAL;

function TO_INTEGER (ARG: SIGNED) return INTEGER;

function TO_UNSIGNED (ARG, SIZE: NATURAL) return UNSIGNED;

function TO_SIGNED (ARG: INTEGER; SIZE: NATURAL) return SIGNED;

Figura 3.1 - Simulação do indicador de vagas

library ieee;

use ieee.std_logic_1164.all;

entity tri_state is

generic (N: NATURAL := 1);

port

(

input : in std_logic_vector(N-1 downto 0);

ena : in std_logic;

output : out std_logic_vector(N-1 downto 0);

);

end entity;

architecture tri_state of tri_state is

begin

output <= input when ena = '1' else "Z";

end architecture;

library ieee;

use ieee.std_logic_1164.all;

entity Ex3_2 is

port

(

x : in STD_LOGIC_VECTOR(1 downto 0);

y : out STD_LOGIC_VECTOR(1 downto 0)

);

end entity;

architecture un3 of Ex3_2 is

begin

y <= "00" when x = "00" else

"01" when x = "10" else

"10" when x = "01" else

"--";

end architecture;

x = "1----" -- não funciona em VHDL

std_match(x, "1----") -- funciona em VHDL

Ler e guardar a página sobre Aritmética com vetores em VDHL

São suportados nos tipos de dados: BIT, BIT_VECTOR, BOOLEAN, STD_(U)LOGIC, STD_(U)LOGIC_VECTOR, SIGNED e UNSIGNED. Com VHDL 2008 também suportado para BOOLEAN_VECTOR, UFIXED, SFIXED e FLOAT. NOT AND NAND OR NOR XOR XNOR Apenas o operador NOT tem precedência sobre os demais y <= a AND b XOR c -- é equivalente a (a AND b) XOR c y <= NOT a AND b -- é equivalente a (NOT a) AND b. y <= a NAND b -- é equivalente a NOT (a AND b)

São suportados nos tipos de dados: INTEGER, NATURAL, POSITIVE, SIGNED e UNSIGNED. Com VHDL 2008 também suportado para UFIXED, SFIXED e FLOAT. soma (+) subtração (-) multiplicação (*) divisão (/) exponenciação (**) valor absoluto (ABS) resto (REM remainder) módulo (MOD) Não há restrições para síntese de circuitos com os operadores, exceto para "**" que necessita de expoente estático (a**5) ou base estática (5**a). O operador x/y é a divisão inteira com sinal.

O operador ABS x retorna o valor absoluto de x.

O operador x REM y retorna o resto de x/y com sinal de x. Esse operador realiza a operação x REM y = x - (x/y)*y.

O operador x MOD y retorna o resto de x/y com sinal de y. Esse operador realiza a operação x MOD y = x REM y + a*y, onde a = 1 quando o sinal de x é diferente do sinal de y, e a = 0 se os sinais de x e y são iguais.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity bin2bcd is

port

(

C : in std_logic_vector (6 downto 0);

sd, su : out std_logic_vector (3 downto 0)

);

end entity;

architecture ifsc_v1 of bin2bcd is

signal C_uns : unsigned (6 downto 0);

signal sd_uns, su_uns : unsigned (6 downto 0);

begin

sd <= std_logic_vector(resize(sd_uns, 4));

su <= std_logic_vector(resize(su_uns, 4));

sd_uns <= C_uns/10;

su_uns <= C_uns rem 10;

c_uns <= unsigned(c);

end architecture;

architecture ifsc_v2 of bin2bcd is

begin

-- Implemente o circuito usando a definição de REM que é: x REM y = x - (x/y)*y

end architecture;

configuration bin2bcd_cfg of bin2bcd is

--A instrução '''configuration''' associa a '''entity''' bin2bcd a '''architecture'''.

for ifsc_v1 end for;

--Para associar a '''entity''' bin2bcd a '''architecture''' ifsc_v2 comente a linha acima e descomente a linha abaixo.

-- for ifsc_v2 end for;

end configuration;

Figura 3.2 - RTL do conversor de Binário para BCD com 2 digitos  Figura 3.3 - Simulação do conversor de Binário para BCD com 2 digitos

Atributos em VHDL.

Em VHDL existem diversos atributos de sintese que controlam a forma como o processo de "Analysis & Synthesis" é realizado pelo Quartus II. Uma listagem completa pode ser encontrada em:

type fruit is (apple, orange, pear, mango);

attribute enum_encoding : string;

attribute enum_encoding of fruit : type is "11 01 10 00";

entity foo is

port (sel : in std_logic;

data : in std_logic_vector(3 downto 0);

o : out std_logic);

end foo;

architecture rtl of foo is

attribute chip_pin : string;

attribute chip_pin of sel : signal is "C4";

attribute chip_pin of data : signal is "D1, D2, D3, D4";

begin

-- Specify additional code

end architecture;

O uso desse atributo sobrepõe a atribuição dos pinos através da IDE do Quartus II, e por isso não é recomendável. O atributo de síntese chip_pin pode ser usado apenas em portas da entidade "top-level" do projeto. .

O atributo de síntese KEEP, sinaliza ao processo de "Analysis & Synthesis" para manter intacto um determinado signal ou componente. signal a,b,c : std_logic;

attribute keep: boolean;

attribute keep of a,b,c: signal is true;

signal a,b,c : std_logic;

attribute preserve: boolean;

attribute preserve of a,b,c: signal is true;

signal reg1: std_logic;

attribute noprune: boolean;

attribute noprune of reg1: signal is true;

signal a: bit_vector(7 downto 0) := "01100101"; y <= a SLL 2; -- y <= "10010100" (y <= a(5 downto 0) & "00";) y <= a SLA 2; -- y <= "10010111" (y <= a(5 downto 0) & a(0) & a(0);) y <= a ROR 2; -- y <= "01011001" (y <= a(1 downto 0) & a(7 downto 2);)

Igualdade (=) Diferença (/=) Menor que (<) Menor ou igual que (<=) Maior que (>) Maior ou igual que (>=)

Igualdade (?=) Diferença (?/=) Menor que (?<) Menor ou igual que (?<=) Maior que (?>) Maior ou igual que (?>=)

Para cada atributo existe uma descrição completa como mostrado a seguir. P'LEFT Kind: Value. Prefix: Any prefix P that is appropriate for an object with a scalar type or subtype T, or an alias thereof, or that denotes any scalar type or subtype T. Result type: Same type as T. Result: The left bound of T. A seguir estão listados alguns dos atributos mais utilizados.

P'LEFT - The left bound of T. P'RIGHT - The right bound of T. P'HIGH - The upper bound of T. P'LOW - The lower bound of T. P'ASCENDING - It is TRUE if T is defined with an ascending range; FALSE otherwise. P'LENGTH - maximum(0, T’POS(T’HIGH) – T’POS(T’LOW) + 1) P'RANGE - The range T'LEFT to T'RIGHT if the range of T is ascending, or the range T'LEFT downto T'RIGHT if the range of T is descending P'REVERSE_RANGE - The range T'RIGHT downto T'LEFT if the range of T is ascending, or the range T'RIGHT to T'LEFT if the range of T is descending T'POS(X) - The position number of the value of the parameter T'VAL(X) - The value whose position number is the universal_integer value corresponding to X.

A'LEFT [(N)] - Left bound of the Nth index range of A A'RIGHT [(N)] - Right bound of the Nth index range of A A'HIGH [(N)] - Upper bound of the Nth index range of A A'LOW [(N)] - Lower bound of the Nth index range of A. A'RANGE [(N)] - The range A'LEFT(N) to A'RIGHT(N) if the Nth index range of A is ascending, or the range A'LEFT(N) downto A'RIGHT(N) if the Nth index range of A is descending A'REVERSE_RANGE [(N)] - The range A'RIGHT(N) downto A'LEFT(N) if the Nth index range of A is ascending, or the range A'RIGHT(N) to A'LEFT(N) if the Nth index range of A is descending. A'LENGTH [(N)] - Number of values in the Nth index range A'ASCENDING [(N)] - TRUE if the Nth index range of A is defined with an ascending range; FALSE otherwise.

S'EVENT - A value that indicates whether an event has just occurred on signal S. S'LAST_VALUE - For a signal S, if an event has occurred on S in any simulation cycle, S'LAST_VALUE returns the value of S prior to the update of S in the last simulation cycle in which an event occurred; otherwise, S'LAST_VALUE returns the current value of S.

E'SIMPLE_NAME - The simple name, character literal, or operator symbol of the named entity

attribute attribute_name: attribute_type;

attribute attribute_name of entity_tag [signature]: entity_class is value;

A retirada de fatias (SLICES) dos ARRAYs só pode ser feita se o array foi definido com um vetor de vetores (1Dx1D ou 1Dx1Dx1D). Ainda assim é necessário respeitar a ordem dos índices do VETOR. No caso abaixo é ascendente (TO), e dentro dos limites (1 to 4). type a1Dx1D_bit is array (1 to 3) of BIT_VECTOR(1 to 4);

type a2D_bits is array (1 to 3, 1 to 4) of bit; type a3D_bits is array (1 to 3, 1 to 4, 1 to 2) of bit;

slice3 <= table(row, 1) & table(row, 2) & & table(row, 3) & & table(row, 4);

slice4 <= table(1, column) & table(2, column) & table(3, column);

gen1 : for j in 1 to 4 generate

slice3(j) <= table(row, j);

end generate;

gen2 : for i in 1 to 3 generate

slice4(i) <= table(i, column);

end generate;

-----Package:------------

-- File: my_pkg.vhd

-------------------------

package my_data_types is

type a1Dx1D_bit_vector is array (0 to 3) of BIT_VECTOR(7 downto 0);

end my_data_types;

-----Main code: --------

-- File: my_pkg.vhd

-------------------------

use work.my_data_types.all;

entity mux1Dx1D is

port (

x : in a1Dx1D_bit_vector;

sel : integer range 0 to 3;

y : out BIT_VECTOR(7 downto 0)

);

end entity;

architecture pedroni of mux1Dx1D is

begin

y <= x(sel);

end architecture;

Ver pag. 60 a 73 de [2]

Enquanto que em um ARRAY todos os elementos devem ser obrigatoriamente do mesmo tipo, em um RECORD (Registro) os elementos podem ser de tipos diferentes. type memory_access is record

address : integer range 0 to 255;

block : integer range 0 to 3;

data : BIT_VECTOR(15 downto 0);

end record;

--Escrita no RECORD

constant endereco : memory_access := (34, 3, "010011110101011");

--Acesso ao RECORD

signal address_lido : integer range 0 to 255;

signal block_lido : integer range 0 to 3;

signal data_lido : bit_vector(15 downto 0);

address_lido <= endereco.address;

block_lido <= endereco.block;

data_lido <= endereco.data;

entity record_example is

port (

flag : out BIT_VECTOR(1 to 4);