DLP1-EngTel (Plano de Ensino)

Ir para navegação

Ir para pesquisar

|

MINISTÉRIO DA EDUCAÇÃO |

Plano de Ensino de 2014-2 - atual

- Dados gerais

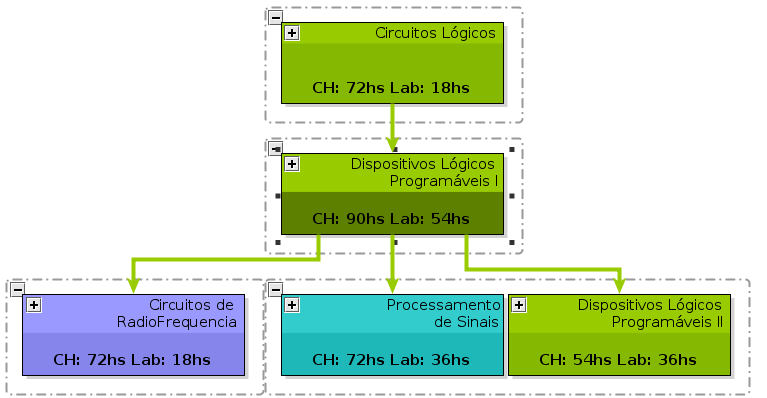

- COMPONENTE CURRICULAR: DLP1 - DISPOSITIVOS LÓGICOS PROGRAMÁVEIS I

- CARGA HORÁRIA: 5 HORAS/SEMANA 90 HORAS. TEÓRICA = 36 HORAS. LABORATÓRIO = 54 HORAS

- PRÉ REQUISITOS: CIL

- DISCIPLINAS SUCESSORAS: CRF, PSD, DLP2

- MÓDULO ESPECIALIZANTE

- Objetivos

Ao final do curso os alunos deverão ser capazes de

- conhecer os tipos de dispositivos lógicos programáveis e utiliza-los para a implementação em VHDL de sistemas simples.

- conhecer e utilizar a linguagem de descrição de hardware VHDL, incluindo: tipos de dados, libraries, conversão de tipos, operadores, atributos, afirmações para código concorrente e sequencial.

- conhecer e utilizar o projeto hierárquico em VHDL, incluindo funções, procedures, componentes, packages.

- Conhecer e utilizar Maquinas de Estado Finita para projeto de sistemas digitais sequenciais.

- Utilizar ferramentas de simulação funcional e temporal para verificar o funcionamento do hardware, incluindo QSIM e Modelsim, criação de testbenches.

- Ementa

- Arquitetura, síntese de projetos, linguagem de descrição de hardware, projetos de circuitos combinacionais e sequenciais utilizando HDL, conceito e projeto de circuitos de máquinas de estado utilizando HDL, simulação e análise temporal de circuitos digitais projetados em HDL

- Conteúdo Programático

- Dispositivos lógicos programáveis. (8h)

- Bases da linguagem VHDL. (8h)

- Tipos de dados, libraries, conversão de tipos, operadores, atributos. (22h)

- Código VHDL concorrente e sequencial. (22h)

- Projeto hierárquico. (6h)

- Simulação e Testbench (6h)

- Maquina de estado finita (FSM). (8h)

- Projeto Final de circuitos lógicos. (6h)

- Avaliações. (4h)

- Estratégias de ensino utilizadas

- Aulas expositivas usando wiki e livro texto para apresentar conceitos;

- Aulas de laboratório;

- Desenvolvimento de projetos para trabalhar de forma articulada os conceitos da disciplina.

- Critérios e instrumentos de avaliação

- 2 avaliações escritas, diversos projetos ao longo do semestre, e um projeto final.

- Atividades Complementares

- Projetos de circuitos usando o ambiente Quartus.

- Simulação de circuitos com QSIM e Modelsim.

- Programação de dispositivos FPGA

- Bibliografia Básica

- PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. ISBN 9788535234657

- TOCCI, Ronald J.; WIDMER, Neal S.; MOSS, Gregory L Sistemas digitais: Princípios e Aplicações; 11ª ed. [S.l]:Pearson, 2011. 840p. ISBN 9788576059226

- James W. Bignell e Robert Donovan Eletrônica Digital; 5ª ed. São Paulo:Cengage Learning, 2010. 672p. ISBN 9788522107452

- Bibliografia Complementar

- Perry, Douglas VHDL : Programming By Example; 4ª ed. [S.l]:McGraw-Hill Professional, 2002. 476p. ISBN 9780071400701

- Pong P. Chu RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability; 1ª ed. [S.l]:Wiley-IEEE Press, 2006. 694p. ISBN 9780471720928

- Pedroni, Volnei A. Digital electronics and design with VHDL; 1ª ed. Burlington:Elsevier, 2008. 693p. ISBN 9780123742704

- ASHENDEN, Peter J. The Designer's Guide to VHDL; 3ª ed. [S.l]:Morgan Kaufmann, 2008. p. ISBN 9780120887859

- PEDRONI, Volnei A. Circuit Design with VHDL; ed. [S.l]:MIT, 2004. p. ISBN 9780262162241

- Bibliografia Adicional

- PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335

ANEXOS