Mudanças entre as edições de "DLP1-EngTel (Plano de Ensino)"

Ir para navegação

Ir para pesquisar

| (28 revisões intermediárias por 4 usuários não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

{{Cab1-IF-SC-Engtelecom}} | {{Cab1-IF-SC-Engtelecom}} | ||

<BIG><center> | <BIG><center> | ||

| − | '''Plano de Ensino de | + | '''Plano de Ensino de 2020-1''' |

</center></BIG> | </center></BIG> | ||

| Linha 13: | Linha 13: | ||

;Objetivos | ;Objetivos | ||

| + | Ao concluir a disciplina os alunos deverão ser capazes de | ||

| + | * Conhecer os tipos de dispositivos lógicos programáveis e utiliza-los para a implementação em VHDL de sistemas simples. | ||

| + | * Conhecer e utilizar a linguagem de descrição de hardware VHDL para código concorrente e sequencial. | ||

| + | * Conhecer e utilizar o projeto hierárquico em VHDL. | ||

| + | * Conhecer e projetar maquinas de estado simples. | ||

| + | * Utilizar ferramentas de simulação funcional e temporal para verificar o funcionamento do hardware, incluindo QSIM e Modelsim | ||

| + | * Criar e utilizar testbenches do tipo gráfico, scritpt .do e VHDL. | ||

;Ementa | ;Ementa | ||

:Arquitetura, síntese de projetos, linguagem de descrição de hardware, projetos de circuitos combinacionais e sequenciais utilizando HDL, conceito e projeto de circuitos de máquinas de estado utilizando HDL, simulação e análise temporal de circuitos digitais projetados em HDL | :Arquitetura, síntese de projetos, linguagem de descrição de hardware, projetos de circuitos combinacionais e sequenciais utilizando HDL, conceito e projeto de circuitos de máquinas de estado utilizando HDL, simulação e análise temporal de circuitos digitais projetados em HDL | ||

| − | ;Conteúdo Programático | + | ;Conteúdo Programático |

| + | :1. Introdução a disciplina. | ||

| + | :2. Introdução ao VHDL e Dispositivos lógicos programáveis e o ambiente EDA Quartus. | ||

| + | :3. Definições básicas do VHDL: Tipos de dados, operadores, atributos. | ||

| + | :4. Código VHDL concorrente: uso de WHEN, SELECT, GENERATE; circuitos combinacionais; circuitos aritméticos. | ||

| + | :5. Código VHDL sequencial: uso de PROCESS, IF, WAIT, LOOP, CASE; | ||

| + | :6. Projeto hierárquico: uso de PACKAGE, COMPONENT, CONFIGURATION, FUNCION, PROCEDURE, ASSERT. | ||

| + | :7. Simulação e e uso de testbench | ||

| + | :8. Projeto de maquinas de estado | ||

| + | :9. Projeto Final: especificação, implementação em VHDL, simulação, teste em hardware, documentação, integração dos subprojetos, apresentação oral. | ||

| + | :10. Avaliações. | ||

;Estratégias de ensino utilizadas | ;Estratégias de ensino utilizadas | ||

| + | *Aulas expositivas usando wiki e livro texto para apresentar conceitos, exemplos; | ||

| + | *Aulas de laboratório utilizando softwares de síntese e simulação (Quartus, QSIM, Modelsim) ; | ||

| + | * Desenvolvimento de projetos para trabalhar de forma articulada os conceitos da disciplina. | ||

| + | * Durante o período de Pandemia do Corona-virus as aulas passaram a ser realizadas através de ANPs com encontros sincronos no horário previsto para a disciplina, usando o Google Meet com gravação das aulas. | ||

| + | * Neste período de Pandemia do Corona-virus para as aulas práticas, os alunos inicialmente utilizaram o IFSC-Cloud QUartus, mas depois de Agosto passaram a usar a VM Quartus disponibilizada para este fim. | ||

| + | *Após o dia 30 de agosto os alunos passaram a trabalhar nos projetos finais, e o atendimento as dúvidas eram também feitas de forma individual ou equipes usando o Google Meet e pelo workspace da disciplina no Slack. | ||

;Critérios e instrumentos de avaliação | ;Critérios e instrumentos de avaliação | ||

| + | * O resultado final (RF) do aluno na disciplina será calculado realizando a média ponderadas dos valores. | ||

| + | :<math> RF = \frac{A1 * PA1 + A2 * PA2 + AE * PAE + PFr * PPFr + PFp * PPFp } {PA1 + PA2 + PAE + PPFr + PPFp}</math>, | ||

| + | :onde os pesos de ponderação são: <math> \begin{matrix} PA1 = 29 ; PA2 = 29 ; PAE = 6 ; PPFr = 18; PPFp = 18 \end{matrix} </math> | ||

| + | * cada avaliação e também o resultado final (RF) será atribuído um valor entre 0 e 10. | ||

| + | * valores não inteiros obtidos na média do RF serão arredondados: | ||

| + | ::a) para baixo se a parte fracionária for menor que 0,4. | ||

| + | ::b) para cima se a parte fracionária for maior que 0,6. | ||

| + | ::c) de acordo com a avaliação subjetiva e frequência do aluno se a parte fracionária estiver entre 0,4 e 0,6. | ||

| + | * O resultado final mínimo para aprovação é 6 (seis), devendo o aluno ter os conceitos superiores ou iguais a 4 em nas avaliações A1, A2 e PF. | ||

| + | * Ao aluno que tiver frequência inferior a 75% na disciplina será atribuído RF = 0; | ||

| + | |||

| + | * A1 e A2 são 2 avaliações escritas/laboratório. Para estas avaliações haverá no final do semestre a possibilidade de realizar uma recuperação R12 cobrindo todas as unidades, para os aluno que estiverem com valores inferiores a 6 nas avaliações A1 ou A2, cujo conceito máximo nessas avaliações após a recuperação será de 6. | ||

| + | * AE será constituída pelo conjunto de atividades Atividades Extraclasse AE1 a AEN realizada ao longo do semestre. Para cada uma dessas atividades o aluno/equipe que não entregá-la no prazo preestabelecido, como forma de recuperação será admitido a entrega da atividade com atraso, sendo descontado 0,3 pontos por dia de atraso. Após 20 dias de atraso não será atribuído nenhum conceito a esta atividade; | ||

| + | * PF será constituída pela avaliação no projeto final, no qual serão analisados os quesitos: | ||

| + | :1 - Implementação do projeto, atendimento as especificações e requisitos do sistema. (PPFr) | ||

| + | :2 - Documentação do projeto e especificações iniciais. (PPFr) | ||

| + | <!-- | ||

| + | :3 - Avaliação do aluno durante o desenvolvimento do projeto. | ||

| + | :4 - Apresentação do projeto para a turma (15 minutos por equipe) | ||

| + | --> | ||

| + | ;Atividades Complementares | ||

| + | *Projetos de circuitos usando o ambiente Quartus. | ||

| + | *Simulação de circuitos com QSIM e Modelsim. | ||

| + | *Programação de dispositivos FPGA | ||

| + | * Durante o semestre os alunos desenvolverão de forma individual ou em equipes algumas atividades extra-classe (AEs), que consistem de projetos ou exercícios para um melhor compreensão e aplicação dos temas da ementa. | ||

| + | *Para os exercícios práticos extra-classe os alunos dispõe da IFSC-CLOUD Quartus e também uma VM Quartus. | ||

| + | *Como laboratório remoto foi disponibilizado um kit que os alunos podem acessar conforme descrito em [[Criação de um acesso remoto ao kit MERCURIO IV]]. | ||

| + | |||

| + | =Bibliografia do PPCv2015-2= | ||

| + | |||

| + | ;Bibliografia Básica | ||

| + | # James W. Bignell e Robert Donovan '''Eletrônica Digital'''; 5ª ed. São Paulo:Cengage Learning, 2010. 672p. ISBN 9788522107452. Qtdade Na Biblioteca para a Disciplina:6. Número de chamada: 621.381 B593e | ||

| + | # PEDRONI, Volnei A '''Eletrônica Digital Moderna e VHDL: Princípios Digitais, Eletrônica Digital, Projeto Digital, Microeletrônica e VHDL'''; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. ISBN 9788535234657. Qtdade Na Biblioteca para a Disciplina:8. Número de chamada: 621.392 P372e | ||

| + | # TOCCI, Ronald J.; WIDMER, Neal S.; MOSS, Gregory L. '''Sistemas digitais: Princípios e Aplicações'''; 11ª ed. [S.l]:Pearson, 2011. 840p. ISBN 9788576059226. Qtdade Na Biblioteca para a Disciplina:4. Número de chamada: 621.381 T631s | ||

| + | |||

| + | ;Bibliografia Complementar | ||

| + | # ASHENDEN, Peter J. '''The Designer's Guide to VHDL - Vol3'''; 3ª ed. [S.l]:Morgan Kaufmann, 2008. p. ISBN 9780120887859. Qtdade Na Biblioteca para a Disciplina:1. Número de chamada: 621.392 A824d | ||

| + | # COSTA, César da. '''Projetos de circuitos digitais com FPGA'''; 35ª ed. São Paulo:Érica, 2009. 206p. ISBN 9788536502397. Qtdade Na Biblioteca para a Disciplina:2. Número de chamada: 621.3815 C837p | ||

| + | # IDOETA, Ivan Valeije; CAPUANO, Francisco Gabriel '''Elementos de eletrônica digital'''; 35ª ed. São Paulo:Érica, 2003. 524p. ISBN 8571940193. Qtdade Na Biblioteca para a Disciplina:2. Número de chamada: 621. 381 I22e | ||

| + | # PEDRONI, Volnei A '''Digital electronics and design with VHDL'''; 1ª ed. Burlington:Elsevier, 2008. 693p. ISBN 9780123742704. Qtdade Na Biblioteca para a Disciplina:2. Número de chamada: 621.392 P372d | ||

| + | # Perry, Douglas '''VHDL : Programming By Example'''; 4ª ed. [S.l]:McGraw-Hill Professional, 2002. 476p. ISBN 9780071400701. Qtdade Na Biblioteca para a Disciplina:2. Número de chamada: 621.392 P462v | ||

| + | |||

| + | <!-- | ||

| + | =Bibliografia prevista PPCv2016-1= | ||

| + | |||

| + | ;Bibliografia Básica | ||

| + | |||

| + | # James W. Bignell e Robert Donovan '''Eletrônica Digital'''; 5ª ed. São Paulo:Cengage Learning, 2010. 672p. ISBN 9788522107452. Qtdade Na Biblioteca para a Disciplina:6 | ||

| + | # PEDRONI, Volnei A '''Eletrônica Digital Moderna e VHDL: Princípios Digitais, Eletrônica Digital, Projeto Digital, Microeletrônica e VHDL'''; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. ISBN 9788535234657. Qtdade Na Biblioteca para a Disciplina:8 | ||

| + | # TOCCI, Ronald J.; WIDMER, Neal S.; MOSS, Gregory L. '''Sistemas digitais: Princípios e Aplicações'''; 11ª ed. [S.l]:Pearson, 2011. 840p. ISBN 9788576059226. Qtdade Na Biblioteca para a Disciplina:4 | ||

| + | |||

| + | ;Bibliografia Complementar | ||

| + | |||

| + | # PEDRONI, Volnei A '''Digital electronics and design with VHDL'''; 1ª ed. Burlington:Elsevier, 2008. 693p. ISBN 9780123742704. Qtdade Na Biblioteca para a Disciplina:2 | ||

| + | # IDOETA, Ivan Valeije; CAPUANO, Francisco Gabriel '''Elementos de eletrônica digital'''; 35ª ed. São Paulo:Érica, 2003. 524p. ISBN 8571940193. Qtdade Na Biblioteca para a Disciplina:2 | ||

| + | # Perry, Douglas '''VHDL : Programming By Example'''; 4ª ed. [S.l]:McGraw-Hill Professional, 2002. 476p. ISBN 9780071400701. Qtdade Na Biblioteca para a Disciplina:2 | ||

| + | # COSTA, César da. '''Projetando controladores digitais com FPGA'''; ed. São Paulo:Novatec, 2006. 206p. ISBN 8575220888. Qtdade Na Biblioteca para a Disciplina:2 | ||

| + | # ASHENDEN, Peter J. '''Digital Design An Embedded Systems Aproach Using Verilog'''; ed. [S.l]:Elsevier, 2008. p. ISBN 978012369284. Qtdade Na Biblioteca para a Disciplina:2 | ||

| + | # PEDRONI, Volnei A '''Circuit Design and Simulation with VHDL'''; 2ª ed. Massachusetts-EUA:MIT, 2010. p. ISBN 9780262014335. Qtdade Na Biblioteca para a Disciplina:2 | ||

| + | |||

| + | Comentário: Observar diferenças em COSTA e ASHENDEN | ||

| + | --> | ||

| + | |||

| + | <!-- | ||

| + | =Bibliografia Inicialmente Sugerida= | ||

;Bibliografia Básica | ;Bibliografia Básica | ||

| Linha 32: | Linha 120: | ||

# Pong P. Chu '''RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability'''; 1ª ed. [S.l]:Wiley-IEEE Press, 2006. 694p. ISBN 9780471720928 | # Pong P. Chu '''RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability'''; 1ª ed. [S.l]:Wiley-IEEE Press, 2006. 694p. ISBN 9780471720928 | ||

# Pedroni, Volnei A. '''Digital electronics and design with VHDL'''; 1ª ed. Burlington:Elsevier, 2008. 693p. ISBN 9780123742704 | # Pedroni, Volnei A. '''Digital electronics and design with VHDL'''; 1ª ed. Burlington:Elsevier, 2008. 693p. ISBN 9780123742704 | ||

| − | # ASHENDEN, Peter J. '''The Designer's Guide to VHDL | + | # ASHENDEN, Peter J. '''[[The Designer's Guide to VHDL]]'''; 3ª ed. [S.l]:Morgan Kaufmann, 2008. p. ISBN 9780120887859 |

# PEDRONI, Volnei A. '''Circuit Design with VHDL'''; ed. [S.l]:MIT, 2004. p. ISBN 9780262162241 | # PEDRONI, Volnei A. '''Circuit Design with VHDL'''; ed. [S.l]:MIT, 2004. p. ISBN 9780262162241 | ||

| + | --> | ||

| + | ;Bibliografia Adicional | ||

| + | # PEDRONI, Volnei A. '''[[Circuit Design and Simulation with VHDL]]'''; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 | ||

| − | |||

| − | |||

| − | |||

| − | |||

{{ENGTELECO}} | {{ENGTELECO}} | ||

Edição das 11h02min de 20 de abril de 2021

|

MINISTÉRIO DA EDUCAÇÃO |

Plano de Ensino de 2020-1

- Dados gerais

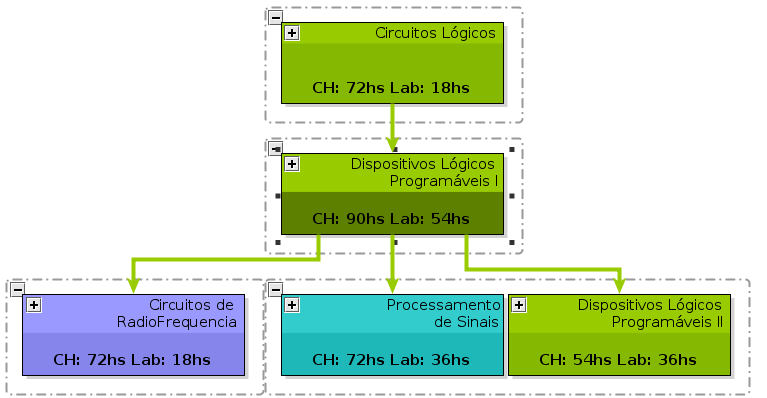

- COMPONENTE CURRICULAR: DLP1 - DISPOSITIVOS LÓGICOS PROGRAMÁVEIS I

- CARGA HORÁRIA: 5 HORAS/SEMANA 90 HORAS. TEÓRICA = 36 HORAS. LABORATÓRIO = 54 HORAS

- PRÉ REQUISITOS: CIL

- DISCIPLINAS SUCESSORAS: CRF, PSD, DLP2

- MÓDULO ESPECIALIZANTE

- Objetivos

Ao concluir a disciplina os alunos deverão ser capazes de

- Conhecer os tipos de dispositivos lógicos programáveis e utiliza-los para a implementação em VHDL de sistemas simples.

- Conhecer e utilizar a linguagem de descrição de hardware VHDL para código concorrente e sequencial.

- Conhecer e utilizar o projeto hierárquico em VHDL.

- Conhecer e projetar maquinas de estado simples.

- Utilizar ferramentas de simulação funcional e temporal para verificar o funcionamento do hardware, incluindo QSIM e Modelsim

- Criar e utilizar testbenches do tipo gráfico, scritpt .do e VHDL.

- Ementa

- Arquitetura, síntese de projetos, linguagem de descrição de hardware, projetos de circuitos combinacionais e sequenciais utilizando HDL, conceito e projeto de circuitos de máquinas de estado utilizando HDL, simulação e análise temporal de circuitos digitais projetados em HDL

- Conteúdo Programático

- 1. Introdução a disciplina.

- 2. Introdução ao VHDL e Dispositivos lógicos programáveis e o ambiente EDA Quartus.

- 3. Definições básicas do VHDL: Tipos de dados, operadores, atributos.

- 4. Código VHDL concorrente: uso de WHEN, SELECT, GENERATE; circuitos combinacionais; circuitos aritméticos.

- 5. Código VHDL sequencial: uso de PROCESS, IF, WAIT, LOOP, CASE;

- 6. Projeto hierárquico: uso de PACKAGE, COMPONENT, CONFIGURATION, FUNCION, PROCEDURE, ASSERT.

- 7. Simulação e e uso de testbench

- 8. Projeto de maquinas de estado

- 9. Projeto Final: especificação, implementação em VHDL, simulação, teste em hardware, documentação, integração dos subprojetos, apresentação oral.

- 10. Avaliações.

- Estratégias de ensino utilizadas

- Aulas expositivas usando wiki e livro texto para apresentar conceitos, exemplos;

- Aulas de laboratório utilizando softwares de síntese e simulação (Quartus, QSIM, Modelsim) ;

- Desenvolvimento de projetos para trabalhar de forma articulada os conceitos da disciplina.

- Durante o período de Pandemia do Corona-virus as aulas passaram a ser realizadas através de ANPs com encontros sincronos no horário previsto para a disciplina, usando o Google Meet com gravação das aulas.

- Neste período de Pandemia do Corona-virus para as aulas práticas, os alunos inicialmente utilizaram o IFSC-Cloud QUartus, mas depois de Agosto passaram a usar a VM Quartus disponibilizada para este fim.

- Após o dia 30 de agosto os alunos passaram a trabalhar nos projetos finais, e o atendimento as dúvidas eram também feitas de forma individual ou equipes usando o Google Meet e pelo workspace da disciplina no Slack.

- Critérios e instrumentos de avaliação

- O resultado final (RF) do aluno na disciplina será calculado realizando a média ponderadas dos valores.

- ,

- onde os pesos de ponderação são:

- cada avaliação e também o resultado final (RF) será atribuído um valor entre 0 e 10.

- valores não inteiros obtidos na média do RF serão arredondados:

- a) para baixo se a parte fracionária for menor que 0,4.

- b) para cima se a parte fracionária for maior que 0,6.

- c) de acordo com a avaliação subjetiva e frequência do aluno se a parte fracionária estiver entre 0,4 e 0,6.

- O resultado final mínimo para aprovação é 6 (seis), devendo o aluno ter os conceitos superiores ou iguais a 4 em nas avaliações A1, A2 e PF.

- Ao aluno que tiver frequência inferior a 75% na disciplina será atribuído RF = 0;

- A1 e A2 são 2 avaliações escritas/laboratório. Para estas avaliações haverá no final do semestre a possibilidade de realizar uma recuperação R12 cobrindo todas as unidades, para os aluno que estiverem com valores inferiores a 6 nas avaliações A1 ou A2, cujo conceito máximo nessas avaliações após a recuperação será de 6.

- AE será constituída pelo conjunto de atividades Atividades Extraclasse AE1 a AEN realizada ao longo do semestre. Para cada uma dessas atividades o aluno/equipe que não entregá-la no prazo preestabelecido, como forma de recuperação será admitido a entrega da atividade com atraso, sendo descontado 0,3 pontos por dia de atraso. Após 20 dias de atraso não será atribuído nenhum conceito a esta atividade;

- PF será constituída pela avaliação no projeto final, no qual serão analisados os quesitos:

- 1 - Implementação do projeto, atendimento as especificações e requisitos do sistema. (PPFr)

- 2 - Documentação do projeto e especificações iniciais. (PPFr)

- Atividades Complementares

- Projetos de circuitos usando o ambiente Quartus.

- Simulação de circuitos com QSIM e Modelsim.

- Programação de dispositivos FPGA

- Durante o semestre os alunos desenvolverão de forma individual ou em equipes algumas atividades extra-classe (AEs), que consistem de projetos ou exercícios para um melhor compreensão e aplicação dos temas da ementa.

- Para os exercícios práticos extra-classe os alunos dispõe da IFSC-CLOUD Quartus e também uma VM Quartus.

- Como laboratório remoto foi disponibilizado um kit que os alunos podem acessar conforme descrito em Criação de um acesso remoto ao kit MERCURIO IV.

Bibliografia do PPCv2015-2

- Bibliografia Básica

- James W. Bignell e Robert Donovan Eletrônica Digital; 5ª ed. São Paulo:Cengage Learning, 2010. 672p. ISBN 9788522107452. Qtdade Na Biblioteca para a Disciplina:6. Número de chamada: 621.381 B593e

- PEDRONI, Volnei A Eletrônica Digital Moderna e VHDL: Princípios Digitais, Eletrônica Digital, Projeto Digital, Microeletrônica e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. ISBN 9788535234657. Qtdade Na Biblioteca para a Disciplina:8. Número de chamada: 621.392 P372e

- TOCCI, Ronald J.; WIDMER, Neal S.; MOSS, Gregory L. Sistemas digitais: Princípios e Aplicações; 11ª ed. [S.l]:Pearson, 2011. 840p. ISBN 9788576059226. Qtdade Na Biblioteca para a Disciplina:4. Número de chamada: 621.381 T631s

- Bibliografia Complementar

- ASHENDEN, Peter J. The Designer's Guide to VHDL - Vol3; 3ª ed. [S.l]:Morgan Kaufmann, 2008. p. ISBN 9780120887859. Qtdade Na Biblioteca para a Disciplina:1. Número de chamada: 621.392 A824d

- COSTA, César da. Projetos de circuitos digitais com FPGA; 35ª ed. São Paulo:Érica, 2009. 206p. ISBN 9788536502397. Qtdade Na Biblioteca para a Disciplina:2. Número de chamada: 621.3815 C837p

- IDOETA, Ivan Valeije; CAPUANO, Francisco Gabriel Elementos de eletrônica digital; 35ª ed. São Paulo:Érica, 2003. 524p. ISBN 8571940193. Qtdade Na Biblioteca para a Disciplina:2. Número de chamada: 621. 381 I22e

- PEDRONI, Volnei A Digital electronics and design with VHDL; 1ª ed. Burlington:Elsevier, 2008. 693p. ISBN 9780123742704. Qtdade Na Biblioteca para a Disciplina:2. Número de chamada: 621.392 P372d

- Perry, Douglas VHDL : Programming By Example; 4ª ed. [S.l]:McGraw-Hill Professional, 2002. 476p. ISBN 9780071400701. Qtdade Na Biblioteca para a Disciplina:2. Número de chamada: 621.392 P462v

- Bibliografia Adicional

- PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335