DIG222802 2018 2 AULA08

Apresentação

Olá Estudante,

Nessa semana vamos falar dos multiplexadores e demultiplexadores. Na verdade, a implementação desses dispositivos, não deixa de ser uma aplicação dos codificadores e decodificadores, que vimos anteriormente, e que vai nos preparar para estudarmos as memórias mais adiante.

Lembre-se que a WiKi não deve ser utilizada como única fonte de estudos.

Bons Estudos!

Prof. Douglas A.

Objetivo

- Aprender sobre circuitos Multiplexadores.

- Compreender o funcionamento dos Demultiplexadores.

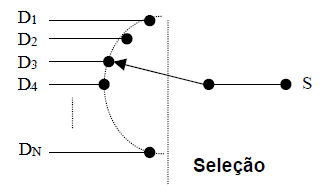

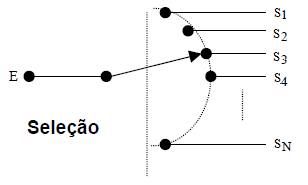

Multiplexadores

Os circuitos multiplexadores (MUX) possuem uma única saída a qual permite ligar as informações de uma de suas várias entradas, selecionadas por uma palavra binária de controle. Ou seja, a saída copia o estado da entrada selecionada. Um circuito elementar poderia ser comparado com uma chave de 1 polo por N (N:1) posições de entrada. A Figura 1 mostra um circuito seletor de N entradas por uma saída.

Figura 1 - Circuito seletor (N:1).

Se desejarmos ligar os dados da entrada 2 na saída, por exemplo, basta

selecionarmos a posição 2 na chave seletora. E assim por diante. Porém,

para se fazer isto é necessário que cada chave seletora enderece uma

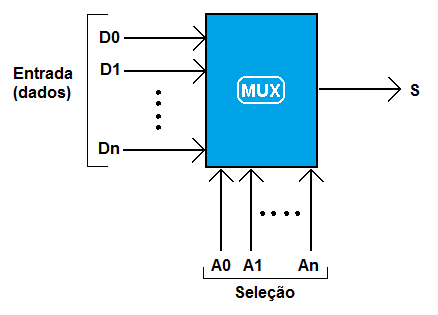

das saídas. A Figura 2 mostra o esquema completo de entradas, endereçamento

e saída de um multiplexador.

Figura 2 - Multiplexador (N:1).

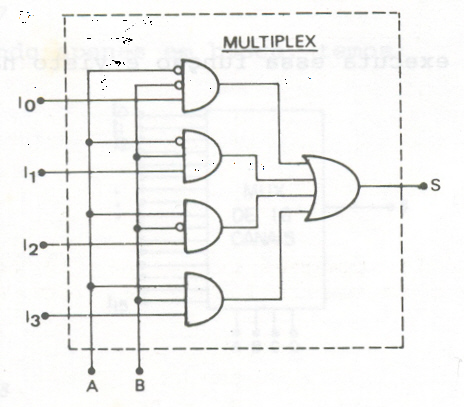

Com um circuito combinacional, podemos implementar facilmente esta tarefa de selecionar

uma das entradas. A Figura 3 mostra o exemplo de um circuito lógico que implementa um MUX de 4 entradas.

Figura 3 - Multiplexador de 4 entradas.

Percebe-se claramente neste circuito, que as combinações possíveis das chaves A e B (, onde N é número de bits de endereço) selecionam somente uma das entradas I. A Tabela 1 mostra o resultado para o MUX de 4 entradas.

| A B | Saída |

|---|---|

| 0 0 | |

| 0 1 | |

| 1 0 | |

| 1 1 |

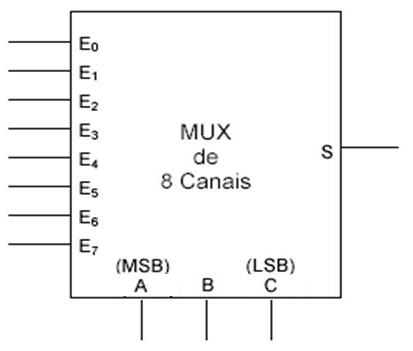

Logo, quantidade de linhas de controle depende justamente da quantidade de entradas que devem ser selecionadas. Para um MUX de 4 entradas precisamos de 2 entradas de endereçamento, pois com dois dígitos cobrimos as 4 combinações possíveis de estados de controle. Já para um MUX de 8 entradas, como o mostrado na Figura 4, precisamos de 3 entradas de endereçamento, de modo a se obter as 8 combinações de estados que definem qual entradas será a ativada. A Tabela 2 mostra a tabela verdade com as possibilidades de seleção para o MUX de 8 entradas.

Figura 4 - MUX de 8 entradas.

| A B C | Saída |

|---|---|

| 0 0 0 | |

| 0 0 1 | |

| 0 1 0 | |

| 0 1 1 | |

| 1 0 0 | |

| 1 0 1 | |

| 1 1 0 | |

| 1 1 1 |

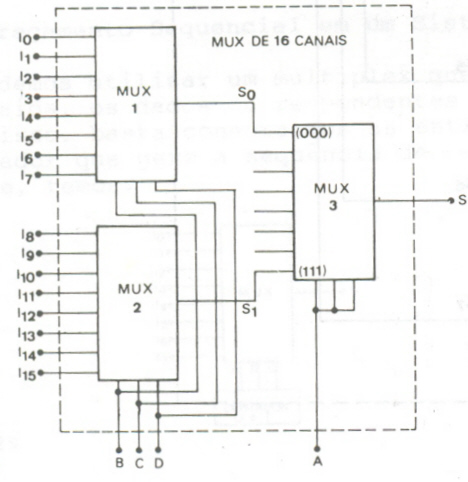

É possível ampliar a capacidade de multiplexação de mais entradas a partir de MUX com poucas entradas. Isso permite que seja disponibilizado multiplexadores comerciais de 2, 4 , 8 ou 16 entradas e a partir deles ampliar a capacidade de multiplexação. Estes circuitos digitais são valiosos nos projetos de sistemas microprocessados, pois são amplamente utilizados para acesso a bancos de memórias e dispositivos de entrada/saída como teclados e displays. A Figura 5 apresenta um MUX de 16 canais de entrada realizado a partir de MUX de 8 entradas.

Figura 5 - MUX de 16 canais utilizando MUX de 8 entradas.

Exercício de Fixação

Construa um circuito MUX de 16 entradas a partir de MUX de 4 entradas.

(realizar em sala)

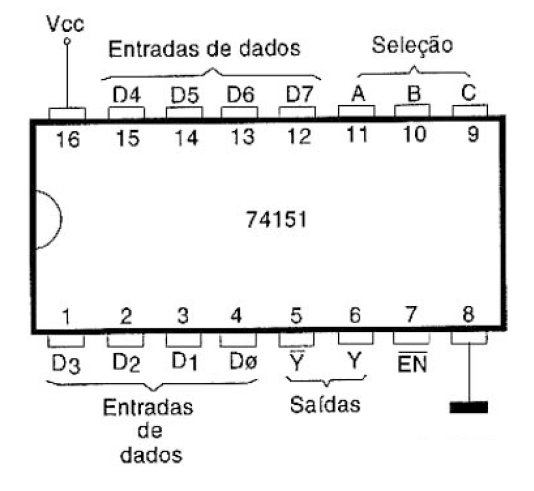

CI 74151

Este circuito TTL clássico, possui 8 entradas de dados, três linhas de seleção e duas saídas, sendo que uma apresenta o sinal da entrada na original e a outra invertido. Na operação normal a entrada EN de habilitação deve ficar no nível lógico baixo. Se esta entrada for colocada em nível alto a saída Y se mantém no nível baixo e a saída Y\ no nível alto independentemente do que acontece nas linhas de dados ou de controle. O CI 74151 é apresentado em invólucro DIL de 16 pinos com a disposição de terminais mostrada na Figura 6.

Figura 6 - CI 74151 seletor 1 de 8.

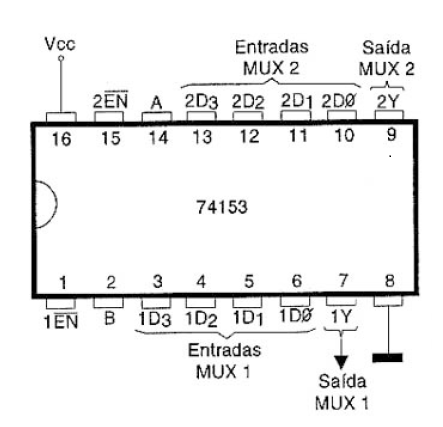

CI 74153

Este circuito integrado TTL é um duplo seletor de dados que contém dois multiplexadores de 4 entradas de dados, com duas linhas de controle que atuam ao mesmo tempo sobre os dois circuitos. Na figura 7 temos a pinagem deste componente que é apresentado também em invólucro de 16 pinos.

Figura 7 - CI 74153 com 2 MUX de 4 entradas.

Na operação normal as entradas EN devem ser mantidas no nível baixo. Com estas entradas no nível alto, a saída do multiplexador correspondente se mantém no nível baixo independentemente da entrada selecionada.

Exercício de Fixação

Realize um multiplexador de 8 entradas a partir do CI 74153.

(fazer em sala de aula)

Demultiplexadores

Naturalmente os Demultiplexadores (DEMUX) são circuitos digitais que efetuam a operação inversa dos multiplexadores, ou seja, possuem várias saídas as quais permitem receber as informações de uma única entrada, selecionadas por uma palavra binária de controle. Ou seja, a saída selecionada copia o estado da entrada. A mesma analogia de uma chave com um polo de entrada e N posições de saída pode ser usada. A Figura 8 mostra o circuito selecionador.

Figura 8 - Circuito 1 para N.

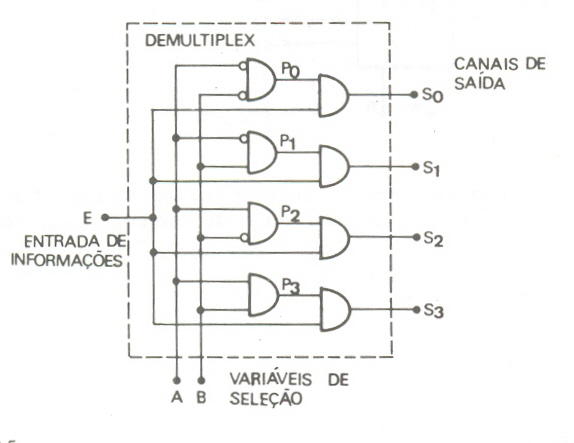

Um circuito DEMUX de 4 saídas pode ser visto na Figura 9, e sua tabela verdade ser vista a seguir. Pela

sua operação eles também podem ser utilizados como decodificadores binários BCD para as N linhas de saída.

Figura 9 - DEMUX com 1 entrada e 4 saídas.

| Seleção | Saída | |||

|---|---|---|---|---|

| A B | S0 | S1 | S2 | S3 |

| 0 0 | E | 0 | 0 | 0 |

| 0 1 | 0 | E | 0 | 0 |

| 1 0 | 0 | 0 | E | 0 |

| 1 1 | 0 | 0 | 0 | E |

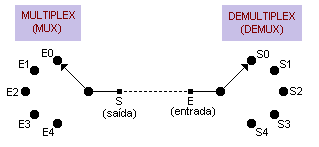

O DEMUX efetua a função inversa do MUX, ou seja, transmite informações contidas em uma linha para uma das varias linhas ou canais disponíveis. Para melhor entendermos o conceito de MUX e DEMUX, podemos fazer uma comparação com uma chave seletora, conforme

é apresentado na Figura 10.

Figura 10 - Circuito Multiplexador e Demultiplexador.

A informação de dados E0 estará presente na saída S0, através de um processo apenas mecânico, mas que deverá estar sincronizado.

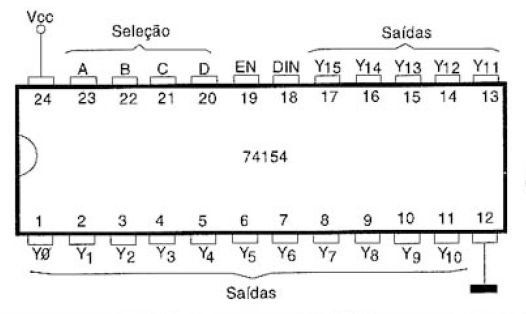

CI 74154

Este circuito integrado TTL é um DEMUX de 1 para 16 e é apresentado em invólucro DIL de 24 pinos com a pinagem mostrada na Figura 11.

Figura 11 - DEMUX com 1 entrada e 16 saídas.

Este tipo de circuito também é conhecido como "distribuidor de dados" e na operação normal a entrada EN deve ser

mantida no nível lógico baixo. Quando EN estiver no nível lógico alto, todas as saídas ficarão no nível lógico alto, independentemente do que ocorra na entrada de dados e no controle.

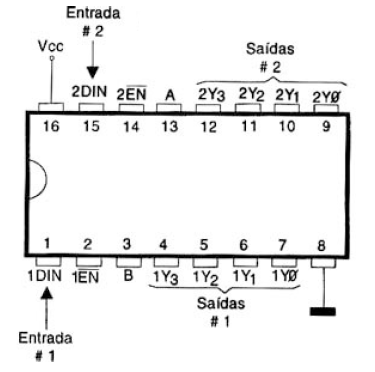

CI 74155

Este circuito integrado TTL se caracteriza por possuir dois DEMUX de 1 para 4. A Figura 12 apresenta o CI 74155 em invólucro DIL de 16 pinos.

Figura 12 - Duplo DEMUX com 1 entrada e 4 saídas.

Na operação normal a entrada EN deve estar no nível lógico baixo. Quando as entradas EN (1 e 2) estiverem em nível lógico alto, todas as saídas dos seletores ficarão no nível lógico alto, independente da seleção e dos dados das duas entradas.

Aplicações com Multiplexadores e Demultiplexadores

- Implementação de circuitos combinacionais;

- Roteamento de dados;

- Varredura de Display;

- Conversão paralelo – serial (UART);

- Conversão serial – paralelo.

Central Telefônica

Décadas de 80 e 90.

Figura 13 - Central Telefônica analógica década de 80 e 90.

Redes SDH e PDH

São sistemas comercias que transmitem bilhões de bits por segundo, suficiente, - em 1998, para levar próximo a 1 milhão de conversas simultâneas em um canal de fibra ótica. Centrais telefônicas eletrônicas, telefones celulares, modernos PABX e sistemas de transmissão trabalham, atualmente, com sinais digitais binários. Contudo, a voz humana é analógica antes de ser manipulada por esses equipamentos, deve ser digitalizada. Compreender como ocorre essa digitalização é fundamental para entender a importância de sistemas de SDH.

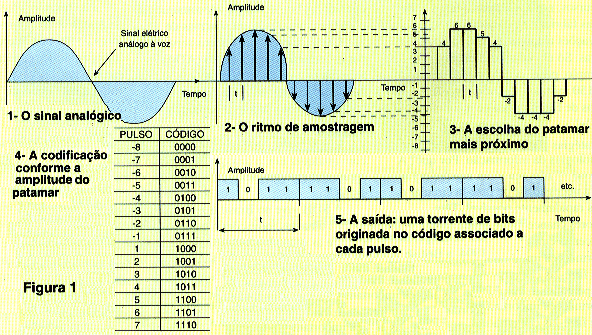

A digitalização consiste em enviar pequenas amostras do sinal elétrico análogo à voz, tomadas a intervalos regulares. Isto seria o bastante para recuperar o sinal original do outro lado da linha, onde um circuito eletrônico transformaria as amostras num sinal analógico muito semelhante ao original. Nyquist, engenheiro americano que trabalhava no Bell System nos anos 20, descobriu que a voz, quando transmitida por sistemas telefônicos, deveria ser amostrada 8 mil vezes por segundo. Que correspondia ao dobro da banda de frequência utilizada pela voz humana nas transmissões telefônicas. Esse ritmo de amostragem seria suficiente para que o sinal fosse recomposto do outro lado. A Figura 14 mostra o detalhamento do processo de digitalização.

Figura 14 - Detalhamento do processo de digitalização.

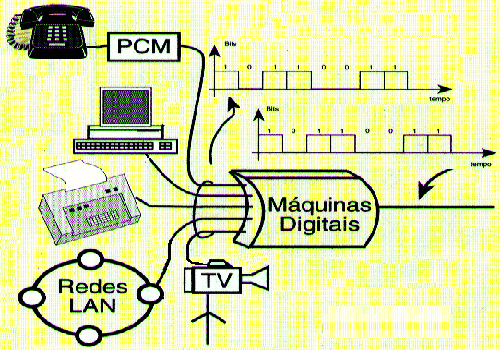

É importante perceber que como são feitas 8000 amostras por segundo e cada amostra tem 8 bits, temos 64kbits/s. Esta é a taxa de digitalização da voz humana para fins telefônicos. Estes bits passam pela linha telefônica e o receptor então constrói o sinal original devido à existência de um demodulador PCM (Pulse Code Modulation). Qualquer tipo de sinal de entrada pode ser transformado em sinal digital. Isto significa que os mesmos equipamentos projetados para voz digitalizada podem manejar qualquer outro sinal digital - dados de computadores, videoconferência, vídeo digital. A Figura 15 mostra os tipos de sinais que podem ser digitalizados e transmitidos.

Figura 15 - Sinais que podem ser digitalizados e transmitidos.

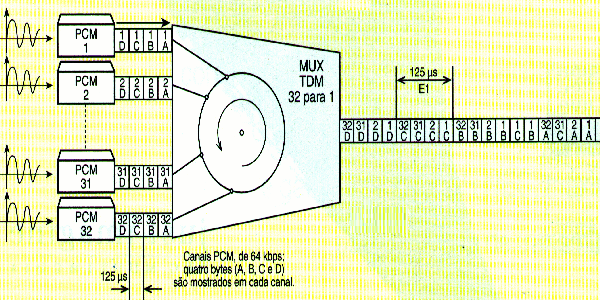

A multiplexação empregada é a TDM (time division multiplex). No caso será mostrada a multiplexação de canais PCM em um único apenas. A Figura 16 apresenta a multiplexação de canais PCM em E1.

Figura 16 - Multiplexação por divisão de tempo.

O multiplexador TDM lê o primeiro byte de cada um dos 32 canais PCM, todos ao mesmo tempo. Cada um desses bytes dura 125 us, após o que são armazenados na memória do multiplexador. Os 32 primeiros bytes de cada um dos 32 canais PCM duram o mesmo tempo (125us), em outras palavras, a velocidade da torrente de bits, na saída do mux, é de 2,048 Mbps, ou 32 vezes 64 kbps.

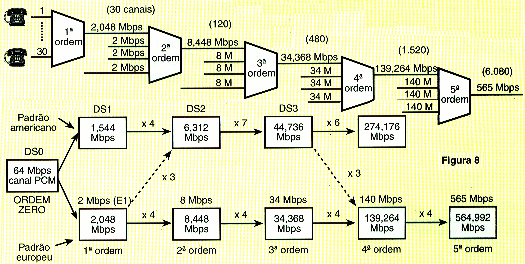

Foi criada assim uma hierarquia de máquinas TDM. As máquinas que reunem canais PCM em torno de um único canal de 2Mbits/s são TDM de primeira ordem, os que multiplexam em um canal de 8Mbits/s são TDM de segunda ordem e assim por diante. Com a concatenação de vários TDMs de ordens diferentes, é possível reunir, por exemplo, todas as ligações telefônicas de uma cidade, destinadas a outra cidade, numa única fibra óptica. A Figura 17 mostra a diferença entre o padrão americano e europeu de multiplexação TDM.

Figura 17 - Diferença entre o padrão americano e europeu de multiplexação TDM.

Fonte: https://www.gta.ufrj.br/grad/98_2/claus/sdhnow~1.html

Organização da próxima aula

Olá Alunos,

Acabamos de ver MUX e DEMUX, que são circuitos largamente utilizados na transmissão de dados, tendo vasta aplicação em telefonia, sendo que os MUXs caracterizam-se por possuir várias entradas, sendo que uma dessas entradas, através de um processo de endereçamento, é ligada à saída . Já os DEMUXs funciona de forma inversa, ou seja, uma entrada pode ser encaminhada para uma das diversas saídas, também através de um endereçamento adequado. Na próxima aula teremos a avaliação teórica 2 (AT2), cujos conteúdos são: registradores, codificadores e decodificadores e, claro, os multiplexadores e demultiplexadores.

Estudem pra AT2!

Prof. Douglas A.

Referências

[1] CASAGRANDE, Jorge H. B.. Apostila: ELETRÔNICA DIGITAL 1 CAPÍTULO 3 – Circuitos Combinacionais. CEFET/SC, 2005.