Mudanças entre as edições de "DIG222802 2017 1 AULA12"

| Linha 1: | Linha 1: | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

=Tutorial Modelsim= | =Tutorial Modelsim= | ||

Edição das 14h35min de 17 de abril de 2017

Tutorial Modelsim

Ferramentas de simulação são grandes aliadas no desenvolvimento de aplicações embarcadas, pois facilitam a vida do desenvolvedor, em FPGA é extremamente recomendado que todo o código seja testado em um simulador antes de ser sintetizado em um FPGA. Nesta aula será apresentado um rápido tutorial de modelsim.

O processo de gravar o FPGA e testar é muito mais demorado do que simplesmente rodar o simulador. Além disso não existem muitas interfaces da FPGA com o mundo externo, é praticamente impossível saber sobre tudo que está acontecendo no seu sistema em tempo real. Alguns bugs são difíceis de serem encontrados em tempo de execução pois podem ocorrer só em situações especificas que demoram muito a acontecer ou por necessitar de vários equipamentos externos para simular a situação em que ocorreriam.

O Modelsim é um simulador de HDL (Hardware Description Language) desenvolvido pela Mentor Graphics. Ele suporta a simulação das linguagens VHDL e Verilog e pode simular o código a nível de RTL (Register Transfer Level) e Gate Level. Em nível de RTL é analisado o circuito a nível de comportamento dos registradores e em Gate Level é analisado a nível de netlist com inclusão de atrasos das portas lógicas e etc.

Neste tutorial vamos apresentar o que é necessário para realizar a simulação da aplicação e seu de comportamento.

Download do Modelsim

A primeira coisa que deve ser feita, é instalar o Modelsim no seu computador. Uma edição de graça do Modelsim para estudantes pode ser obtido no site da Altera. Recomendo o download junto com o Quartus 14.

É importante notar que a versão gratuita possui algumas limitações, tais como: limitação de performance, limite para o número de linhas de código executáveis e não trabalhar com duas linguagens em um mesmo projeto (misturar VHDL e Verilog).

Criar um TestBench

Uma das utilidades de VHDL é a simulação que é usada para estudar a operação de um circuito ou para verificar se um design está correto. Fazer uma simulação em VHDL é simular um experimento com um circuito físico, em que as entradas do circuito são conectadas a algum sinal de estímulo (por exemplo, um gerador de sinais) , e com isso, as saídas deste circuito podem ser observadas.

Simular uma lógica programada em VHDL é similar a fazer um experimento virtual, em que o circuito físico é substituído pela sua descrição em VHDL, bem como os estímulos de entrada e as saídas. Este conjunto de ferramentas e práticas são implantadas em um Testbench (arquivo de teste).

O código VHDL abaixo apresenta o arquivo testbench_pisca_led.vhd para o nosso exemplo.

library ieee;

use ieee.std_logic_1164.all;

entity testbench_pisca_led is

end entity testbench_pisca_led;

architecture rtl of testbench_pisca_led is

signal clk: std_logic := '0';

signal rs: std_logic;

signal led_status: std_logic;

component pisca_led

port

(

sys_clk_50mhz : in std_logic;

sys_rst : in std_logic;

led : out std_logic

);

end component;

begin

clk <= NOT clk after 10 ns; -- clock de 50 MHz

pisca_led1: pisca_led PORT MAP(clk, rs, led_status);

end architecture rtl;

Pode-se observar as entradas de estímulo criadas do clock de 50MHz e o sinal de reset. A saída é o led_status. (10ns para alto, 10ns para baixo = período de 20ns = frequência de 50 MHz).

Para melhor visualizar a simulação o código pisca_led.vhd teve a frequência de pisca alterada para um período de 10ms. Isso foi feito alterando o valor da comparação do sinal led_delay para 500000;

library ieee;

use ieee.std_logic_1164.all;

entity pisca_led is

port

(

sys_clk_50mhz : in std_logic;

sys_rst : in std_logic;

led : out std_logic

);

end entity pisca_led;

architecture rtl of pisca_led is

signal led_delay : NATURAL range 0 to 50000000;

signal led_reg : std_logic;

begin

led <= led_reg; -- Atribui a porta de saída chamada led o valor do registrador

process(sys_clk_50mhz, sys_rst) -- Executado a cada pulso de clock ou reset

begin

if sys_rst = '0' then -- Reset assíncrono, independe do clock

led_delay <= 0;

led_reg <= '0';

elsif rising_edge(sys_clk_50mhz) then

led_delay <= led_delay + 1;

if led_delay = 500000 then

led_delay <= 0;

led_reg <= not led_reg; -- Inverte o valor do registrador do led

end if;

end if;

end process;

end architecture rtl;

A seguir será mostrado como criar um projeto no Modelsim para que os códigos apresentados sejam testados.

Criar um Projeto, Adicionar os Arquivos, e Compilar

Podemos então abrir o Modelsim. Isto deve ser o que você vai encontrar ao executar o Modelsim e clicar em Jumpstart pela primeira vez.

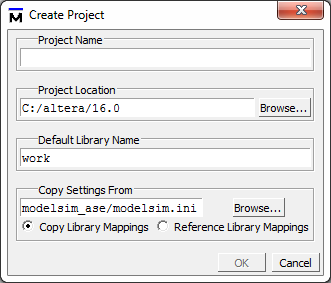

Figura 1 - Informações sobre o projeto inicial.

Preencha as informações adequadamente e clique em Ok. Uma nova janela irá se abrir.

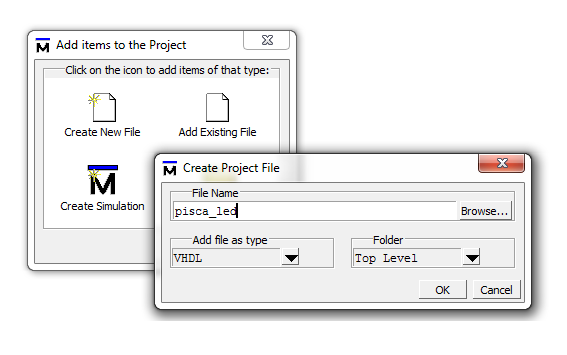

Figura 2 - Adicionando arquivos ao projeto.

Se você já tem os arquivos .vhd do Testbench e do módulo disponível pisca_led , clique em ‘Add Existing File’ e adicione os arquivos ao projeto. Se não os tiver, o Modelsim possui um editor que pode ser utilizado para esse fim. Então clique em Create New File e copie o conteúdo para o novo arquivo. A tela do seu projeto deve ficar como mostra a Figura 3.

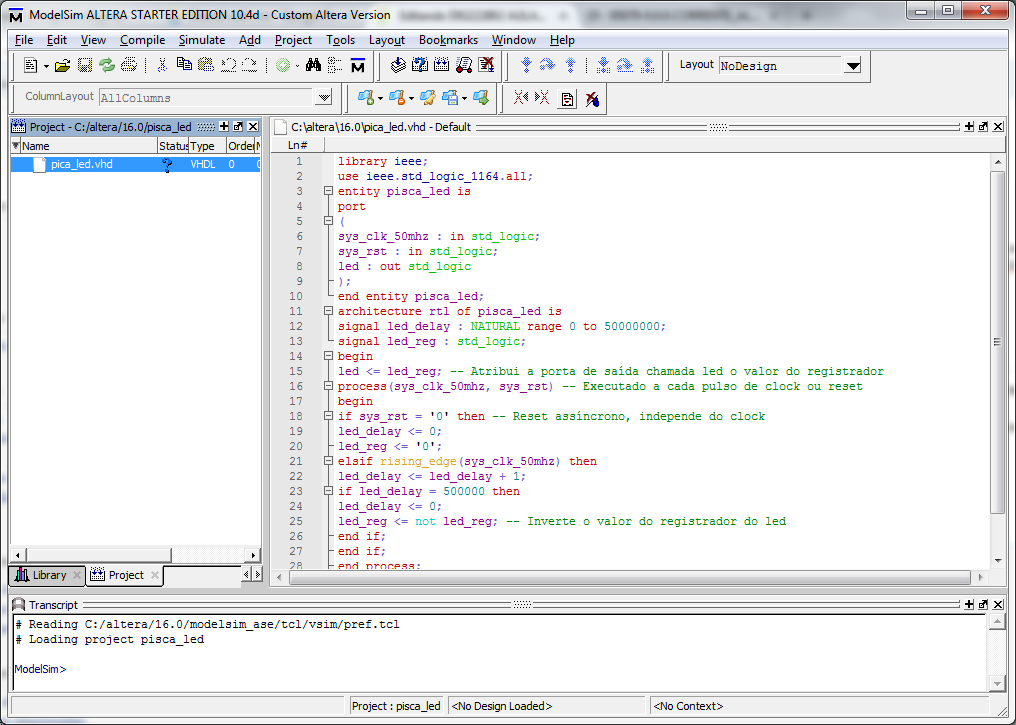

Figura 3 - Visão da tela do projeto.

Não esqueça que você deverá ter os códigos dos dois arquvios: pisca_led.vhd e testebench_pisca_led.vhd.

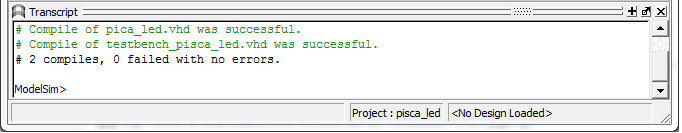

Agora vamos compilar os arquivos para isto é só clicar em Compile > Compile All. Se não houver erros nos arquivos a seguinte mensagem irá aparecer na tela Transcript:

Figura 4 - Visão da área da tela com as informações do Transcript.

Rodar a Simulação

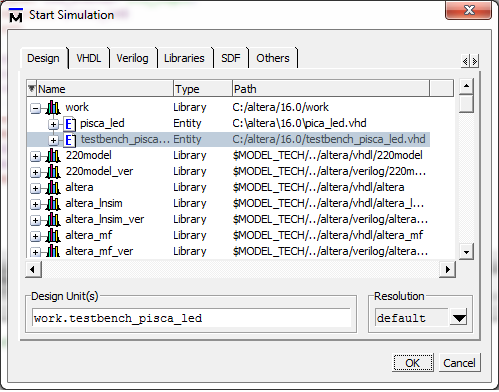

Agora vamos rodar a simulação. Para isso clique em Simulate > Start Simulation... A seguinte tela vai aparecer:

Figura 5 - Janela com as informações da Simulação.

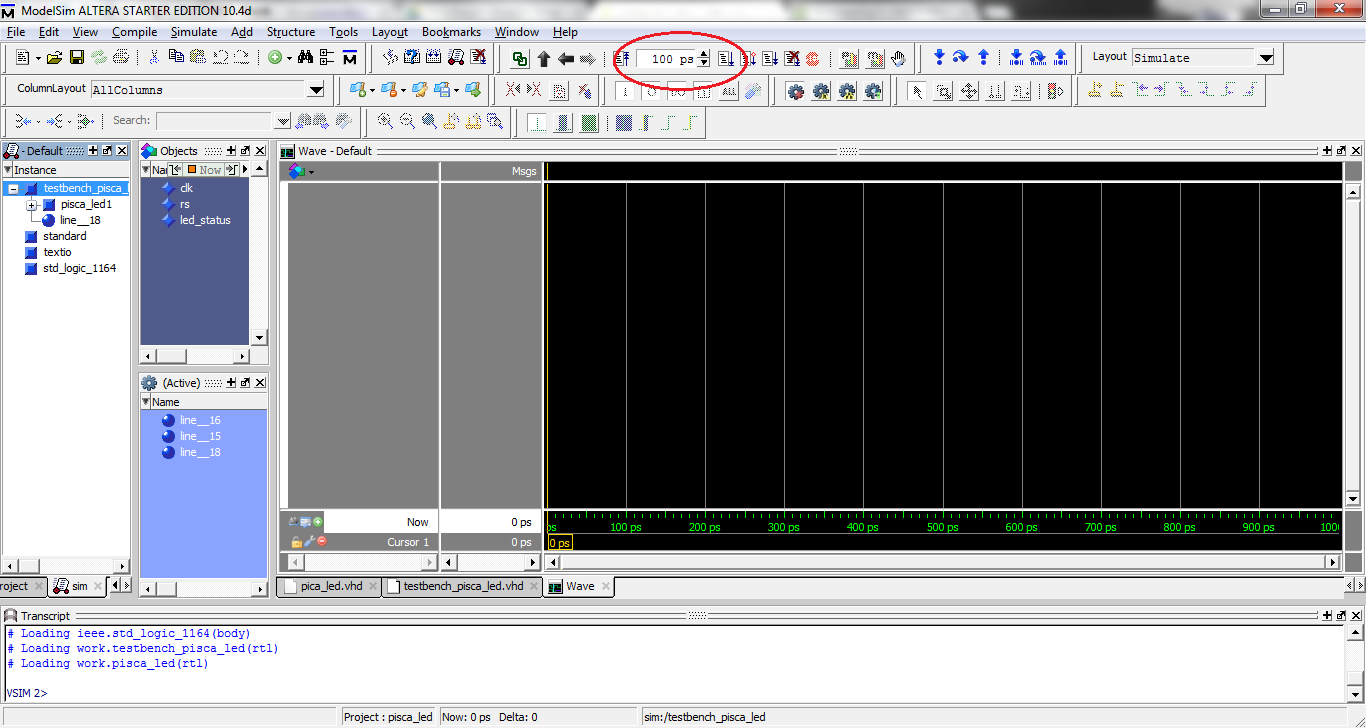

Clicando em OK, deverá aparecer a tela de Wave -default. Caso não apareça, vá em View > Wave.

Figura 6 - Janela da Simulação.

É possível observar os seguintes itens, descritos na imagem:

- Tempo de simulação: Especifica o tempo de cada passo da simulação;

- Instancias: Instâncias disponíveis;

- Objects: Sinais disponíveis dentro da instância selecionada;

- Wave: Analisador de ondas, onde é possível verificar os sinais em determinados instante de tempo.

Antes de começar a simulação, escolha os sinais de interesse que serão analisados. Para tal, selecione primeiramente a instância do testbench_pisca_led no Instance Viewer. Observe que os sinais clk, rs e led_status ficarão disponíveis em Objects. Arraste estes 3 sinais para a janela Wave. Em seguida, selecione a instância pisca_led1 e arraste o sinal led_delay para a janela Wave.

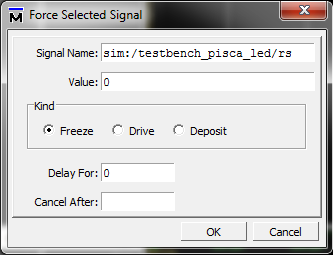

Na janela Wave, o sinal de reset não está sendo setado, e com isso ele está no estado unknown. Antes de simularmos temos que fazer com que o sinal rs fique em 0 para que ocorra o reset e os sinais sejam iniciados corretamente. Para fazer isso clique com o botão direito sobre o sinal rs. No menu que irá se abrir, clique em Forc... . Coloque value = 0 e clique em OK.

Figura 7 - Atribuindo um valor a um sinal.

Em seguida, altere o tempo do passo da simulação para 10ms e clique em play. Essa operação irá levar algum tempo devido às limitações da versão free do Modelsim.

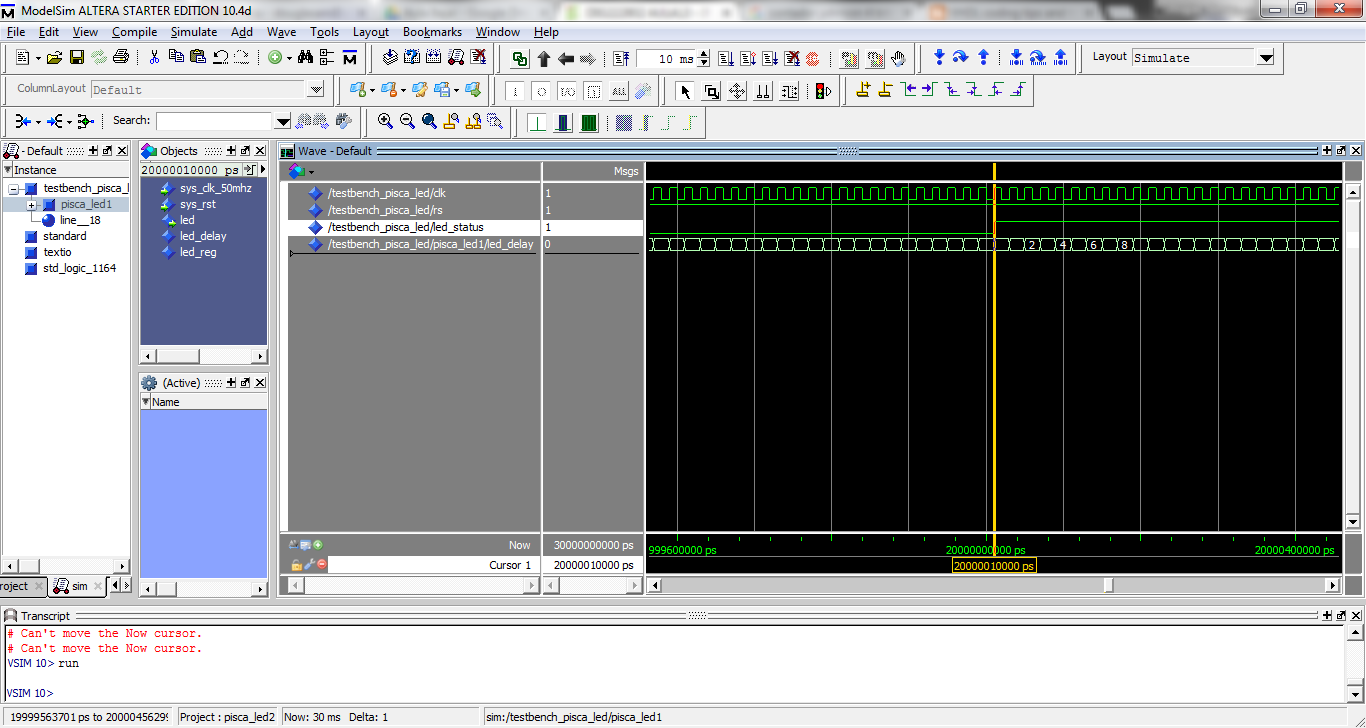

Altere o sinal de rs para 1 e rode novamente 10ms. Rode mais uma vez 10 ms.

Ao fim estará simulado 30 ms em que os primeiros 20 ms foram utilizados para dar reset no módulo de pisca_led e os próximos 10 ms foram utilizados para o led alterar seu status para 1.

Ao final da simulação, podemos observar o resultado na janela wave. O zoom (icone lupa) pode ser utilizado para melhor visualizar a simulação. Para observar o evento da alteração do status do led, selecione o sinal led_status e clique no botão para procurar o nível de borda. Conforme podemos observar na Figura 8.

Figura 8 - Resultado da simulação.

Observamos que a simulação aconteceu conforme o esperado. A cada pulso de clock, o contador led_delay foi incrementado e quando atingiu o valor 500000 (10 ms) o valor de led_status foi alterado.

Conclusões

Simulações são de suma importância para o desenvolvedor VHDL, pois o tempo de compilação de tais ferramentas é excessivamente grande conforme o projeto vai aumentando de complexidade. Fica muito trabalhoso testar um design diretamente em um placa ou kit de desenvolvimento. Além disso, ela permite verificar se o comportamento está de acordo com o projetado antes de ir para o kit, permitindo encontrar possíveis “furos”.

Por fim, sugiro que você faça algumas modificações no código, principalmente para que a simulação não demore tanto. Isso pode ser feito alterando-se o valor de comparação do registrador led_delay.

Existem diversas formas de criar um testbench e testar um circuito, neste tutorial fiz de forma básica pois a intenção era mostrar o Modelsim! Mais para frente faço um post exclusivo sobre testbenchs.

Adaptamos esse Texto Original, publicado por Andre Prado em seu blog e escrito em conjunto com Raphael Silva.

Exercício

Um contador de Johnson é um circuito digital que consiste de uma série de flip-flops do tipo D ligados entre si num circuito de com realimentação da saída Q\ do último FF na entrada D do primeiro FF. Quando o circuito é acionado todas as saídas Q dos FF ficam em nível lógico zero, enquanto todas às saídas Q\ ficam em 1.

O diagrama de circuito para um contador Johnson de 4 bits é mostrada abaixo :

Figura 9 - Contador Johnson.

O código VHDL para um contador Johnson de 4 bits é mostrado abaixo:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity johnson_counter is

port (

DAT_O : out unsigned(3 downto 0);

RST_I : in std_logic;

CLK_I : in std_logic

);

end johnson_counter;

architecture Behavioral of johnson_counter is

signal temp : unsigned(3 downto 0):=(others => '0');

begin

DAT_O <= temp;

process(CLK_I)

begin

if( rising_edge(CLK_I) ) then

if (RST_I = '1') then

temp <= (others => '0');

else

temp(1) <= temp(0);

temp(2) <= temp(1);

temp(3) <= temp(2);

temp(0) <= not temp(3);

end if;

end if;

end process;

end Behavioral;

O código testbench utilizado para testar o código é dada abaixo:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY tb2 IS

END tb2;

ARCHITECTURE behavior OF tb2 IS

--Inputs

signal RST_I : std_logic := '0';

signal CLK_I : std_logic := '0';

--Outputs

signal DAT_O : unsigned(3 downto 0);

-- Clock period definitions

constant CLK_I_period : time := 1 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: entity work.johnson_counter PORT MAP (

DAT_O => DAT_O,

RST_I => RST_I,

CLK_I => CLK_I

);

-- Clock process definitions

CLK_I_process :process

begin

CLK_I <= '0';

wait for CLK_I_period/2;

CLK_I <= '1';

wait for CLK_I_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

RST_I <= '1';

wait for 2 ns;

RST_I <= '0';

wait for 2 ns;

RST_I <= '1';

wait for 1 ns;

RST_I <= '0';

wait;

end process;

END;

Nota: Você deve definir um período de simulação de 1ns. Você deve, primeiramente, definir o sinal CLK_I como clock (botão direito do mouse > Clock...) e simular (botão run) para RST_I (botão direto do mouse > Force...) igual a 1, depois igual a zero (0).

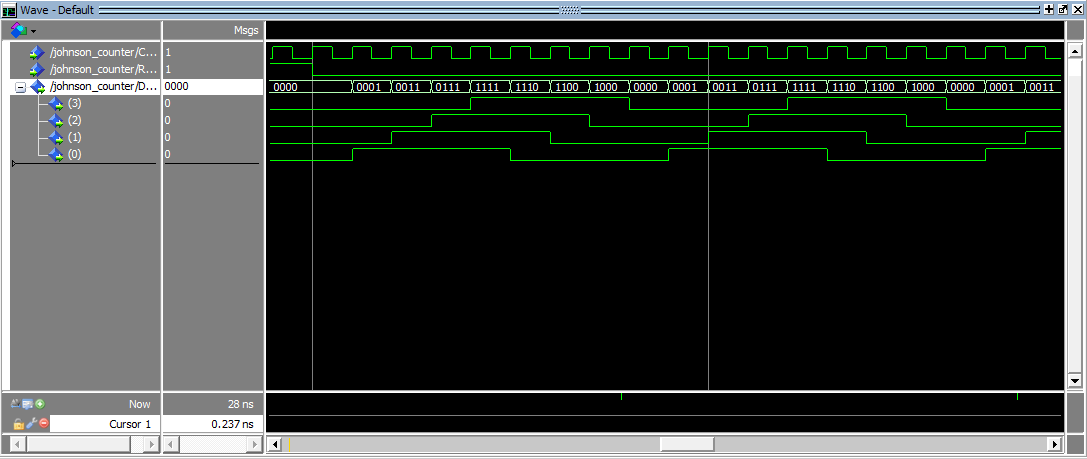

A Figura 10 mostra o resultado esperado para as formas da onda da simulação.

Figura 10 - Formas de ondas simuladas para o Contador Johnson.

Exemplos de códigos VHDL

http://wiki.sj.ifsc.edu.br/index.php/C%C3%B3digos_VHDL_para_uso_nas_Aulas

Organização das próxima aulas

Na próxima aula vamos conversar sobre o Altera Quartus II, que é um ambiente utilizado para o design de sistemas programáveis em Chip - system-on-a-programmable-chip (SOPC). A versão do Quartus II que será vista é 9.0 que oferece o máximo em desempenho e produtividade para projetos de FPGA, CPLD, entre outros.

Estudem!

Prof. Douglas A.

Referências

[1] https://www.altera.com/products/design-software/model---simulation/modelsim-altera-software.html

[2] http://www.embarcados.com.br/tutorial-de-modelsim-vhdl-fpga/