Mudanças entre as edições de "DIG222802 2017 1 AULA02"

Ir para navegação

Ir para pesquisar

(Página substituída por ' ----- link=DIG222802_2017_1_AULA01 link=DIG222802_2017_1#Aulas link=DIG222802_2017_1_AULA03') |

|||

| Linha 1: | Linha 1: | ||

| + | =Laboratório 1= | ||

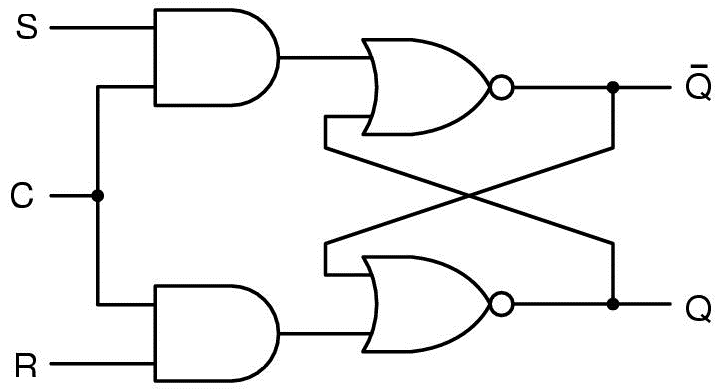

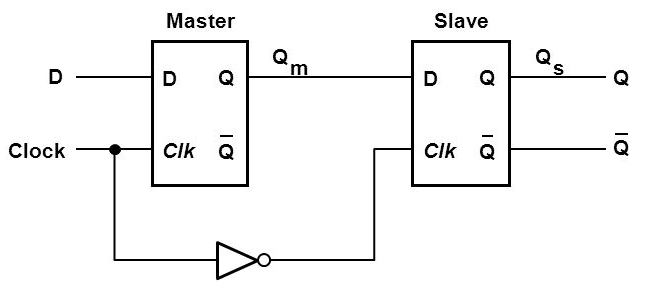

| + | O primeiro experimento da turma de Digital 2 da Engenharia vai ser realizado na LabELETRO entre 16h às 17h45min. Está dividido em duas etapas: A primeira trata-se de testar o funcionamento de um latch RS controlado feito a partir das portas lógicas AND (E) e NOR (NOU) comprovando a tabela verdade. A segunda etapa é testar o funcionamento dos flip-flops D na configuração mestre-escravo também comprovando a tabela verdade. | ||

| + | |||

| + | |||

| + | ==Parte I== | ||

| + | |||

| + | ;Objetivo: | ||

| + | |||

| + | Testar o funcionamento de um circuito latch RS controlado, feito a partir das portas lógicas AND (E) e NOR (NOU) como mostra a Figura 8. | ||

| + | |||

| + | [[Imagem:fig4_DIG222802.png|center|300px]] | ||

| + | <center> | ||

| + | Figura 8 - Latch RS controlado. | ||

| + | </center> | ||

| + | |||

| + | |||

| + | {| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

| + | |+'''Tabela Verdade''' | ||

| + | |- | ||

| + | ! style="background:#4069e1; width: 20px;" | C | ||

| + | ! style="background:#4069e1; width: 20px;" | R | ||

| + | ! style="background:#4069e1; width: 20px;" | S | ||

| + | ! style="background:#4069e1; width: 20px;" | Q | ||

| + | |- | ||

| + | | 0 | ||

| + | | X | ||

| + | | X | ||

| + | | Qa | ||

| + | |- | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | Qa | ||

| + | |- | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | |proibido | ||

| + | |} | ||

| + | *Qa: saída do estado anterior. | ||

| + | |||

| + | ==Procedimento== | ||

| + | |||

| + | #Formar as 10 equipes com 2 ou 3 integrantes; | ||

| + | #Desenhar as ligações já utilizando o esquemático dos CIs; | ||

| + | #Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima; | ||

| + | ## Fazer a ligação de VCC e GND; | ||

| + | ## Fazer a ligação de PR\ (preset) e CLR\ (clear) em VCC ou numa chave. Lembrando que são ativos baixos; | ||

| + | ## Fazer a ligação entre as portas lógicas dos circuitos integrados; | ||

| + | ## Fazer a ligação de R, S e C com chaves seletoras; | ||

| + | ## Fazer a ligação das Saídas Q e Q\ aos LEDs; | ||

| + | #Testar a tabela verdade. | ||

| + | |||

| + | ==Parte II== | ||

| + | |||

| + | ;Objetivo: Testar o funcionamento de um Flip-flop D na configuração mestre–escravo a partir do CI 7474 e uma porta inversora. O circuito a ser montado pode ser visto na Figura 9. | ||

| + | |||

| + | |||

| + | [[Imagem:fig6_DIG222802.png|center|400px]] | ||

| + | <center> | ||

| + | Figura 9 - Flip-flop tipo D na configuração mestre–escravo. | ||

| + | </center> | ||

| + | |||

| + | |||

| + | |||

| + | {| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

| + | |+'''FF tipo D''' | ||

| + | |- | ||

| + | ! style="background:#4069e1; width: 20px;" | D | ||

| + | ! style="background:#4069e1; width: 20px;" | Q | ||

| + | ! style="background:#4069e1; width: 20px;" | Q\ | ||

| + | |- | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | |} | ||

| + | |||

| + | ==Procedimento== | ||

| + | |||

| + | #Mesmas equipes; | ||

| + | #Desenhar as ligações já utilizando o esquemático dos CIs; | ||

| + | #Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima; | ||

| + | ## Fazer a ligação de VCC e GND | ||

| + | ## Fazer a ligação de PRE e CLR nas chaves seletoras. | ||

| + | ## Fazer a ligação entre as FF passando pela inversora | ||

| + | ## Fazer a ligação de D e Clock com chaves seletoras | ||

| + | ## Fazer a ligação das Saídas Qm e Qs aos LEDs | ||

| + | #Construir a tabela verdade para Qm e Qs a partir da simulação dos pulsos de clock (ligar e desligar a chave). | ||

| + | #Ligar o clock a uma frequência de 1Hz e ver o que acontece. | ||

Edição das 14h37min de 7 de fevereiro de 2017

Laboratório 1

O primeiro experimento da turma de Digital 2 da Engenharia vai ser realizado na LabELETRO entre 16h às 17h45min. Está dividido em duas etapas: A primeira trata-se de testar o funcionamento de um latch RS controlado feito a partir das portas lógicas AND (E) e NOR (NOU) comprovando a tabela verdade. A segunda etapa é testar o funcionamento dos flip-flops D na configuração mestre-escravo também comprovando a tabela verdade.

Parte I

- Objetivo

Testar o funcionamento de um circuito latch RS controlado, feito a partir das portas lógicas AND (E) e NOR (NOU) como mostra a Figura 8.

Figura 8 - Latch RS controlado.

| C | R | S | Q |

|---|---|---|---|

| 0 | X | X | Qa |

| 1 | 0 | 0 | Qa |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | proibido |

- Qa: saída do estado anterior.

Procedimento

- Formar as 10 equipes com 2 ou 3 integrantes;

- Desenhar as ligações já utilizando o esquemático dos CIs;

- Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima;

- Fazer a ligação de VCC e GND;

- Fazer a ligação de PR\ (preset) e CLR\ (clear) em VCC ou numa chave. Lembrando que são ativos baixos;

- Fazer a ligação entre as portas lógicas dos circuitos integrados;

- Fazer a ligação de R, S e C com chaves seletoras;

- Fazer a ligação das Saídas Q e Q\ aos LEDs;

- Testar a tabela verdade.

Parte II

- Objetivo

- Testar o funcionamento de um Flip-flop D na configuração mestre–escravo a partir do CI 7474 e uma porta inversora. O circuito a ser montado pode ser visto na Figura 9.

Figura 9 - Flip-flop tipo D na configuração mestre–escravo.

| D | Q | Q\ |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 1 | 0 |

Procedimento

- Mesmas equipes;

- Desenhar as ligações já utilizando o esquemático dos CIs;

- Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima;

- Fazer a ligação de VCC e GND

- Fazer a ligação de PRE e CLR nas chaves seletoras.

- Fazer a ligação entre as FF passando pela inversora

- Fazer a ligação de D e Clock com chaves seletoras

- Fazer a ligação das Saídas Qm e Qs aos LEDs

- Construir a tabela verdade para Qm e Qs a partir da simulação dos pulsos de clock (ligar e desligar a chave).

- Ligar o clock a uma frequência de 1Hz e ver o que acontece.