Mudanças entre as edições de "DIG222802 2016 2 AULA06"

(Limpou toda a página) |

|||

| (6 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

| + | =Laboratório 2= | ||

| + | O segundo experimento da turma de Digital 2 da Engenharia vai ser realizado na LabDIG (104) entre 10h e 11h30min (turma 1) e entre 16h40min e 17h30min. Vamos testar um contador crescente utilizando um único circuito integrado (CI) funcionando como relógio (clock de 1Hz). O experimento Está dividido em duas etapas: A primeira trata-se de montar um contador crescente de 0 a 9 com o integrado 74193, mostrando o resultado (unidade) em um display de 7 seg através de um um circuito BCD 7447. A segunda parte é montar mais um display (dezena) para contar de 0 a 59. | ||

| + | ==Parte 1== | ||

| + | |||

| + | ;Objetivo: Montar um contador crescente de 0 a 9 com CI 74193 apresentando o resultado da contagem em um display de 7 segmentos a partir do BCD 7447. O circuito correspondente é apresentado na Figura 1 denominado Parte 1. | ||

| + | |||

| + | [[Imagem:fig37_DIG222802.png|center|600px]] | ||

| + | <center> | ||

| + | Figura 1 - Contador crescente de dois dígitos com 74193. | ||

| + | </center> | ||

| + | |||

| + | ==Procedimento== | ||

| + | |||

| + | #Formar até 10 equipes com preferencialmente 2 integrantes; | ||

| + | #Desenhar as ligações utilizando o esquemático dos CIs; | ||

| + | #Testar o funcionamento do gerador de frequência da bancada digital (alguns não estão funcionando); | ||

| + | #Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima; | ||

| + | ## Fazer a ligação de VCC e GND; | ||

| + | ## Fazer a ligação de PL em VCC. Lembrando que esta porta é ativo baixo; | ||

| + | ## Fazer a ligação entre as portas lógicas dos CIs; | ||

| + | ## Fazer a ligação de ''clock'' com gerador de frequência de 1Hz, ou colocando numa chave seletora; | ||

| + | #Testar o funcionamento e fazer as correções necessários e ligações que por ventura estiverem faltando. | ||

| + | |||

| + | Lembrando, o circuito foi simulado no Proteus e funciona. Poderá haver algumas ligações (extras) de outros pinos em VCC/GND não detectadas na simulação. | ||

| + | |||

| + | ==Parte 2== | ||

| + | |||

| + | ;Objetivo: Montar um segundo módulo para contar de 0 a 5 apresentado o resultado também no display de 7 segmentos através de 7447. | ||

| + | |||

| + | |||

| + | ==Procedimento== | ||

| + | |||

| + | #Mesmas equipes; | ||

| + | #Repetir as ligações utilizando o esquemático dos CIs já realizado; | ||

| + | #Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima; | ||

| + | ## Fazer a ligações como na Parte 1; | ||

| + | ## Fazer a ligação do ''clock'' a partir da saída da AND (MR); | ||

| + | #Testar o funcionamento e fazer as correções necessárias e ligações que por ventura estiverem faltando. | ||

| + | |||

| + | ==Desafio== | ||

| + | |||

| + | Fazer um cronometro regressivo de 59 até 0 simulado no Proteus. | ||

| + | |||

| + | =Material Utilizado= | ||

| + | |||

| + | #CI 74193 (contador UP/DOWN 4 bits) (Figura 2) | ||

| + | #CI 7447 (conversor BCD 7 seg) (Figura 3) | ||

| + | #CI 7408 (AND) (Figura 4) | ||

| + | #Display de 7 segmento anodo comum (Figura 5) | ||

| + | #Resistor de 220/330 ohms | ||

| + | #Capacitor de 56pF | ||

| + | #fios diversos | ||

| + | #bancada digital | ||

| + | |||

| + | ==Circuitos== | ||

| + | |||

| + | |||

| + | [[Imagem:CI_74192_74193.png|center|350px]] | ||

| + | <center> | ||

| + | Figura 2 - Esquemático do CI 74192/74193 - Contador UP/DOWN de 4 bits. | ||

| + | </center> | ||

| + | |||

| + | |||

| + | [[Imagem:CI_7447.png|center|350px]] | ||

| + | <center> | ||

| + | Figura 3 - Esquemático do CI 7447 - Conversor BCD 7 segmentos. | ||

| + | </center> | ||

| + | |||

| + | |||

| + | [[Imagem:CI_7408.png|center|250px]] | ||

| + | <center> | ||

| + | Figura 4 - Esquemático do CI 7408 - Portas AND. | ||

| + | </center> | ||

| + | |||

| + | |||

| + | [[Imagem:display7seg_pinagem.jpg|center|200px]] | ||

| + | <center> | ||

| + | Figura 5 - Display de 7 segmentos anodo comum. | ||

| + | </center> | ||

| + | |||

| + | =Relatório= | ||

| + | |||

| + | O relatório deverá ser entregue, pela turma 1 até 13h30min, e pela turma dois até 19h. As equipes que não terminaram as duas partes do experimento, podem fazer o relatório da parte 1 e relatar o que aconteceu com a parte 2. | ||

| + | |||

| + | |||

| + | ==Relatório Simplificado== | ||

| + | |||

| + | ;Critérios avaliativos: | ||

| + | |||

| + | ::Prática (montagem/equipe): 6 | ||

| + | ::Procedimento experimental: 2 | ||

| + | ::Resultados e discussões : 2 | ||

| + | |||

| + | ::'''Resultado''': 10 | ||

| + | |||

| + | |||

| + | |||

| + | |||

| + | |||

| + | ----- | ||

| + | {| border="1" cellpadding="5" cellspacing="0" | ||

| + | ! style="background:#00BFFF;" | [[DIG222802_2016_2_AULA05 | << ]] | ||

| + | ! style="background:#789;" | [[DIG222802_2016_2 | <> ]] | ||

| + | ! style="background:#00BFFF;" | [[DIG222802_2016_2_AULA07 | >> ]] | ||

| + | |} | ||

Edição atual tal como às 16h17min de 4 de outubro de 2016

Laboratório 2

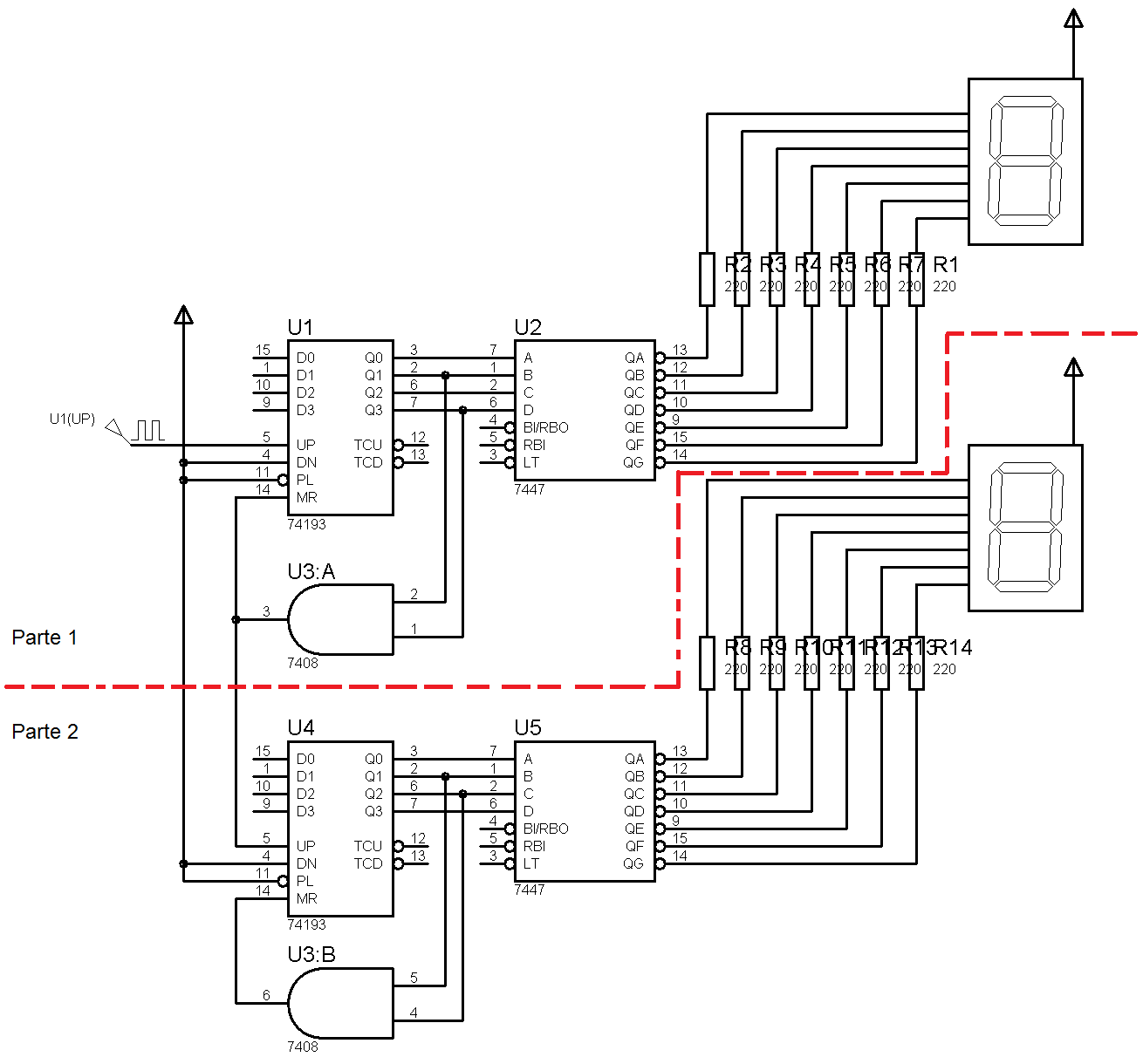

O segundo experimento da turma de Digital 2 da Engenharia vai ser realizado na LabDIG (104) entre 10h e 11h30min (turma 1) e entre 16h40min e 17h30min. Vamos testar um contador crescente utilizando um único circuito integrado (CI) funcionando como relógio (clock de 1Hz). O experimento Está dividido em duas etapas: A primeira trata-se de montar um contador crescente de 0 a 9 com o integrado 74193, mostrando o resultado (unidade) em um display de 7 seg através de um um circuito BCD 7447. A segunda parte é montar mais um display (dezena) para contar de 0 a 59.

Parte 1

- Objetivo

- Montar um contador crescente de 0 a 9 com CI 74193 apresentando o resultado da contagem em um display de 7 segmentos a partir do BCD 7447. O circuito correspondente é apresentado na Figura 1 denominado Parte 1.

Figura 1 - Contador crescente de dois dígitos com 74193.

Procedimento

- Formar até 10 equipes com preferencialmente 2 integrantes;

- Desenhar as ligações utilizando o esquemático dos CIs;

- Testar o funcionamento do gerador de frequência da bancada digital (alguns não estão funcionando);

- Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima;

- Fazer a ligação de VCC e GND;

- Fazer a ligação de PL em VCC. Lembrando que esta porta é ativo baixo;

- Fazer a ligação entre as portas lógicas dos CIs;

- Fazer a ligação de clock com gerador de frequência de 1Hz, ou colocando numa chave seletora;

- Testar o funcionamento e fazer as correções necessários e ligações que por ventura estiverem faltando.

Lembrando, o circuito foi simulado no Proteus e funciona. Poderá haver algumas ligações (extras) de outros pinos em VCC/GND não detectadas na simulação.

Parte 2

- Objetivo

- Montar um segundo módulo para contar de 0 a 5 apresentado o resultado também no display de 7 segmentos através de 7447.

Procedimento

- Mesmas equipes;

- Repetir as ligações utilizando o esquemático dos CIs já realizado;

- Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima;

- Fazer a ligações como na Parte 1;

- Fazer a ligação do clock a partir da saída da AND (MR);

- Testar o funcionamento e fazer as correções necessárias e ligações que por ventura estiverem faltando.

Desafio

Fazer um cronometro regressivo de 59 até 0 simulado no Proteus.

Material Utilizado

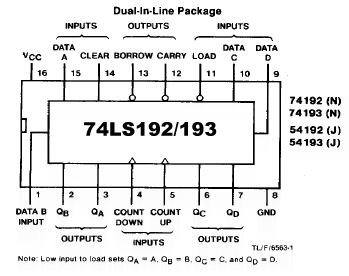

- CI 74193 (contador UP/DOWN 4 bits) (Figura 2)

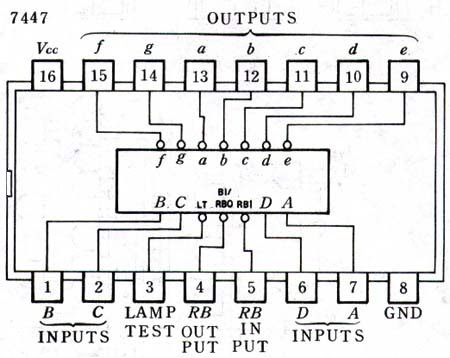

- CI 7447 (conversor BCD 7 seg) (Figura 3)

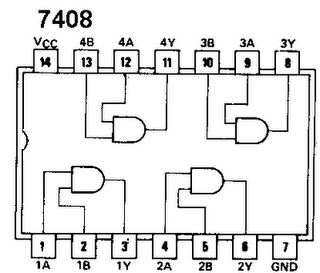

- CI 7408 (AND) (Figura 4)

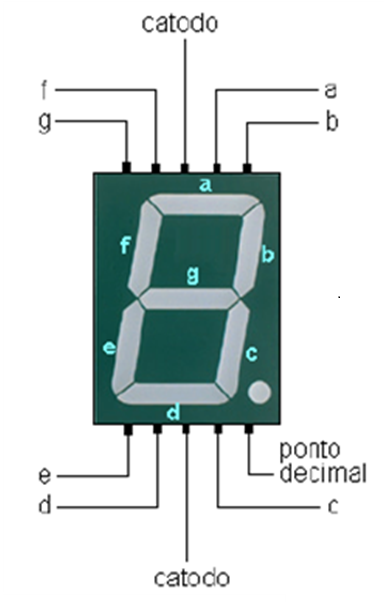

- Display de 7 segmento anodo comum (Figura 5)

- Resistor de 220/330 ohms

- Capacitor de 56pF

- fios diversos

- bancada digital

Circuitos

Figura 2 - Esquemático do CI 74192/74193 - Contador UP/DOWN de 4 bits.

Figura 3 - Esquemático do CI 7447 - Conversor BCD 7 segmentos.

Figura 4 - Esquemático do CI 7408 - Portas AND.

Figura 5 - Display de 7 segmentos anodo comum.

Relatório

O relatório deverá ser entregue, pela turma 1 até 13h30min, e pela turma dois até 19h. As equipes que não terminaram as duas partes do experimento, podem fazer o relatório da parte 1 e relatar o que aconteceu com a parte 2.

Relatório Simplificado

- Critérios avaliativos

- Prática (montagem/equipe): 6

- Procedimento experimental: 2

- Resultados e discussões : 2

- Resultado: 10

| << | <> | >> |

|---|