Mudanças entre as edições de "DI2022802 2020 2 AULA05"

Ir para navegação

Ir para pesquisar

| Linha 86: | Linha 86: | ||

|} | |} | ||

*Qa: saída do estado anterior. | *Qa: saída do estado anterior. | ||

| − | + | ::13. Por quê surgiu o Latch tipo D? | |

| + | ::14. Complete o diagrama abaixo transformando o Latch RS controlado em Latch tipo D. Em seguida, complete a tabela verdade. | ||

----- | ----- | ||

Edição das 12h26min de 30 de novembro de 2020

Lista de Exercícios para AT1

- 1. O que é um circuito digital Combinacional?

- 2. O que é um circuito digital Sequencial?

- 3. Qual a diferença entre um circuito Combinacional e um Sequencial?

- 4. O circuito Sequencial pode ser dividido em quantos grupos e quais são?

- 5. Qual a diferença entre Síncrono e Assíncrono?

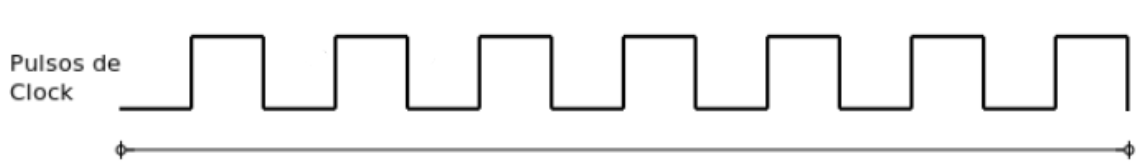

- 6. Observe a figura abaixo e faça o que se pede:

- a) Identifique o que é borda de subida e borda de descida.

- b) Identifique apenas um período do clock.

- c) Quanto pulsos de clock completos tem na figura?

- d) Se num osciloscópio a forma de onda completa aparecer numa escala de, 14s do início ao

- fim, qual é a frequência e o período deste clock?

- e) Na lógica TTL qual são os valores para nível lógico alto (1) e nível lógico baixo (0)?

- 7. Qual frequência de um sinal de relógio com 1ms de período?

- 8. Qual o período de um sinal de relógio com 100MHz?

- 9. O que são os Latches?

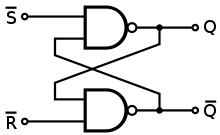

- 10. O RS é o Latch mais simples que existe e é mostrado na figura abaixo. Complete a tabela verdade abaixo considerando que inicialmente Q=0 e Q\=1.

R S Q Q\ 0 0 0 1 0 1 1 0 1 1

*Perceba que RS não estão barrados na tabela.

- 11. Complete a figura da questão anterior, transformando-a num Latch RS controlado.

- 12. Complete a tabela verdade para o RS Controlado mostrado abaixo considerando que inicialmente Q=Q e Q\=Q\.

C R S Q Q\ 0 X X Qa Qa\ 1 0 0 1 0 1 1 1 0 1 1 1

*Qa: saída do estado anterior.

- 13. Por quê surgiu o Latch tipo D?

- 14. Complete o diagrama abaixo transformando o Latch RS controlado em Latch tipo D. Em seguida, complete a tabela verdade.