Mudanças entre as edições de "DI2022802 2020 2 AULA05"

Ir para navegação

Ir para pesquisar

(→Parte2) |

|||

| (24 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 9: | Linha 9: | ||

:5. Qual a diferença entre Síncrono e Assíncrono? | :5. Qual a diferença entre Síncrono e Assíncrono? | ||

:6. Observe a figura abaixo e faça o que se pede: | :6. Observe a figura abaixo e faça o que se pede: | ||

| − | ::[[Imagem:fig120_DIG222802.png|600px]] | + | ::[[Imagem:fig120_DIG222802.png|600px|border]] |

::a) Identifique o que é borda de subida e borda de descida. | ::a) Identifique o que é borda de subida e borda de descida. | ||

::b) Identifique apenas um período do clock. | ::b) Identifique apenas um período do clock. | ||

::c) Quanto pulsos de clock completos tem na figura? | ::c) Quanto pulsos de clock completos tem na figura? | ||

| − | ::d) Se num osciloscópio a forma de onda completa aparecer numa escala de, 14s do início ao | + | ::d) Se num osciloscópio a forma de onda completa aparecer numa escala de, 14s do início ao fim, qual é a frequência e o período deste clock? |

| − | |||

::e) Na lógica TTL qual são os valores para nível lógico alto (1) e nível lógico baixo (0)? | ::e) Na lógica TTL qual são os valores para nível lógico alto (1) e nível lógico baixo (0)? | ||

:7. Qual frequência de um sinal de relógio com 1ms de período? | :7. Qual frequência de um sinal de relógio com 1ms de período? | ||

| Linha 20: | Linha 19: | ||

:9. O que são os Latches? | :9. O que são os Latches? | ||

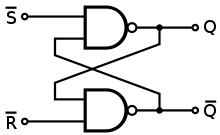

:10. O RS é o Latch mais simples que existe e é mostrado na figura abaixo. Complete a tabela verdade abaixo considerando que inicialmente Q=0 e Q\=1. | :10. O RS é o Latch mais simples que existe e é mostrado na figura abaixo. Complete a tabela verdade abaixo considerando que inicialmente Q=0 e Q\=1. | ||

| − | ::[[Imagem:fig121_DIG222802.png|300px]] | + | ::[[Imagem:fig121_DIG222802.png|300px|border]] |

::{| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ::{| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

! style="background:#808080; color:white; width: 20px;" | R | ! style="background:#808080; color:white; width: 20px;" | R | ||

| Linha 49: | Linha 48: | ||

*Perceba que RS não estão barrados na tabela. | *Perceba que RS não estão barrados na tabela. | ||

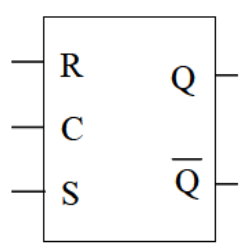

:11. Complete a figura da questão anterior, transformando-a num Latch RS controlado. | :11. Complete a figura da questão anterior, transformando-a num Latch RS controlado. | ||

| − | :12. Complete a tabela verdade para o RS Controlado | + | :12. Complete a tabela verdade abaixo para o RS Controlado de questão anterior considerando que inicialmente Q=Q e Q\=Q\. |

::{| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ::{| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

! style="background:#808080; color:white; width: 20px;" | C | ! style="background:#808080; color:white; width: 20px;" | C | ||

| Linha 88: | Linha 87: | ||

|} | |} | ||

*Qa: saída do estado anterior. | *Qa: saída do estado anterior. | ||

| − | + | :13. Por quê surgiu o Latch tipo D? | |

| − | + | :14. Complete o diagrama abaixo transformando o Latch RS controlado em Latch tipo D. Em seguida, complete a tabela verdade mais abaixo. | |

| + | ::[[Imagem:fig122_DIG222802.png|150px|border]] | ||

| + | ::{| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

| + | ! style="background:#808080; color:white; width: 20px;" | D | ||

| + | ! style="background:#808080; color:white; width: 20px;" | Q | ||

| + | |- | ||

| + | | 0 | ||

| + | | | ||

| + | |- | ||

| + | | 1 | ||

| + | | | ||

| + | |} | ||

| + | :15. Complete. Os _____________ são elementos de circuito que podem apresentar _______ | ||

| + | ::estados estáveis. A aplicação de sinal de ______________ pode alterar o estado de suas | ||

| + | ::_________________. É possível considerar que o circuito é uma _________________ capaz | ||

| + | ::de armazenar ______ bit. | ||

| + | :16. Desenhe um circuito do flip-flop RS por borda de subida e outro por borda de descida. | ||

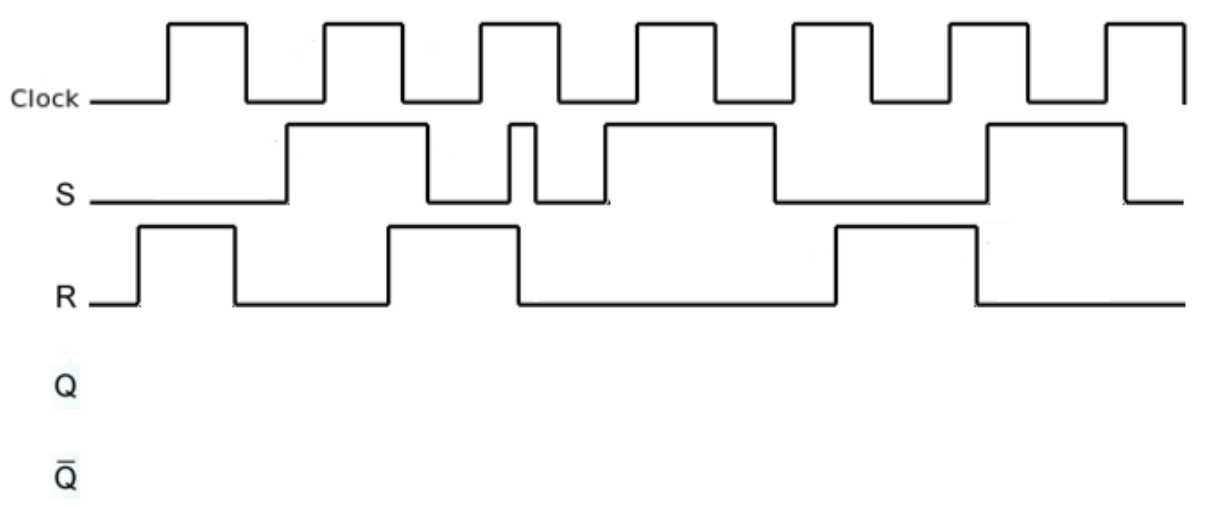

| + | :17. Complete a forma de onda (Q e Q\) da figura abaixo, para um circuito de um flip-flop RS sensível a borda de subida do clock. | ||

| + | ::[[Imagem:fig123_DIG222802.png|600px|border]] | ||

| + | :18. Complete a forma de onda (Q e Q\) da figura abaixo, para um circuito de um flip-flop RS com borda de descida do clock. | ||

| + | ::[[Imagem:fig123_DIG222802.png|600px|border]] | ||

| + | :19. Como funciona o flip-flop tipo D? | ||

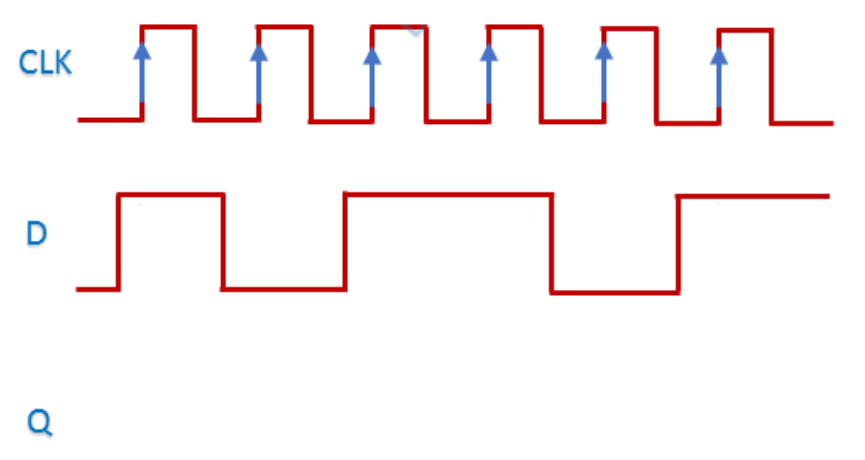

| + | :20. Complete a forma de onda da figura abaixo, para um circuito do flip-flip tipo D com borda de subida do clock. | ||

| + | ::[[Imagem:fig124_DIG222802.png|500px|border]] | ||

| + | :21. Complete. No _________________ J-K quando houver variação do _____________, o valor | ||

| + | ::guardado no flip-flop será alternado se as entradas J e K forem iguais a ________ e será | ||

| + | ::mantido se ambas forem iguais a ______. No caso de serem diferentes, então o valor se | ||

| + | ::tornará ________ se a entrada J (Jump) for ________ e será __________ se a entrada K | ||

| + | ::(Kill) for _________. | ||

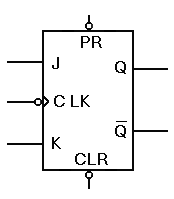

| + | :22. A figura abaixo mostra o símbolo utilizado para o flip-flop JK. Descreva todas as características apresentadas no diagrama. | ||

| + | ::[[Imagem:fig12_DIG222802.png|border|150px]] | ||

| + | 21. Preencha a tabela verdade para o flip-flop JK. | ||

| + | ::{| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

| + | ! style="background:#808080; color:white; width: 20px;" | J | ||

| + | ! style="background:#808080; color:white; width: 20px;" | K | ||

| + | ! style="background:#808080; color:white; width: 20px;" | Q | ||

| + | ! style="background:#808080; color:white; width: 20px;" | Q\ | ||

| + | |- | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | | ||

| + | | | ||

| + | |- | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | | ||

| + | | | ||

| + | |- | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | | ||

| + | | | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | | ||

| + | | | ||

| + | |} | ||

| + | :22. Transforme o flip-flop JK em tipo T. | ||

| + | ::[[Imagem:fig12_DIG222802.png|border|150px]] | ||

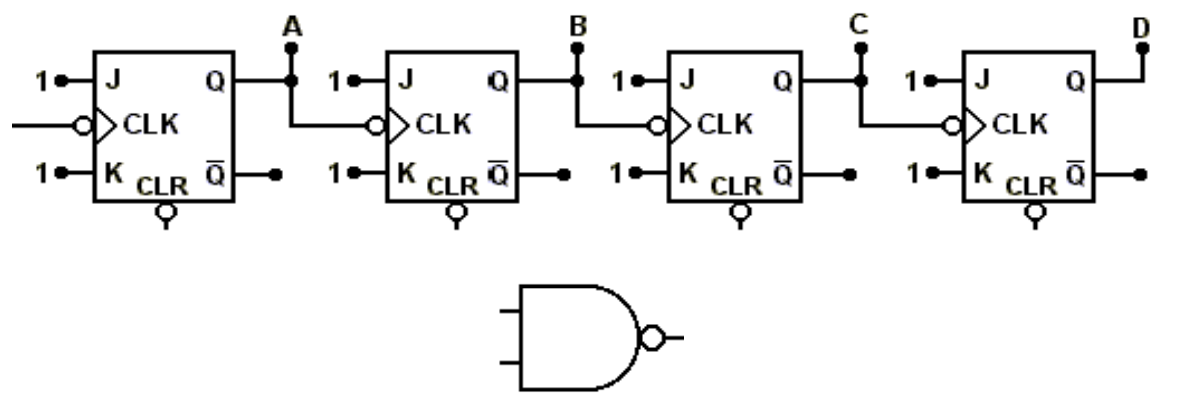

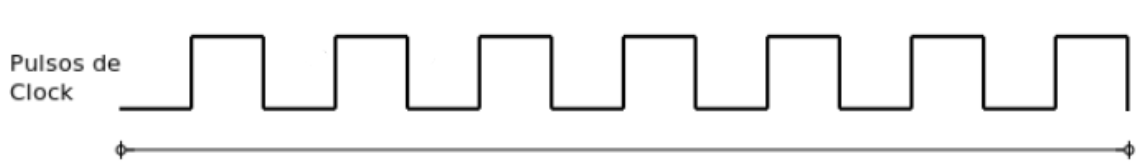

| + | :23. Um circuito típico de um contador assíncrono construído com FF do tipo JK é mostrado na figura abaixo. Responda: | ||

| + | ::[[Imagem:fig125_DIG222802.png|600px|border]] | ||

| + | ::a) Quantos bits têm esse contador? | ||

| + | ::b) É possível contar de quanto até quanto em binário e em decimal? | ||

| + | ::c) Por quê J e K são iguais a 1? | ||

| + | ::d) Esse contador é crescente ou decrescente? | ||

| + | ::e) Se for crescente, como transformar para decrescente? | ||

| + | ::f) Se for decrescente, como transformar para crescente? | ||

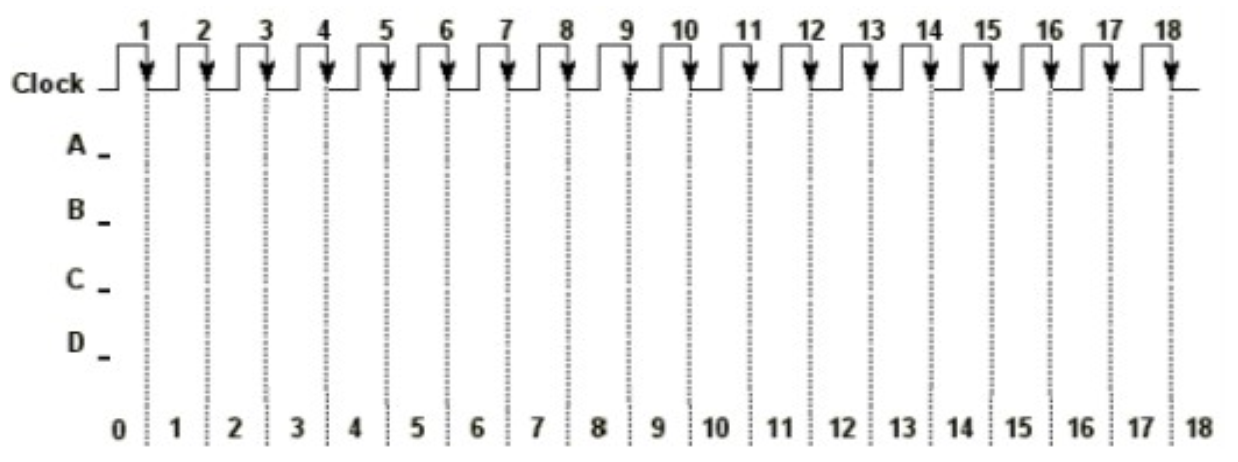

| + | ::g) Complete a forma de onda abaixo para o crescente: | ||

| + | ::[[Imagem:fig126_DIG222802.png|600px|border]] | ||

| + | ::h) Complete a forma de onda abaixo para o decrescente: | ||

| + | ::[[Imagem:fig126_DIG222802.png|600px|border]] | ||

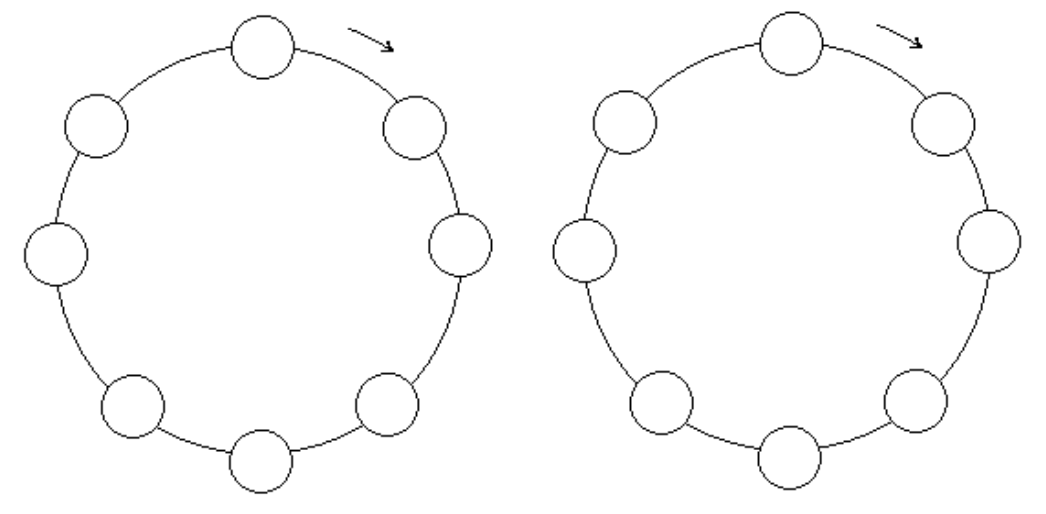

| + | :24. Preencha nas figuras abaixo, o diagrama de estados de um contador crescente e de um contador decrescente em binário de 3 bits. | ||

| + | ::[[Imagem:fig127_DIG222802.png|600px|border]] | ||

| + | :25. O que é um contador de módulo? Pra quê serve? | ||

| + | :26. O que é o estado temporário ou não atingível de um contador de módulo? | ||

| + | :27. Quantos flip-flops são necessários para contar de 0 a 99, ou seja, MOD-100? | ||

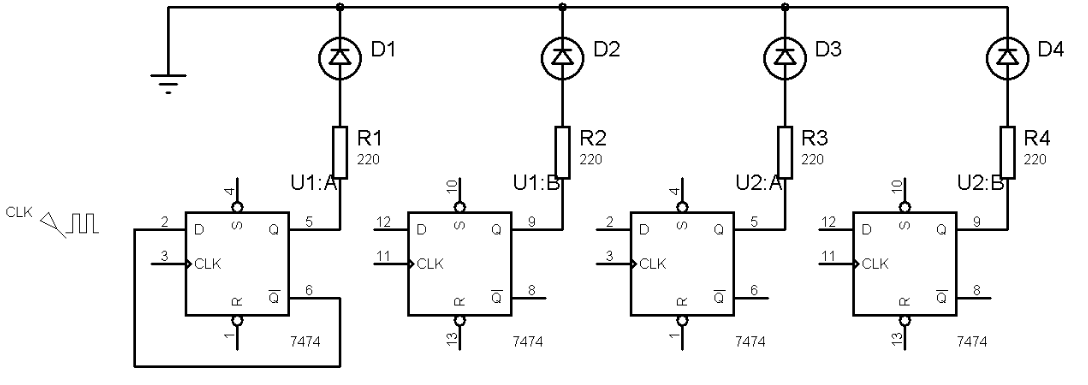

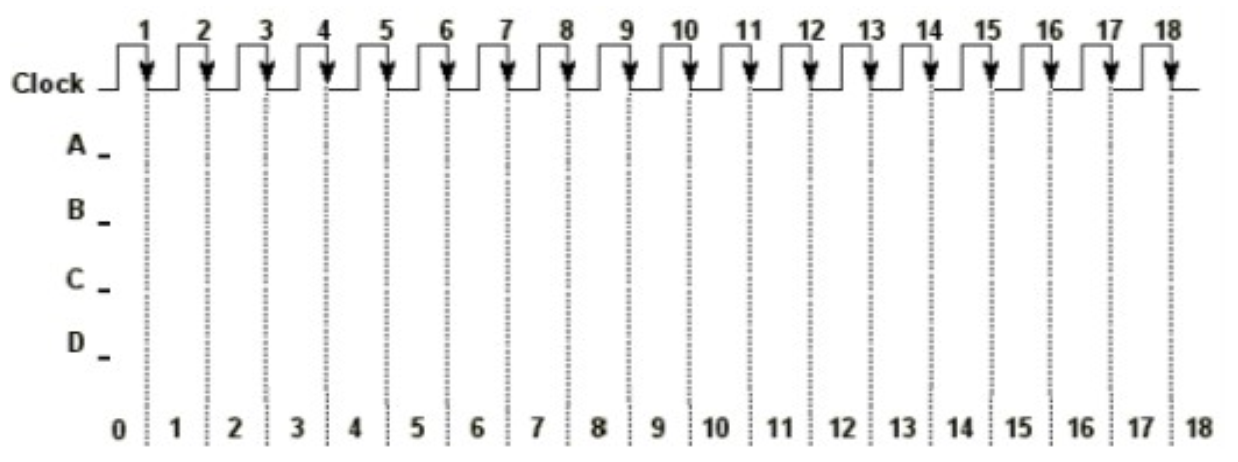

| + | :28. A figura abaixo representa um contador de 4 bits, transforme ele em um contador MOD-10, ou seja, deve contar de 0 a 9. | ||

| + | ::[[Imagem:fig128_DIG222802.png|600px|border]] | ||

| + | 29. Complete a forma de onda para o circuito da questão anterior. | ||

| + | ::[[Imagem:fig126_DIG222802.png|600px|border]] | ||

| + | 30. O que são os atrasos de propagação dos contadores assíncronos e o quê isso implica? | ||

==Parte2== | ==Parte2== | ||

| − | |||

:1. Complete o circuito abaixo para que funcione como contador '''assíncrono''' crescente. | :1. Complete o circuito abaixo para que funcione como contador '''assíncrono''' crescente. | ||

| − | ::[[Imagem:fig78_DIG222802.png|600px]] | + | ::[[Imagem:fig78_DIG222802.png|600px|border]] |

:2. Utilizando o mesmo circuito, faça as modificações necessárias para que funcione como contador '''assíncrono''' decrescente. | :2. Utilizando o mesmo circuito, faça as modificações necessárias para que funcione como contador '''assíncrono''' decrescente. | ||

:3. Explique o funcionamento do contador '''síncrono''' crescente visto da figura abaixo. | :3. Explique o funcionamento do contador '''síncrono''' crescente visto da figura abaixo. | ||

| − | ::[[Imagem:fig79_DIG222802.png|400px]] | + | ::[[Imagem:fig79_DIG222802.png|400px|border]] |

:4. Quantos FF e portas lógicas eu preciso para fazer um contador síncrono que conte 0 até 100. Apresente os cálculos. | :4. Quantos FF e portas lógicas eu preciso para fazer um contador síncrono que conte 0 até 100. Apresente os cálculos. | ||

:5. Quantos FF são necessários para gerar um sinal de onda quadrada com uma frequência de 24Hz a partir de um sinal original de 2,4GHz. | :5. Quantos FF são necessários para gerar um sinal de onda quadrada com uma frequência de 24Hz a partir de um sinal original de 2,4GHz. | ||

| − | :6. Quantos CI 74193 seriam necessários para mostrar uma contagem, em display de 7 segmentos, de 0 até 1000. | + | :6. Qual é o atraso de propagação de um contador síncrono? |

| − | : | + | :7. O que é um contador com carga paralela? |

| − | + | :8. Quantos CI 74193 seriam necessários para mostrar uma contagem, em display de 7 segmentos, de 0 até 1000. | |

| − | + | :9. Que frequência eu tenho no pino QD do CI 74193 sendo uma frequência de clock de 8kHz, numa configuração de contador crescente de 4 bits. | |

| + | :10. O que é um contador BCD? | ||

| − | == | + | ==Exercícios de contadores (PDF)== |

http://wiki.sj.ifsc.edu.br/images/1/11/EX2_DIG222802.pdf | http://wiki.sj.ifsc.edu.br/images/1/11/EX2_DIG222802.pdf | ||

Edição atual tal como às 14h21min de 30 de novembro de 2020

Lista de Exercícios para AT1

Parte 1

- 1. O que é um circuito digital Combinacional?

- 2. O que é um circuito digital Sequencial?

- 3. Qual a diferença entre um circuito Combinacional e um Sequencial?

- 4. O circuito Sequencial pode ser dividido em quantos grupos e quais são?

- 5. Qual a diferença entre Síncrono e Assíncrono?

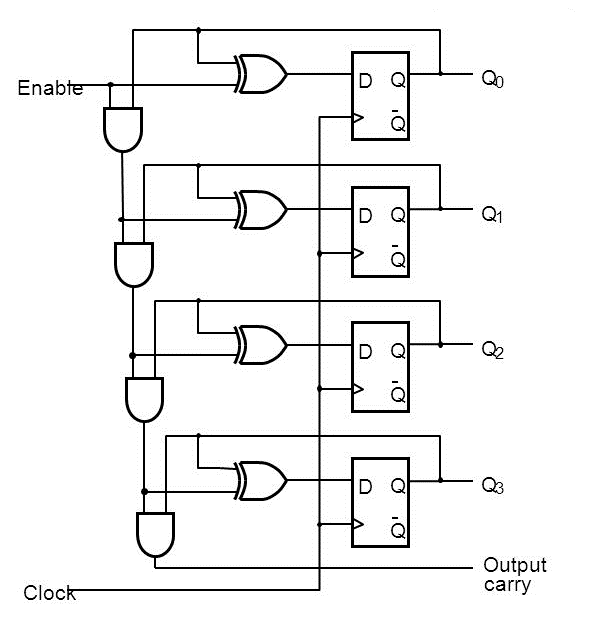

- 6. Observe a figura abaixo e faça o que se pede:

- a) Identifique o que é borda de subida e borda de descida.

- b) Identifique apenas um período do clock.

- c) Quanto pulsos de clock completos tem na figura?

- d) Se num osciloscópio a forma de onda completa aparecer numa escala de, 14s do início ao fim, qual é a frequência e o período deste clock?

- e) Na lógica TTL qual são os valores para nível lógico alto (1) e nível lógico baixo (0)?

- 7. Qual frequência de um sinal de relógio com 1ms de período?

- 8. Qual o período de um sinal de relógio com 100MHz?

- 9. O que são os Latches?

- 10. O RS é o Latch mais simples que existe e é mostrado na figura abaixo. Complete a tabela verdade abaixo considerando que inicialmente Q=0 e Q\=1.

R S Q Q\ 0 0 0 1 0 1 1 0 1 1

*Perceba que RS não estão barrados na tabela.

- 11. Complete a figura da questão anterior, transformando-a num Latch RS controlado.

- 12. Complete a tabela verdade abaixo para o RS Controlado de questão anterior considerando que inicialmente Q=Q e Q\=Q\.

C R S Q Q\ 0 X X Qa Qa\ 1 0 0 1 0 1 1 1 0 1 1 1

*Qa: saída do estado anterior.

- 13. Por quê surgiu o Latch tipo D?

- 14. Complete o diagrama abaixo transformando o Latch RS controlado em Latch tipo D. Em seguida, complete a tabela verdade mais abaixo.

D Q 0 1

- 15. Complete. Os _____________ são elementos de circuito que podem apresentar _______

- estados estáveis. A aplicação de sinal de ______________ pode alterar o estado de suas

- _________________. É possível considerar que o circuito é uma _________________ capaz

- de armazenar ______ bit.

- 16. Desenhe um circuito do flip-flop RS por borda de subida e outro por borda de descida.

- 17. Complete a forma de onda (Q e Q\) da figura abaixo, para um circuito de um flip-flop RS sensível a borda de subida do clock.

- 18. Complete a forma de onda (Q e Q\) da figura abaixo, para um circuito de um flip-flop RS com borda de descida do clock.

- 19. Como funciona o flip-flop tipo D?

- 20. Complete a forma de onda da figura abaixo, para um circuito do flip-flip tipo D com borda de subida do clock.

- 21. Complete. No _________________ J-K quando houver variação do _____________, o valor

- guardado no flip-flop será alternado se as entradas J e K forem iguais a ________ e será

- mantido se ambas forem iguais a ______. No caso de serem diferentes, então o valor se

- tornará ________ se a entrada J (Jump) for ________ e será __________ se a entrada K

- (Kill) for _________.

- 22. A figura abaixo mostra o símbolo utilizado para o flip-flop JK. Descreva todas as características apresentadas no diagrama.

21. Preencha a tabela verdade para o flip-flop JK.

J K Q Q\ 0 0 0 1 1 0 1 1

- 22. Transforme o flip-flop JK em tipo T.

- 23. Um circuito típico de um contador assíncrono construído com FF do tipo JK é mostrado na figura abaixo. Responda:

- a) Quantos bits têm esse contador?

- b) É possível contar de quanto até quanto em binário e em decimal?

- c) Por quê J e K são iguais a 1?

- d) Esse contador é crescente ou decrescente?

- e) Se for crescente, como transformar para decrescente?

- f) Se for decrescente, como transformar para crescente?

- g) Complete a forma de onda abaixo para o crescente:

- h) Complete a forma de onda abaixo para o decrescente:

- 24. Preencha nas figuras abaixo, o diagrama de estados de um contador crescente e de um contador decrescente em binário de 3 bits.

- 25. O que é um contador de módulo? Pra quê serve?

- 26. O que é o estado temporário ou não atingível de um contador de módulo?

- 27. Quantos flip-flops são necessários para contar de 0 a 99, ou seja, MOD-100?

- 28. A figura abaixo representa um contador de 4 bits, transforme ele em um contador MOD-10, ou seja, deve contar de 0 a 9.

29. Complete a forma de onda para o circuito da questão anterior.

30. O que são os atrasos de propagação dos contadores assíncronos e o quê isso implica?

Parte2

- 1. Complete o circuito abaixo para que funcione como contador assíncrono crescente.

- 2. Utilizando o mesmo circuito, faça as modificações necessárias para que funcione como contador assíncrono decrescente.

- 3. Explique o funcionamento do contador síncrono crescente visto da figura abaixo.

- 4. Quantos FF e portas lógicas eu preciso para fazer um contador síncrono que conte 0 até 100. Apresente os cálculos.

- 5. Quantos FF são necessários para gerar um sinal de onda quadrada com uma frequência de 24Hz a partir de um sinal original de 2,4GHz.

- 6. Qual é o atraso de propagação de um contador síncrono?

- 7. O que é um contador com carga paralela?

- 8. Quantos CI 74193 seriam necessários para mostrar uma contagem, em display de 7 segmentos, de 0 até 1000.

- 9. Que frequência eu tenho no pino QD do CI 74193 sendo uma frequência de clock de 8kHz, numa configuração de contador crescente de 4 bits.

- 10. O que é um contador BCD?

Exercícios de contadores (PDF)

http://wiki.sj.ifsc.edu.br/images/1/11/EX2_DIG222802.pdf