DI2022802 2020 1 AULA03

Laboratório 1

O primeiro experimento da turma de Digital 2 da Engenharia vai ser realizado na LabMIC (sala 104) no dia 02/03 entre 13h30min e 17h30min. O experimento está dividido em duas etapas, sendo que na primeira parte vocês vão testar o funcionamento de um Latch RS controlado feito a partir das portas lógicas AND (E) e NOR (NOU) comprovando a tabela verdade. Na segunda etapa vocês vão testar o funcionamento dos flip-flops tipo D na configuração mestre-escravo, comprovando a teoria envolvida.

Atenção!

No horário das 13h30min às 15h20min primeira turma conforme lista passada em sala de aula.

No horário das 15h40min às 17h30min segunda turma conforme lista passada em sala de aula.

Parte I - Latch RS

- Objetivo

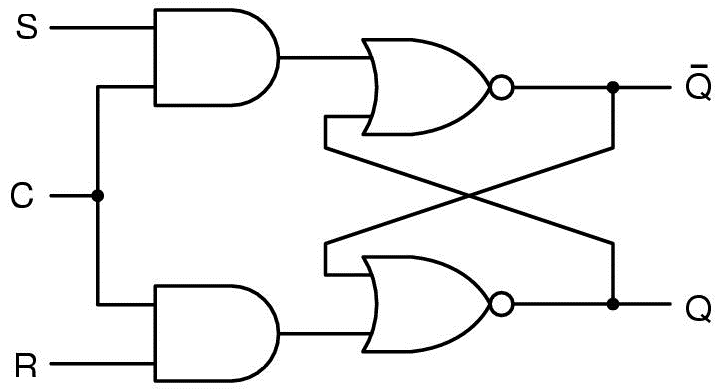

Testar o funcionamento de um circuito latch RS controlado, feito a partir das portas lógicas AND (E) e NOR (NOU) como mostra a Figura 1.

Figura 1 - Latch RS controlado.

| C | R | S | Q |

|---|---|---|---|

| 0 | X | X | Qa |

| 1 | 0 | 0 | Qa |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | proibido |

[*]Qa: saída do estado anterior.

Procedimento

- Formar até 10 equipes com 2 alunos;

- Desenhar as ligações utilizando o esquemático dos CIs;

- Montar o circuito na banca digital, os CIs devem ficar com o chanfro voltado para cima;

- Fazer a ligação de VCC e GND;

- Fazer a ligação entre as portas lógicas dos circuitos integrados;

- Fazer a ligação de R, S e C com chaves seletoras;

- Fazer a ligação das Saídas Q e Q\ aos LEDs;

- Testar a tabela verdade.

Parte II - Mestre-escravo

- Objetivo

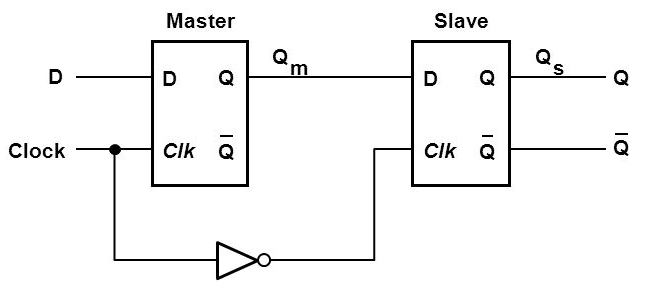

- Testar o funcionamento de um Flip-flop D na configuração mestre–escravo a partir do CI 7474 e uma porta inversora. O circuito a ser montado pode ser visto na Figura 2.

Figura 2 - Flip-flop tipo D na configuração mestre–escravo.

| D | Q | Q\ |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 1 | 0 |

Procedimento

- Mesmas equipes;

- Desenhar as ligações utilizando o esquemático dos CIs;

- Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima;

- Fazer a ligação de VCC e GND

- Fazer a ligação de PRE e CLR nas chaves seletoras.

- Fazer a ligação entre as FF passando pela inversora

- Fazer a ligação de D e Clock com chaves seletoras

- Fazer a ligação das Saídas Qm e Qs aos LEDs

- Construir a tabela verdade para Qm e Qs a partir da simulação dos pulsos de clock (ligar e desligar a chave).

- Ligar o clock a uma frequência de 1Hz (se estiver disponível) e ver o que acontece.

Material Utilizado

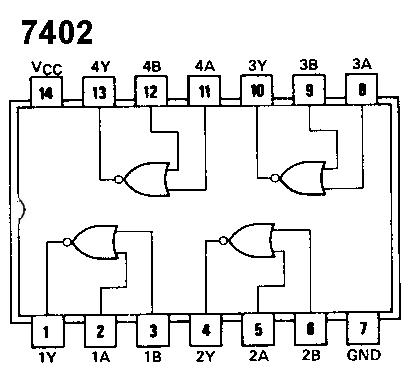

- CI 7402 (NOR) (Figura 3)

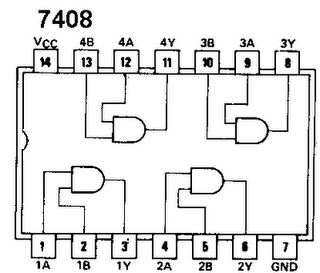

- CI 7408 (AND) (Figura 4)

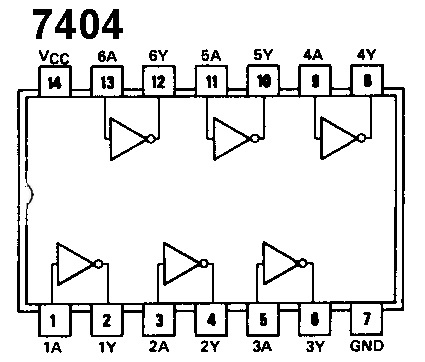

- CI 7404 (INV) (Figura 5)

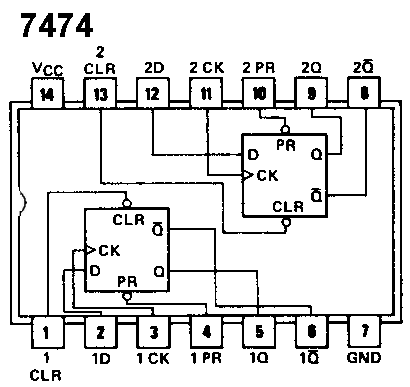

- CI 7474 (FF tipo D) (Figura 6)

- fios diversos

- bancada digital

- alicates

Esquemáticos dos CIs

Figura 3 - Esquemático do CI 7402 - Portas NOR.

Figura 4 - Esquemático do CI 7408 - Portas AND.

Figura 5 - Esquemático do CI 7404 - Portas Inversoras.

Figura 6 - Esquemático do CI 7474 - Dois FF tipo D.

Relatório

O relatório deverá ser entregue, pela turma 1 até 13h30min, e pela turma dois até 19h. As equipes que não terminaram as duas partes do experimento, podem fazer o relatório da parte 1 e relatar o que aconteceu com a parte 2.

- Critérios avaliativos

- Prática (montagem/equipe): 4

- Circuito completo (todos): 2

- Resultados e discussões : 4

- Resultado: 10