Conversor Analógico Digital - Rampa Dupla

Principio de Funcionamento

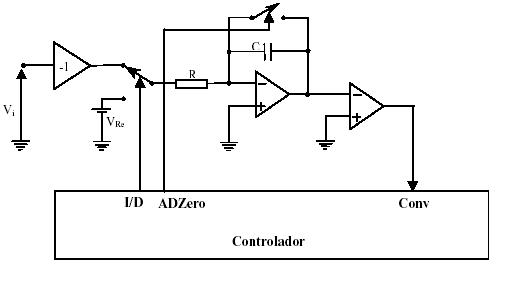

O sinal analógico de entrada Vi é unipolar positivo, writing jobspodendo variar de 0 Volts até um valor máximo igual ao valor da fonte de referência VRef. A fonte de referencia também é positiva. O sinal de entrada passa por um buffer inversor, fazendo com que o circuito veja Vi negativo, com polaridade oposta a VRef, ao mesmo tempo que provê alta impedância para o sinal a ser convertido. Quando a chave de entrada, eletronicamente controlada, está na posição do sinal a ser medido (convertido), a saída do integrador apresenta uma rampa ascendente, e este intervalo de tempo é chamado integração. Quando a chave é mudada para a posição VRef (que é positiva), a saída do integrador apresenta rampa descendente, e este intervalo de tempo é chamado deintegração. Quando a chave é mudada para a posição VRef (que é positiva), a saída do integrador apresenta rampa descendente, e este intervalo de tempo é chamado deintegração. A inclinação da rampa, em ambos os casos, depende dos valores de R e C (constantes), e da tensão aplicada na entrada do integrador (Vi , que pode variar, e VRef , que é constante). Após receber a solicitação para iniciar uma nova conversão, o controlador digital abre a chave de zeramento (ADZero = “0”), ao mesmo tempo que posiciona a chave eletrônica de entrada (integração/deintegração) na posição Vi, correspondente ao nível “1” do sinal de controle I/D* (Integração/Deintegração). O controlador conta um intervalo de tempo fixo, correspondendo ao tempo de integração, que é o tempo para o contador atingir seu máximo valor (no clock seguinte voltará a zero). Atingido este tempo fixo, a chave é mudada para a posição VRef (I/D* = “0”), começando o tempo de deintegração, a partir do qual o controlador inicia (desde zero) uma nova contagem crescente. Imediatamente, o controlador passa a monitorar o sinal de saída do comparador (Conv), cuja saída é TTL compatível, e o controlador continua contando até que Conv transite para o nível alto (indicando que a saída em rampa descendente do integrador cruzou o zero). O valor da contagem é diretamente proporcional, em forma digital, ao valor da tensão de entrada.

Características

- É um conversor lento com alta resolução (1ms 20 bit)

- Composto por integrador de Miller, comparador de tensão, contador e

lógica de controlo

- Durante tempo fixo t1 integra-se VA (1ªrampa)

- Determina-se o tempo t2 que leva a repor o integrador a 0 (2ªrampa)

- Comparador pára contador

- Conversor insensível à tolerância de R e de C e à frequência

do relógio esuas variações

- Na prática utilizam-se + 2 rampas, uma para inicializar o

condensador e outra para armazenar erros de desvio dos amp. ops.

- Esse conversor é baseado na mesma topologia do conversor de rampa simples, ele permite eliminar a depedência da conversão com a frequência de clock e com o capacitor de integração.

- Esse conversor é muito popular pelos seus baixo offset e erro de ganho,e elevada linearidade.

- Exige circuito de baixa complexidade.

- É vocacionado para sinais bastante lentos sendo adequado para aparelhos de medida (corrente e tensão).

- É de baixo custos, boa resolução, baixa taxa de conversão.

- Os erros de offset podem ser compensados recorrendo-se a um conversor de quadrupa rampa.Uma conversão faz-se com Vin=0 (amostrar o offset).A segunda conversão corresponde a Vin. O valor final será este subtráido do primeiro.

- Esses conversores de rampa dupla como ja foi citado sao muitos lentos.No pior casos Tt=T1 / T1=T2=2n+1 TCK.

Exemplo (1) de Circuitos de Conversores Rampa-Dupla

* Funcionamento:

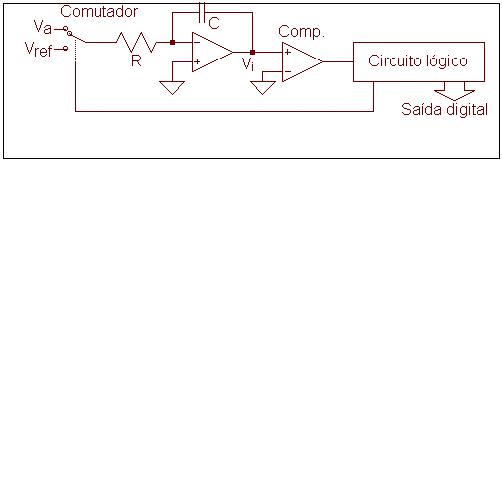

- Os conversor A/D de integração usam um integrador para converter o valor da tensão a converter num intervalo de tempo, que é medido com simples técnicas digitais. Existem vários circuitos que usam integradores, uns mais simples mas com mais erros, outros mais complexos, como o de quádrupla rampa, que reduz ainda mais alguns erros que o de dupla rampa.

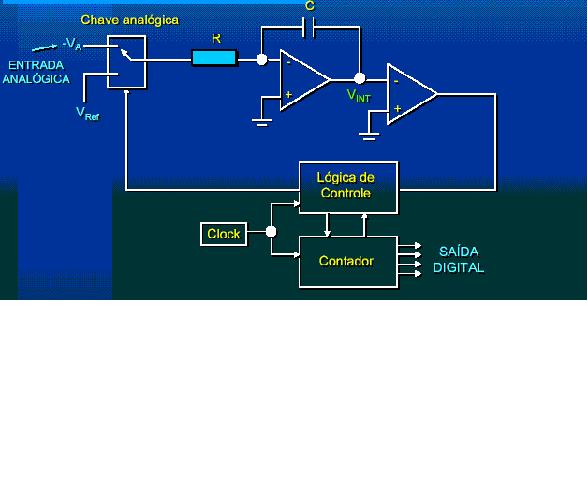

- O circuito da figura é um esquema simplificado de um conversor A/D de dupla rampa.

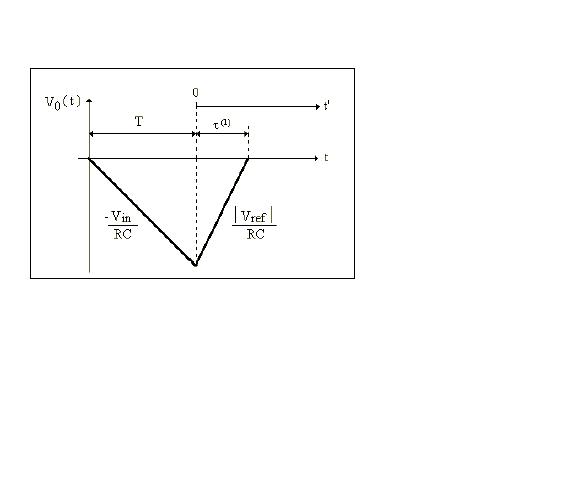

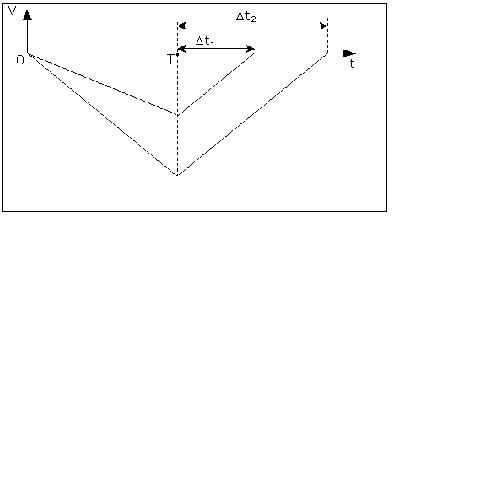

- O comutador electrónico à esquerda selecciona alternadamente a tensão de entrada Va e uma tensão de referência Vref sob controlo do circuito lógico à direita. Este circuito lógico contém um contador de n bits. No início da conversão, o contador de n bits está a zero, e o condensador C está descarregado. A tensão de saída do integrador Vi é zero. O comutador está ligado à tensão analógica de entrada Va, que vamos supor constante e positiva. A partir deste instante inicial, a tensão Vi vai crescer negativamente, com um declive constante, como indica o gráfico abaixo, enquanto o contador conta os impulso do relógio do sistema.

- Quando o contador chegar ao valor da máxima contagem, ao fim do tempo T=2n.Trel, em que Trel é o período do relógio do sistema, o comutador selecciona a tensão de referência Vref. Esta tem um valor de sinal oposto ao da tensão de entrada, pelo que a tensão de saída do integrador é uma rampa, com uma inclinação positiva. Quando a tensão de saída do integrador atinge o valor zero, a saída do comparador muda de estado e sinaliza ao circuito lógico que para o contador. O valor do contador é uma medida do tempo desta segunda integração, Δt1=NTrel, em que N é o valor do contador. Se a tensão de entrada for maior, a derivada da tensão Vi durante a primeira integração seria maior e o tempo da segunda integração seria por exemplo Δt2, como representado no gráfico.

- Sendo Va constante, a corrente de carregamento do condensador C é Va/R e a carga acumulada em C ao fim do tempo T é VaT/R. Esta carga será removida durante a segunda fase da integração, em que a corrente é (-Vref)/R, e a carga é removida durante o tempo Δt1.A igualdade das cargas é então:

- O valor de é então dado por:

- O intervalo de tempo Δt1 é medido pelo contador. Como este tem uma resolução de n bits, o valor da contagem N do contador quando este é parado ao fim da segunda integração é:

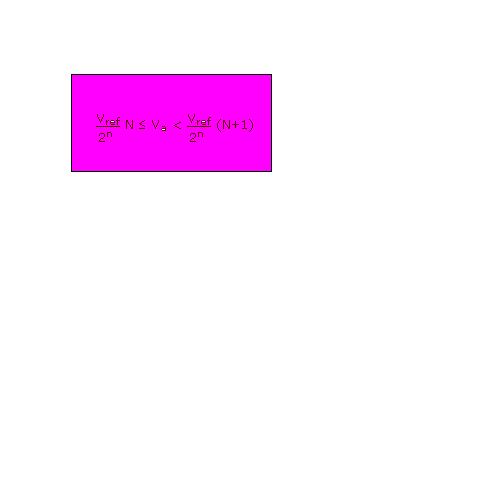

- Nesta equação, o operador Int extrai o maior inteiro presente na quantidade entre os parênteses rectos. Ou seja, quando o contador é parado, o valor da contagem é o maior número de ciclos do relógio completos que cabem no intervalo Δt1. Podemos exprimir isto de outra maneira dizendo que (N.Trel) ≤ Δt1 < (N+1)Trel. Substituindo na equação para Va acima, e fazendo T=2nTrel, obtém-se o intervalo de quantização no qual está localizado o valor da tensão analógica a converter:

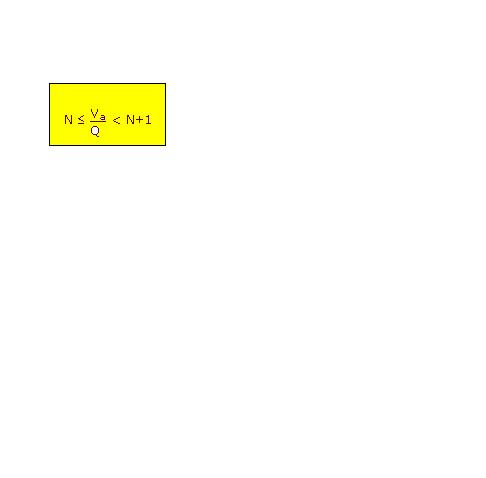

- Como o quociente Vref/2n é o quantum Q, podemos concluir que o resultado N da conversão é tal que:

- Isto é equivalente a escrever que N = Int [Va/Q]. Note-se que a característica de conversão resultante não é exactamente idêntica à característica teórica, uma vez que a primeira transição, da contagem N=0 para a contagem N=1, se dá quando Va=Q, e todas as outras transições entre contagens depois em múltiplos inteiros de Q. Teoricamente a primeira transição deveria ser para Va=Q/2, e as seguintes para múltiplos ímpares de Q/2, ou seja deveria ser N = Int [(Va/Q)+0,5]. Para se obter a característica teórica tem que começar a conversão desfasada meio período de relógio da contagem.

Vantagens do Circuito (1) Conversor Rampa-Dupla

- Uma das vantagens deste conversor é o não necessitar que a tensão de entrada seja fixada durante a conversão. O facto de a tensão de entrada ser integrada contribui mesmo para diminuir a influência de ruído sobreposto à tensão que se deseja converter. O ruído que tenha um período que seja um sub-múltiplo do valor do intervalo de integração T é mesmo totalmente eliminado, pelo que o valor de T é geralmente escolhido de modo a eliminar ruído à frequência da rede de distribuição de energia. Por exemplo, fazendo T=100ms, consegue-se eliminar ruído a 50/60 Hz, que é a frequência a rede.

Exemplo (2) de Circuitos de Conversores de Rampa-Dupla

Vantagens do Circuito (2) Conversor Rampa-Dupla

- Precisão dependente de Vref.

- Esse circuito é capaz de operar com 12 Bits (3 digitos BCD).

- Ele tem rejeição ao ruido.

Desvantagens desse Circuito é:

- Tempo de conversão ainda muito grande (-10ms) ou mais.

- Aplicações principais:

- multimetros digitais e outros medidores comerciais.

Exemplo (3) de Conversor Rampa-Dupla

*CONVERSOR A/D RAMPA DUPLA TIPO INTEGRADOR.

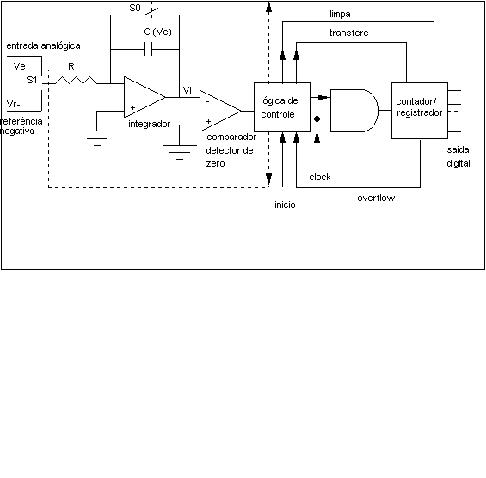

- No início a chave S0 é ativada para descarregar o capacitor e a chave S1 está na posição para ler a entrada analógica (Ve), que por sua vez, é cone ctada a entrada inversora do integrador por um intervalo de tempo fixo (T1), determinado pelo tempo necessário para o contador ser totalmente preenchido por 1's. Durante este intervalo o capacitor é carregado e o integrad or produz uma rampa linear decrescente em sua saída.

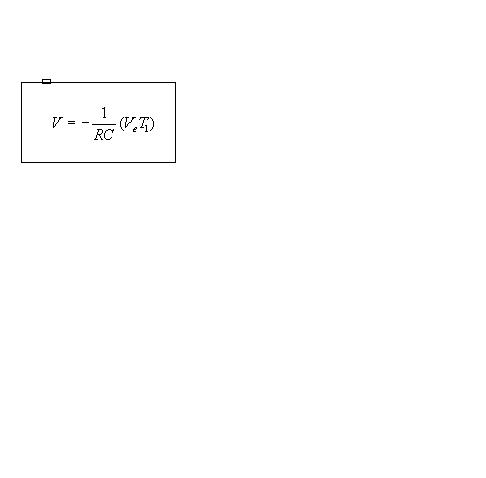

A voltagem final da rampa é da por:

ou, assumindo uma entrada constante:

- Imediatamente após a última contagem (final de T1), o contador é zerado e gera um pulso de "overflow". A lógica de controle recebendo este sinal, paralisa a contagem e muda a chave S1 para que o integrador receba em sua entrada inversora uma voltagem de referência negativa fixa.

O integrador reage à entrada, descarregando o capacitor, e fornecendo uma rampa linear crescente em sua saída, durante um intervalo de tempo T2. Durante T2, os pulsos do relógio são contados, produzindo um total proporcional a voltagem analógica apresentada na entrada do circuito. Ao final de T2 a voltagem da rampa é zero. Neste ponto ainda, o comparador detector de zero, ativa a lógica de controle que por sua vez, encerra a conversão e Ao final de T2 a voltagem da rampa é zero. Neste ponto ainda, o comparador detector de zero, ativa a lógica de controle que por sua vez, encerra a conversão e avisa o bloco contador para transfer ir a contagem para um registrador de saída, podendo começar um novo ciclo de medida. A voltagem na saída do integrador sendo zero e igual a V, T2 pode ser calculado como:

- Note que a relação entre T2 e Ve , é influenciada apenas por Vref e T1.

Um exemplo Conversor A/D rampa dupla tipo integrador segue abaixo.

- Gráfico da saída do integrador:

- Os dispositivos conversores comerciais são providos de uma maior sofisticação que o apresentado neste texto. A maioria deles são projetados para operação bipolar, detectando e indicando digitalm ente a polaridade da entrada. Quando uma entrada analógica negativa é detectada, a polaridade da voltagem de referência, a saída do comparador e a polaridade da linha de saída são invertidas. Possuem também uma circuitaria mais sofisticada no caso do zeramento automático.

- A taxa de conversão depende diretamente da velocidade de oscilação do relógio ("clock") e da resolução desejada. Uma velocidade normal seria de uma conversão completa por segundo. Um acr& eacute;scimo na resolução requer simplesmente que o contador e o "latch" sejam acrescidos em seu módulo.

- A técnica utilizada por este conversor possibilita maior imunidade a ruídos e também a minimização dos erros.

Outro Exemplo de Conversor Rampa-Dupla

- Esse conversor é baseado na mesma topologia do conversor de rampa simples, com uma lógica adicional.

- Ele permite eliminar a dependência da conversão com a freqüência de clock e com o capacitor de integração. Circuito típico:

Obs: Vi deve sempre ter polaridade contrária à Vref.

- Esse é o tipo de conversor usado em multímetros digitais e instrumentos de medida de baixa com velocidade e alta resolução (12 à 22 bits).

*Funcionamento:

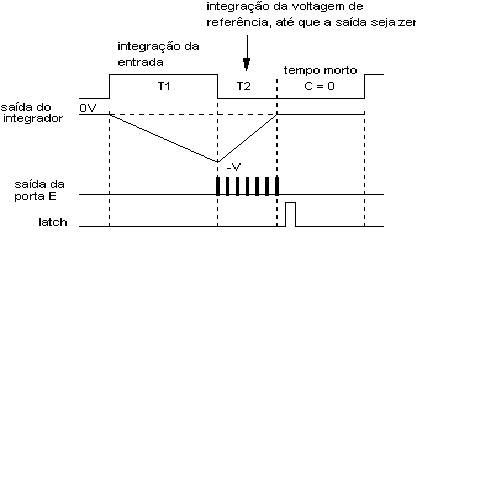

1) No início de cada etapa é efetuado um reset do contador e do capacitor de integração (T0).

2) O sinal de entrada Vi é integrado por um número fixo de contagens (T1);

3) Em seguida a tensão de referência Vref é integrada até que Vo = 0 (T2);

4) O número de contagens efetuadas durante o tempoT2 é proporcional à Vi;

5) O valor digital é obtido diretamente da saída do contador binário;

Graficamente:

Tempo total de conversão: T = T0 + T1

*Características gerais:

- Idênticas às do conversor de rampa simples com as vantagens de fornecer um valor digital

independente de freqüência de clock (para pequenos intervalos de tempo – em que não varie a temperatura, por exemplo) e da constante de integração RC. É o tipo de conversor usado em multímetros digitais e instrumentos de medida de baixa.

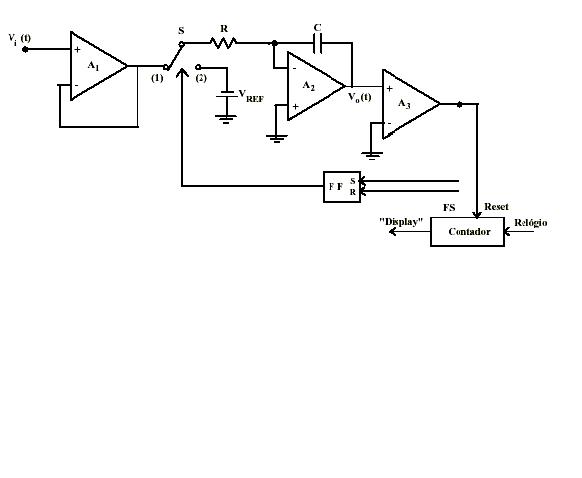

- Circuito de Conversor de dupla rampa na figura abaixo;

- Descrição do circuito acima;

A1 - Seguidor de tensão (“buffer”)

A2 - Integrador

A3 - Comparador ( Tensão de referência = 0 V ) Tem Comutador S na posição (1)

Condensador C descarregado vc(0) = 0

Contador a zero “Display” bloqueado

- Durante esta fase o contador é incrementado por cada impulso de relógio e quando atinge o limite de contagem - NFS= 2n envia um impulso que coloca o comutador S na posição (2).

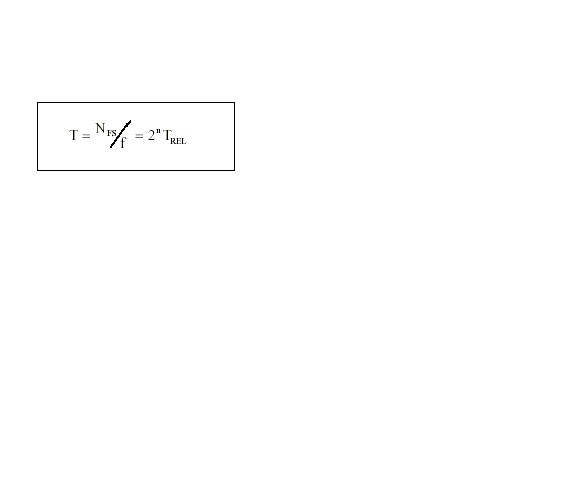

O tempo de integração de VIN é fixo e vale:

n - Número de “bits” do contador

TREL - Período do sinal de relógio

com o comutador na posição (2) e admitindo que VIN e VREF têm polaridades opostas. Quando atinge a tensão nula o comparador, o conteúdo do contador - N é transferido para o “display”, faz-se o “reset” do contador e inicia-se novo ciclo de integração da tensão de entrada colocando S na posição (1).

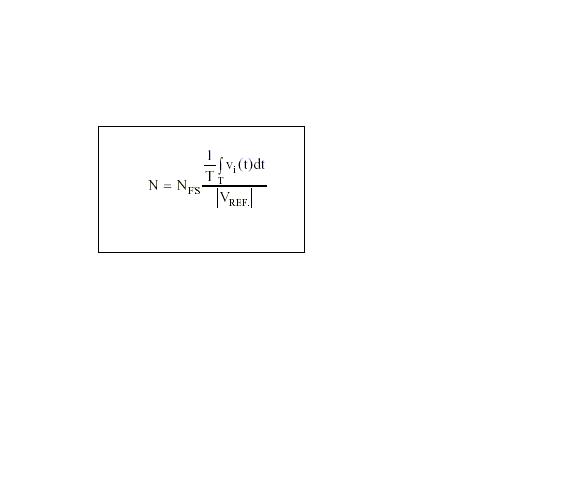

- Determinação do valor de N - contagem transferida para o “display” no instante.

t = T + ô (t’ = ô): O resultado não é alterado se vi (t) for variável no intervalo de tempo de integração desde que o seu valor médio seja VIN, ou seja:

- Por estes motivos a precisão da medida depende apenas da precisão da

tensão de referência. Este método elimina todas as tensões parasitas que se sobrepõem ao sinal vi(t) desde que o seu valor médio durante o período T seja nulo. Devemos para o efeito utilizar um período T que seja múltiplo do período do ruído que se pretende anular. É usual utilizar valores de T múltiplos de 20 (ms) uma vez que deste modo se elimina o ruído parasita proveniente dos 50 Hz da rede de distribuição. A *

*Desvantagem desse circuito;

- A desvantagem principal que se pode referir neste método é o elevado tempo de conversão.

Valores típicos :

Precisão - 10-4....10-6

Ritmo - 10 … 30 S/s

![{\displaystyle N=Int\left[{\frac {\Delta t_{1}}{T_{ref}}}\right]}](https://en.wikipedia.org/api/rest_v1/media/math/render/svg/146708442601fa2d8b16f384e12f7ef1f28b7de0)