Mudanças entre as edições de "Contador binário síncrono"

Ir para navegação

Ir para pesquisar

| (43 revisões intermediárias por 3 usuários não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

;Objetivos: | ;Objetivos: | ||

| − | * Inserir o circuito comercial de um Contador síncrono crescente/ | + | * Inserir o circuito comercial de um Contador síncrono crescente/decrescente; |

* Inserir o circuito comercial de um decodificadores de 7 segmentos; | * Inserir o circuito comercial de um decodificadores de 7 segmentos; | ||

* Testar os circuitos e gerar blocos para ser utilizado em um sistema maior; | * Testar os circuitos e gerar blocos para ser utilizado em um sistema maior; | ||

| Linha 6: | Linha 6: | ||

;Materiais necessários: | ;Materiais necessários: | ||

| − | #CI [http://www.ti.com/lit/ds/symlink/sn74als191a.pdf 74X191 Contador binário síncrono](disponível na biblioteca da ALTERA) | + | # CI [http://www.ti.com/lit/ds/symlink/sn74als191a.pdf 74X191 Contador binário síncrono](disponível na biblioteca da ALTERA) |

| − | #CI [http://www.ti.com/lit/ds/symlink/sn7447a.pdf 74X47/48 Decod 7-seg](disponível na biblioteca da ALTERA) | + | # CI [http://www.ti.com/lit/ds/symlink/sn7447a.pdf 74X47/48 Decod 7-seg](disponível na biblioteca da ALTERA) |

| − | #Computador com software Quartus II da Altera. | + | # Computador com software Quartus II da Altera. |

| − | #Kit DE2-115 - [[Interfaces_de_entrada_e_saída_da_DE2-115 | Cyclone: EP1C3T100A8]] ou Mercurio IV - [[Pinagem_dos_dispositivos_de_entrada_e_saída_do_kit_MERCURIO_IV | Cyclone IV: EP4CE30F23C7]]; | + | # Kit DE2-115 - [[Interfaces_de_entrada_e_saída_da_DE2-115 | Cyclone: EP1C3T100A8]] ou Mercurio IV - [[Pinagem_dos_dispositivos_de_entrada_e_saída_do_kit_MERCURIO_IV | Cyclone IV: EP4CE30F23C7]]; |

==Teste do módulo contador binário síncrono== | ==Teste do módulo contador binário síncrono== | ||

| − | |||

| − | |||

| − | |||

| − | [[Imagem:CI74191_diag.png|900px]] | + | #Abra o Quartus II e crie um novo projeto com nome '''ContUpDown''' na pasta '''/home/aluno/Contador''', utilizando a família family='''Cyclone IV E''' com o dispositivo device='''EP4CE115F29C7''' (placa grande) ou '''Family = Cyclone IV E''' com dispositivo '''device = EP4CE30F23C7''' (Placa pequena). |

| − | + | #Crie um novo diagrama esquemático ('''File >> New >> Block Diagram/Schematic File'''). | |

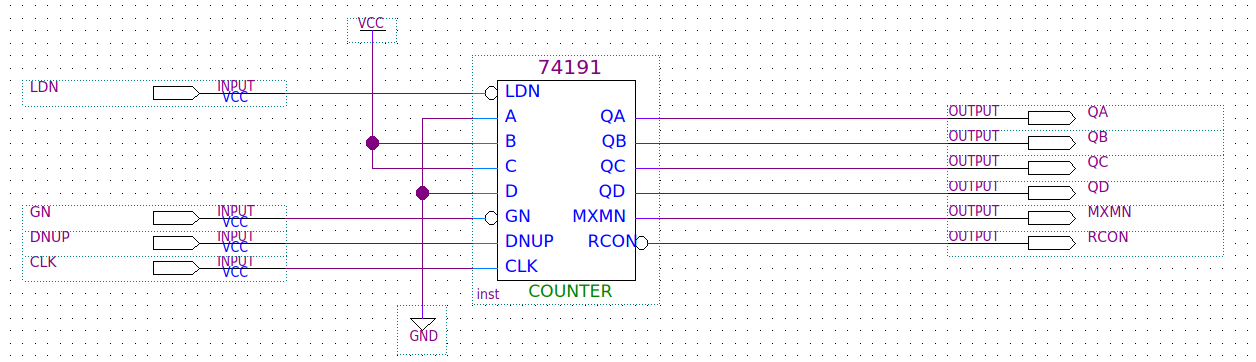

| − | + | #Insira o diagrama esquemático de um Contador binário síncrono com 4 bits, conforme a figura abaixo.[[Imagem:CI74191_diag.png|900px]] | |

| − | + | #Após isso faça a Análise e Síntese do projeto: '''Processing >> Start Compilation'''. | |

| − | + | #Abra o editor de forma de onda do simulador QSIM ('''File > New > University Programa VWF''') (v 13.0 e 13.1). | |

| − | + | #Defina o tempo de simulação ('''Edit > Set End Time ...''') = 1000 ns. | |

| − | + | #Importe todos os nós de lista do projeto ('''Edit > Insert > Insert Node or Bus''') > [Node Finder] > [List] > [>>] > [OK] > [OK]. | |

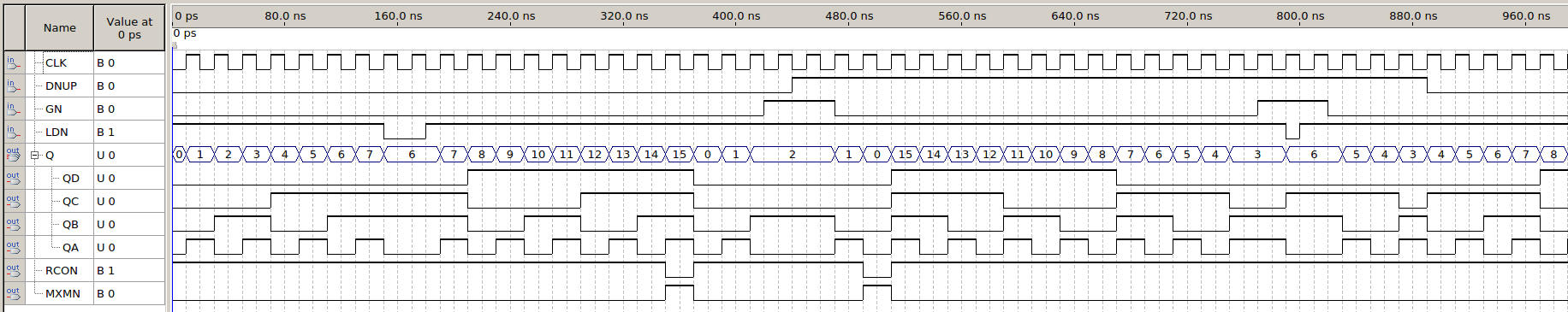

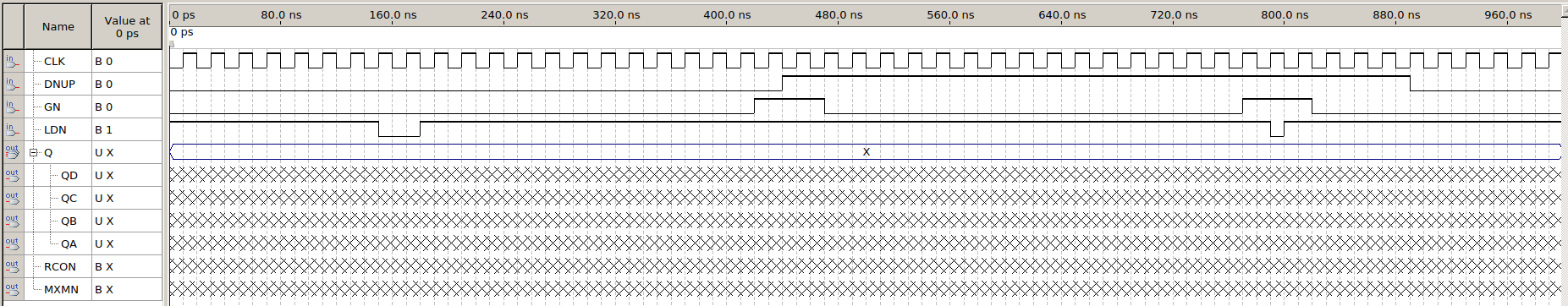

| − | + | #Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome tb_CI74191.vwf.[[Imagem:tb_CI74191.png|900px]] | |

| − | [[Imagem:tb_CI74191.png|900px]] | + | #Indique que o QSIM será usado na simulação ('''Simulation > Options > (x) Quartus II Simulator''') > [OK] > [OK] (v. 13.0) |

| − | + | #Faça a simulação funcional do circuito lógico usando o sinal criado ('''Simulation > Run Functional Simulation''') | |

| − | + | #O resultado da simulação deve corresponder a um contador. | |

| − | + | #Note que os bits das saídas estão agrupados e definidos como RADIX = "Decimal sem sinal". Para isso selecione os sinais ['''Edit > Grouping'''] ['''Group name = OUT'''] > ['''Radix = Unsigned Decimal'''] > [OK]. | |

| − | + | #Verifique se o resultado obtido corresponde a respostas do circuito implementado. | |

| − | |||

| − | |||

| − | |||

| − | |||

[[Imagem:Rtb_CI74191.png|900px]] | [[Imagem:Rtb_CI74191.png|900px]] | ||

;QUESTIONÁRIO: | ;QUESTIONÁRIO: | ||

| − | *O que é necessário para fazer o contador fazer uma contagem descendente | + | * O que é necessário para fazer o contador fazer uma contagem descendente? |

| − | + | * Como fazer para parar a contagem por um tempo mantendo o sinal de ''clock'' ligado? | |

| − | |||

| − | *Como fazer para parar a contagem por um tempo mantendo o sinal de ''clock'' ligado? | ||

==Teste do módulo decodificar de 7 segmentos== | ==Teste do módulo decodificar de 7 segmentos== | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

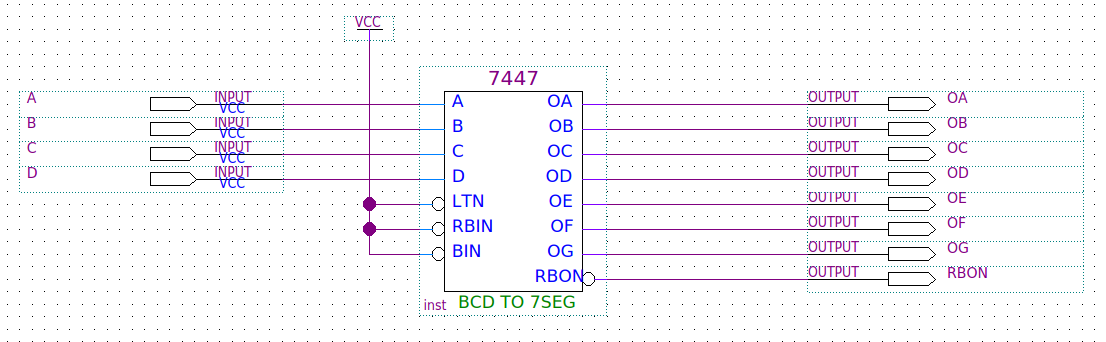

| − | + | #Crie um novo diagrama esquemático ('''File >> New >> Block Diagram/Schematic File''') no mesmo projeto para inserir o diagrama esquemático de um decodificar de 7 segmentos para display de anodo comum, conforme a figura abaixo. <span style="color: red;">Para a FPGA grande (DE2-115) utilize o conversor '''7447''', conforme figura abaixo, e para a FPGA pequena (Macnica), que possui display Catodo Comum, deve-se utilizar o '''7448'''. Ambos os componentes apresentam a mesma pinagem.</span>[[Imagem:CI7447_diag.png|900px]] | |

| − | + | #Após salvar o arquivo como '''ConvBcdSsd.bdf''' na mesma pasta Contador. Mude o '''Top-Level Entity''' para este novo esquemático. Após isso faça a Análise e Síntese do projeto. | |

| − | [[ | ||

| − | + | <span id="[[Imagem:tb_CI7447.png|900px]]" class="mw-image" title="[[Imagem:tb_CI7447.png|900px]]" data-mw-type="image" data-mw-id="104956" data-mw-src="Imagem:tb_CI7447.png" data-mw-link="false" data-mw-sizewidth="900" data-mw-sizeheight="false" data-mw-wikitext="%5B%5BImagem:tb_CI7447.png%7C900px%5D%5D" draggable="true" contenteditable="false"></span> | |

| − | |||

| − | |||

| − | |||

==Criação do sistema completo com os módulos testados== | ==Criação do sistema completo com os módulos testados== | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | [[Imagem:Contador0- | + | #Selecione o diagrama esquemático do ContUpDown.bdf e crie um simbolo para este diagrama ['''File > Create/Update > Create Symbol File for Current File'''], [Save], [OK]. |

| + | #Repita o procedimento para o ConvBcdSsd.bdf. | ||

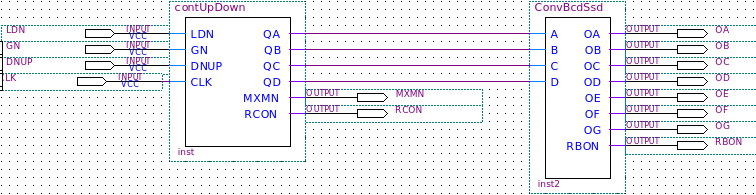

| + | #Crie um novo diagrama esquemático com nome '''/home/aluno/Contador/ContCompleto''' ('''File >> New >> Block Diagram/Schematic File'''), no mesmo projeto para inserir o diagrama esquemático do sistema que será composto dos dois módulos, conforme a figura abaixo. Mude o '''Top-Level Entity''' para este novo esquemático. [[Imagem:Contador0-15_diagv2.png|900px]] | ||

==Preparar o circuito lógico para gravação em um kit de desenvolvimento== | ==Preparar o circuito lógico para gravação em um kit de desenvolvimento== | ||

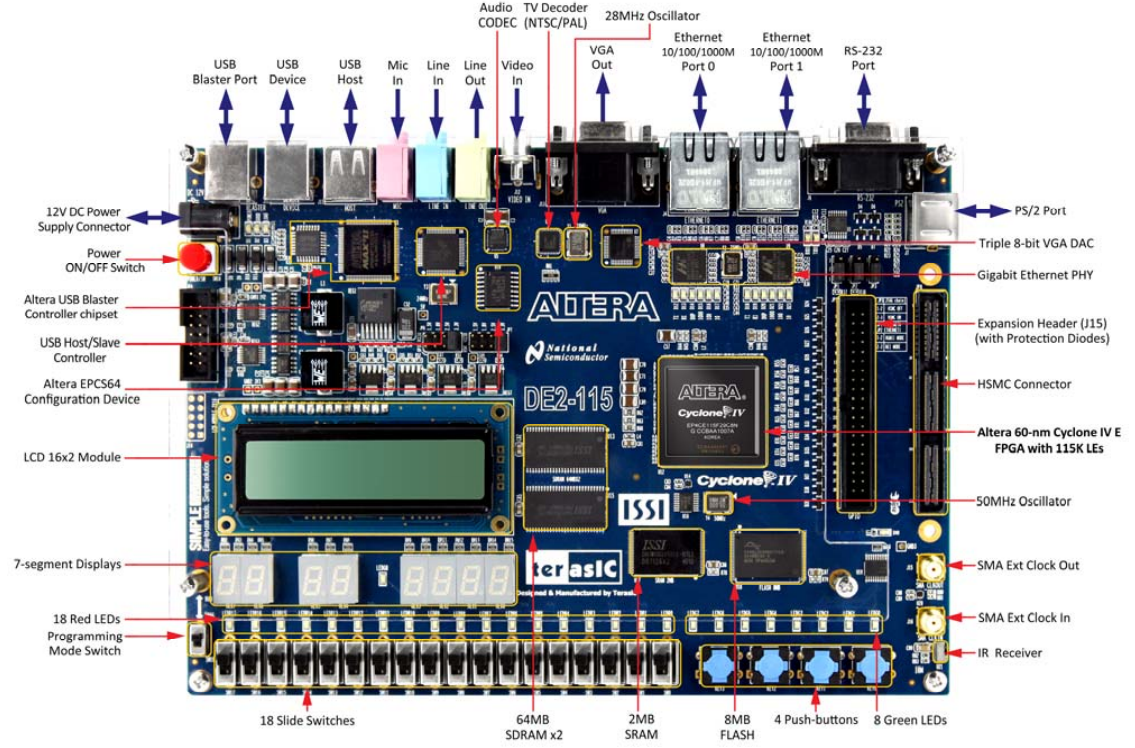

Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit '''DE2-115''' ou '''Mercurio IV'''. [[Arquivo:KitDE2-115.png|200px|right|Clique para Ampliar]] | Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit '''DE2-115''' ou '''Mercurio IV'''. [[Arquivo:KitDE2-115.png|200px|right|Clique para Ampliar]] | ||

| − | + | # Confira a família e dispositivo a ser usado (Assignments > Devices), utilizando a família family='''Cyclone IV E''' com o dispositivo device='''EP4CE115F29C7''' (Placa grande) ou '''device = EP4CE30F23C7''' (Placa pequena), e faça uma nova '''Análise e Síntese''' para que a nova pinagem do FPGA seja reconhecida pelo Quartus. | |

| − | + | # Atribua os pinos do circuito aos pinos do FPGA utilizando o '''Pin Planner''' ['''Assignments > Pin Planner''']. | |

| − | + | # Para descobrir a pinagem do FPGA e sua associação com os componentes do kit consulte o [ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE2-115/DE2_115.qsf Manual da DE2-115]/[[Interfaces de entrada e saída da DE2-115]] ou [[Pinagem_dos_dispositivos_de_entrada_e_saída_do_kit_MERCURIO_IV]]. | |

| − | + | # Para facilitar a configuração dos pinos, '''Assignments >> pin Planner''': | |

| − | + | ## Utilize o display de sete segmentos para mostrar a saída do decodificador de 7 segmentos, fazendo as devidas conexões. | |

| − | + | ## Utilize uma chave de contato momentâneo (''push button'') para gerar o sinal de CLK. | |

| − | + | ## Utilize a chave deslizante SW[0] para o sinal DN/UP, SW[1] para o sinal G', SW[2] para o sinal LD'. | |

| − | + | ## Utilize leds para mostrar o estado dos sinais MXMN, RBO' e RCO'. Pode ser os leds RGB. | |

| − | + | # '''Compile''' o projeto. Note que agora a numeração dos pinos também aparece no diagrama esquemático. | |

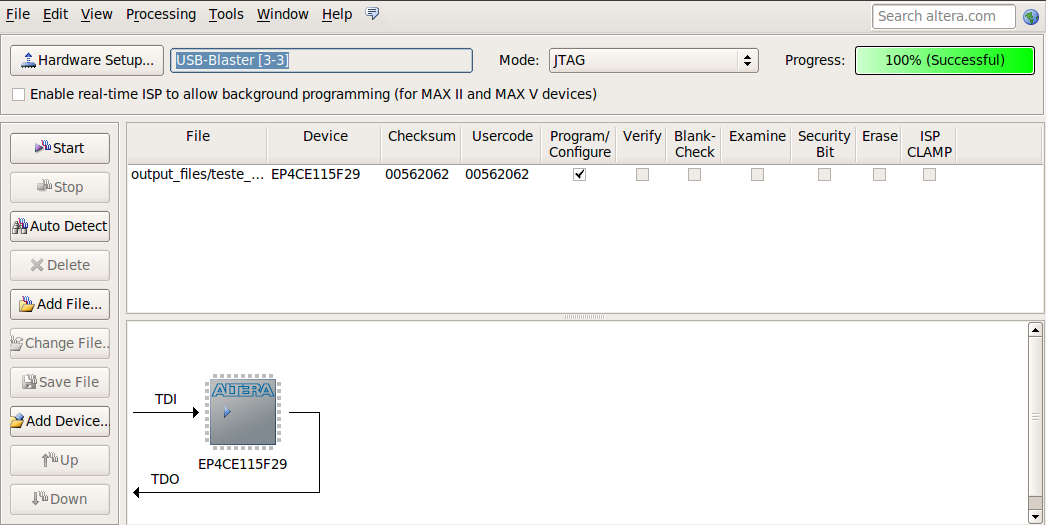

| − | + | # Use a porta USB-Blaster para fazer a programação na placa DE2-115 ou MERCURIO IV; | |

| − | + | # No Quartus vá em ('''Tools > Programmer''') para abrir a página de programação; | |

| − | + | ## Selecione o Hardware ('''Hardware Setup > USB-Blaster'''); | |

| − | + | ## Utilize o modo JTAG e clique em Start para começar a programação;[[Arquivo:Programador.png|200px|thumb|Clique para Ampliar]] | |

| − | + | # Configure as chaves e verifique o funcionamento do circuito. <span style="color: rgb(0, 128, 0);" data-mce-style="color: #008000;">Provavelmente você perceberá que a cada toque na chave associada ao clock ocorrerão vários saltos no contador, isso é provocado pelos repiques na chave.</span> | |

| − | + | # Normalmente uma chave apresenta os denominados repiques de sinal, ou seja, ao se alterar o estado da chave o sinal elétrico oscila várias vezes entre um nível lógico e outro, antes de estabilizar. Para evitar esse fenômeno pode-se fazer uso de um ''deboucer'' que gera um atraso entre os estados. Para usar o ''deboucer'' siga os seguintes passos: | |

| − | + | ## Tools > IP Catalog > Library > Basic Function > Arithmetic > LPM_COUNTER | |

| − | + | ## IP Variation file name: /home/aluno/Contador/clock1ms > OK | |

| − | + | ## 16 bits > Up only > Next | |

| − | + | ## Modulus, with a count modulus of 50000 > [Habilite a opção] '''Carry-out''' > Next. | |

| − | + | ## Next. | |

| − | + | ## Next. | |

| − | + | ## Habilite a opção '''Quartus II symbol file''' > Finish. | |

| − | + | ## Baixe o projeto ''deboucer'' [https://docente.ifsc.edu.br/odilson/CIL29003/Debounce.zip]. | |

| − | + | ## Abra o Navegador de Arquivos e descompacte o pacote zip baixado. | |

| − | + | ## Crie um novo arquivo ('''File >> New >> Block Diagram/Schematic File''') | |

| − | + | ## File > Open > {procure o arquivo} '''Debouncer_v2.bdf''' > Open. | |

| − | + | ## Salve o arquivo na pasta do projeto ('''File >> Save As >> /home/aluno/Contador/Debouncer_v2.bdf''') | |

| − | + | ## Configure o '''debouncer''' para ser o Top Level Entity e compile o esquemático. | |

| − | + | ## Crie um novo ''Symbol File'' para o debouncer: [File > Create/Update > Create Symbol File for Current File]. | |

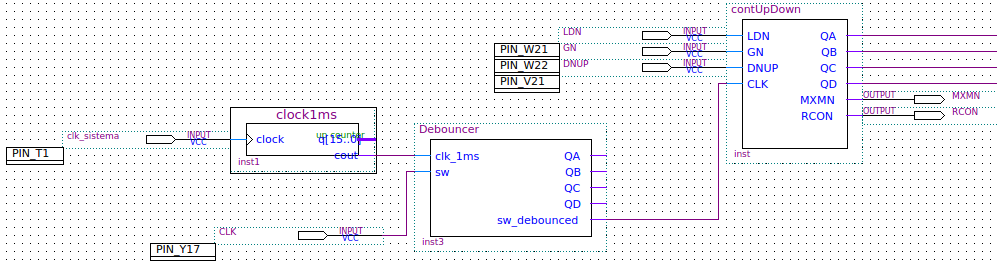

| − | + | ## Volte ao diagrama do contador (ContCompleto) e acrescente os blocos '''clock1ms''' e '''debouncer''': Symbol Tool > Project ... | |

| − | + | ## Interligue os blocos. 1) a entrada '''clock''' do '''clock1ms''' em '''PIN_T1'''. 2) A saída '''cout''' do '''clock1ms''' em '''clk_1ms''' do '''debouncer'''. 3) A entrada '''sw''' do '''debouncer''' na chave '''KEY[11]'''. 4) A saída '''sw_debounced''' no '''CLK''' do contador. Conforme figura ao lado: [[Arquivo:Debouncer.png|800px|thumb|Clique para Ampliar]] | |

| − | + | ## Compile o projeto, programe na placa e verifique o funcionamento. Perceba que agora a chave não deve mais apresentar os repiques. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

Edição atual tal como às 08h57min de 17 de maio de 2023

- Objetivos

- Inserir o circuito comercial de um Contador síncrono crescente/decrescente;

- Inserir o circuito comercial de um decodificadores de 7 segmentos;

- Testar os circuitos e gerar blocos para ser utilizado em um sistema maior;

- Gravar o sistema final em um kit de desenvolvimento e validação do funcionamento;

- Materiais necessários

- CI 74X191 Contador binário síncrono(disponível na biblioteca da ALTERA)

- CI 74X47/48 Decod 7-seg(disponível na biblioteca da ALTERA)

- Computador com software Quartus II da Altera.

- Kit DE2-115 - Cyclone: EP1C3T100A8 ou Mercurio IV - Cyclone IV: EP4CE30F23C7;

Teste do módulo contador binário síncrono

- Abra o Quartus II e crie um novo projeto com nome ContUpDown na pasta /home/aluno/Contador, utilizando a família family=Cyclone IV E com o dispositivo device=EP4CE115F29C7 (placa grande) ou Family = Cyclone IV E com dispositivo device = EP4CE30F23C7 (Placa pequena).

- Crie um novo diagrama esquemático (File >> New >> Block Diagram/Schematic File).

- Insira o diagrama esquemático de um Contador binário síncrono com 4 bits, conforme a figura abaixo.

- Após isso faça a Análise e Síntese do projeto: Processing >> Start Compilation.

- Abra o editor de forma de onda do simulador QSIM (File > New > University Programa VWF) (v 13.0 e 13.1).

- Defina o tempo de simulação (Edit > Set End Time ...) = 1000 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

- Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome tb_CI74191.vwf.

- Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK] (v. 13.0)

- Faça a simulação funcional do circuito lógico usando o sinal criado (Simulation > Run Functional Simulation)

- O resultado da simulação deve corresponder a um contador.

- Note que os bits das saídas estão agrupados e definidos como RADIX = "Decimal sem sinal". Para isso selecione os sinais [Edit > Grouping] [Group name = OUT] > [Radix = Unsigned Decimal] > [OK].

- Verifique se o resultado obtido corresponde a respostas do circuito implementado.

- QUESTIONÁRIO

- O que é necessário para fazer o contador fazer uma contagem descendente?

- Como fazer para parar a contagem por um tempo mantendo o sinal de clock ligado?

Teste do módulo decodificar de 7 segmentos

- Crie um novo diagrama esquemático (File >> New >> Block Diagram/Schematic File) no mesmo projeto para inserir o diagrama esquemático de um decodificar de 7 segmentos para display de anodo comum, conforme a figura abaixo. Para a FPGA grande (DE2-115) utilize o conversor 7447, conforme figura abaixo, e para a FPGA pequena (Macnica), que possui display Catodo Comum, deve-se utilizar o 7448. Ambos os componentes apresentam a mesma pinagem.

- Após salvar o arquivo como ConvBcdSsd.bdf na mesma pasta Contador. Mude o Top-Level Entity para este novo esquemático. Após isso faça a Análise e Síntese do projeto.

Criação do sistema completo com os módulos testados

- Selecione o diagrama esquemático do ContUpDown.bdf e crie um simbolo para este diagrama [File > Create/Update > Create Symbol File for Current File], [Save], [OK].

- Repita o procedimento para o ConvBcdSsd.bdf.

- Crie um novo diagrama esquemático com nome /home/aluno/Contador/ContCompleto (File >> New >> Block Diagram/Schematic File), no mesmo projeto para inserir o diagrama esquemático do sistema que será composto dos dois módulos, conforme a figura abaixo. Mude o Top-Level Entity para este novo esquemático.

Preparar o circuito lógico para gravação em um kit de desenvolvimento

Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit DE2-115 ou Mercurio IV.

- Confira a família e dispositivo a ser usado (Assignments > Devices), utilizando a família family=Cyclone IV E com o dispositivo device=EP4CE115F29C7 (Placa grande) ou device = EP4CE30F23C7 (Placa pequena), e faça uma nova Análise e Síntese para que a nova pinagem do FPGA seja reconhecida pelo Quartus.

- Atribua os pinos do circuito aos pinos do FPGA utilizando o Pin Planner [Assignments > Pin Planner].

- Para descobrir a pinagem do FPGA e sua associação com os componentes do kit consulte o Manual da DE2-115/Interfaces de entrada e saída da DE2-115 ou Pinagem_dos_dispositivos_de_entrada_e_saída_do_kit_MERCURIO_IV.

- Para facilitar a configuração dos pinos, Assignments >> pin Planner:

- Utilize o display de sete segmentos para mostrar a saída do decodificador de 7 segmentos, fazendo as devidas conexões.

- Utilize uma chave de contato momentâneo (push button) para gerar o sinal de CLK.

- Utilize a chave deslizante SW[0] para o sinal DN/UP, SW[1] para o sinal G', SW[2] para o sinal LD'.

- Utilize leds para mostrar o estado dos sinais MXMN, RBO' e RCO'. Pode ser os leds RGB.

- Compile o projeto. Note que agora a numeração dos pinos também aparece no diagrama esquemático.

- Use a porta USB-Blaster para fazer a programação na placa DE2-115 ou MERCURIO IV;

- No Quartus vá em (Tools > Programmer) para abrir a página de programação;

- Selecione o Hardware (Hardware Setup > USB-Blaster);

- Utilize o modo JTAG e clique em Start para começar a programação;

- Configure as chaves e verifique o funcionamento do circuito. Provavelmente você perceberá que a cada toque na chave associada ao clock ocorrerão vários saltos no contador, isso é provocado pelos repiques na chave.

- Normalmente uma chave apresenta os denominados repiques de sinal, ou seja, ao se alterar o estado da chave o sinal elétrico oscila várias vezes entre um nível lógico e outro, antes de estabilizar. Para evitar esse fenômeno pode-se fazer uso de um deboucer que gera um atraso entre os estados. Para usar o deboucer siga os seguintes passos:

- Tools > IP Catalog > Library > Basic Function > Arithmetic > LPM_COUNTER

- IP Variation file name: /home/aluno/Contador/clock1ms > OK

- 16 bits > Up only > Next

- Modulus, with a count modulus of 50000 > [Habilite a opção] Carry-out > Next.

- Next.

- Next.

- Habilite a opção Quartus II symbol file > Finish.

- Baixe o projeto deboucer [1].

- Abra o Navegador de Arquivos e descompacte o pacote zip baixado.

- Crie um novo arquivo (File >> New >> Block Diagram/Schematic File)

- File > Open > {procure o arquivo} Debouncer_v2.bdf > Open.

- Salve o arquivo na pasta do projeto (File >> Save As >> /home/aluno/Contador/Debouncer_v2.bdf)

- Configure o debouncer para ser o Top Level Entity e compile o esquemático.

- Crie um novo Symbol File para o debouncer: [File > Create/Update > Create Symbol File for Current File].

- Volte ao diagrama do contador (ContCompleto) e acrescente os blocos clock1ms e debouncer: Symbol Tool > Project ...

- Interligue os blocos. 1) a entrada clock do clock1ms em PIN_T1. 2) A saída cout do clock1ms em clk_1ms do debouncer. 3) A entrada sw do debouncer na chave KEY[11]. 4) A saída sw_debounced no CLK do contador. Conforme figura ao lado:

- Compile o projeto, programe na placa e verifique o funcionamento. Perceba que agora a chave não deve mais apresentar os repiques.