Mudanças entre as edições de "Contador binário síncrono"

Ir para navegação

Ir para pesquisar

| Linha 1: | Linha 1: | ||

;Objetivos: | ;Objetivos: | ||

| − | * Inserir o circuito comercial de um Contador síncrono crescente; | + | * Inserir o circuito comercial de um Contador síncrono crescente/derescente; |

* Inserir o circuito comercial de um decodificadores de 7 segmentos; | * Inserir o circuito comercial de um decodificadores de 7 segmentos; | ||

* Testar os circuitos e gerar blocos para ser utilizado em um sistema maior; | * Testar os circuitos e gerar blocos para ser utilizado em um sistema maior; | ||

| − | * | + | * Gravar o sistema final em um kit de desenvolvimento e validação do funcionamento; |

;Materiais necessários: | ;Materiais necessários: | ||

#CI [http://www.ti.com/lit/ds/symlink/sn74als191a.pdf 74X191 Contador binário síncrono](disponível na biblioteca da ALTERA) | #CI [http://www.ti.com/lit/ds/symlink/sn74als191a.pdf 74X191 Contador binário síncrono](disponível na biblioteca da ALTERA) | ||

| − | #CI [http://www.ti.com/lit/ds/symlink/sn7447a.pdf 74X47 Decod 7-seg](disponível na biblioteca da ALTERA) | + | #CI [http://www.ti.com/lit/ds/symlink/sn7447a.pdf 74X47/48 Decod 7-seg](disponível na biblioteca da ALTERA) |

#Computador com software Quartus II da Altera. | #Computador com software Quartus II da Altera. | ||

#Kit DE2-115 - [[Interfaces_de_entrada_e_saída_da_DE2-115 | Cyclone: EP1C3T100A8]] ou Mercurio IV - [[Pinagem_dos_dispositivos_de_entrada_e_saída_do_kit_MERCURIO_IV | Cyclone IV: EP4CE30F23C7]]; | #Kit DE2-115 - [[Interfaces_de_entrada_e_saída_da_DE2-115 | Cyclone: EP1C3T100A8]] ou Mercurio IV - [[Pinagem_dos_dispositivos_de_entrada_e_saída_do_kit_MERCURIO_IV | Cyclone IV: EP4CE30F23C7]]; | ||

| Linha 61: | Linha 61: | ||

==Preparar o circuito lógico para gravação em um kit de desenvolvimento== | ==Preparar o circuito lógico para gravação em um kit de desenvolvimento== | ||

| − | Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit DE2-115. [[Arquivo:KitDE2-115.png|200px|right|Clique para Ampliar]] | + | Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit '''DE2-115''' ou '''Mercurio IV'''. [[Arquivo:KitDE2-115.png|200px|right|Clique para Ampliar]] |

| − | *Mude a família e dispositivo a ser usado (Assignments > Devices), [Family = Cyclone IV E] e selecione | + | *Mude a família e dispositivo a ser usado (Assignments > Devices), [Family = Cyclone IV E] e selecione EP1C3T100A8 ou EP4CE115F29C7, e faça uma nova '''Análise e Síntese''' para que a nova pinagem do FPGA seja reconhecida pelo Quartus. |

*Atribua os pinos do circuito aos pinos do FPGA utilizando o '''Pin Planner''' [Assignments > Assignment Editor]. | *Atribua os pinos do circuito aos pinos do FPGA utilizando o '''Pin Planner''' [Assignments > Assignment Editor]. | ||

*Para descobrir a pinagem do FPGA e sua associação com os componentes do kit consulte o [ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE2-115/DE2_115.qsf Manual da DE2-115]/[[Interfaces de entrada e saída da DE2-115]] ou [[Pinagem_dos_dispositivos_de_entrada_e_saída_do_kit_MERCURIO_IV]]. | *Para descobrir a pinagem do FPGA e sua associação com os componentes do kit consulte o [ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE2-115/DE2_115.qsf Manual da DE2-115]/[[Interfaces de entrada e saída da DE2-115]] ou [[Pinagem_dos_dispositivos_de_entrada_e_saída_do_kit_MERCURIO_IV]]. | ||

*Para facilitar a configuração dos pinos: | *Para facilitar a configuração dos pinos: | ||

:*Utilize o display HEX0 para mostrar a saída do decodificador de 7 segmentos, fazendo as devidas conexões. | :*Utilize o display HEX0 para mostrar a saída do decodificador de 7 segmentos, fazendo as devidas conexões. | ||

| − | :*Utilize a chave de contato momentâneo KEY[ | + | :*Utilize a chave de contato momentâneo KEY[11] para gerar o sinal de CLK. |

:*Utilize a chave deslizante SW[0] para o sinal DN/UP, SW[1] para o sinal G', SW[2] para o sinal LD'. | :*Utilize a chave deslizante SW[0] para o sinal DN/UP, SW[1] para o sinal G', SW[2] para o sinal LD'. | ||

:*Utilize leds para mostrar a contagem em binário QD QC QB e QA. | :*Utilize leds para mostrar a contagem em binário QD QC QB e QA. | ||

Edição das 09h41min de 9 de maio de 2017

- Objetivos

- Inserir o circuito comercial de um Contador síncrono crescente/derescente;

- Inserir o circuito comercial de um decodificadores de 7 segmentos;

- Testar os circuitos e gerar blocos para ser utilizado em um sistema maior;

- Gravar o sistema final em um kit de desenvolvimento e validação do funcionamento;

- Materiais necessários

- CI 74X191 Contador binário síncrono(disponível na biblioteca da ALTERA)

- CI 74X47/48 Decod 7-seg(disponível na biblioteca da ALTERA)

- Computador com software Quartus II da Altera.

- Kit DE2-115 - Cyclone: EP1C3T100A8 ou Mercurio IV - Cyclone IV: EP4CE30F23C7;

Teste do módulo contador binário síncrono

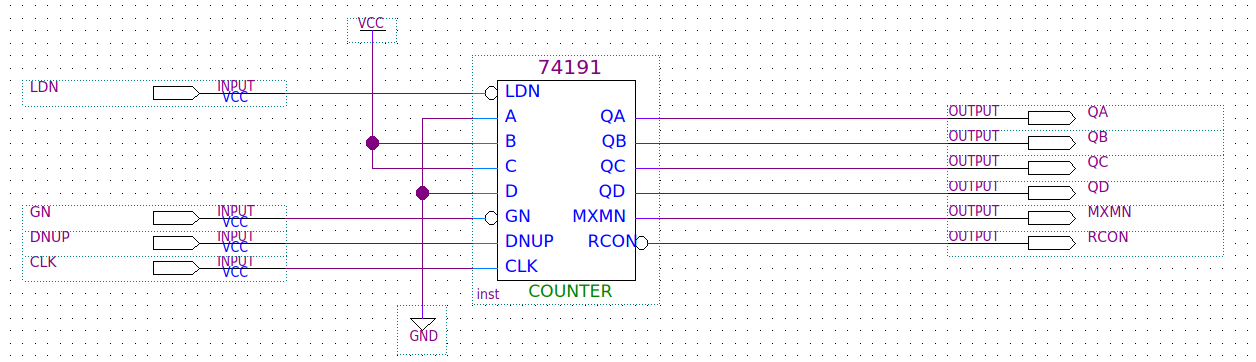

- Abra o Quartus II (versão 13.0.1 SE) e insira o diagrama esquemático de um Contador binário síncrono com 4 bits, conforme a figura abaixo.

- Após salvar o arquivo como CI74191.bdf em uma pasta vazia com nome Exp6, e crie um projeto Exp6.qpf utilizando a família family=Cyclone com o dispositivo device=EP1C3T100A8 ou Cyclone IV E com device = EP4CE30F23C7. Após isso faça a Análise e Síntese do projeto.

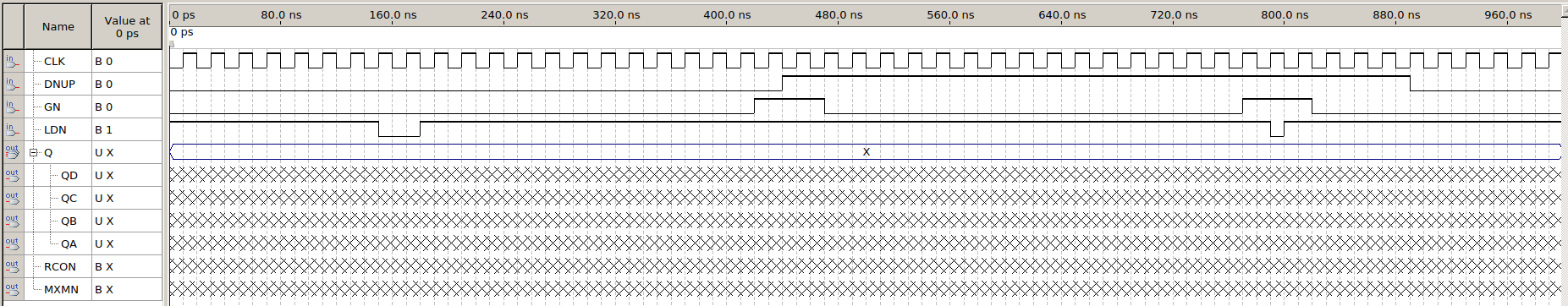

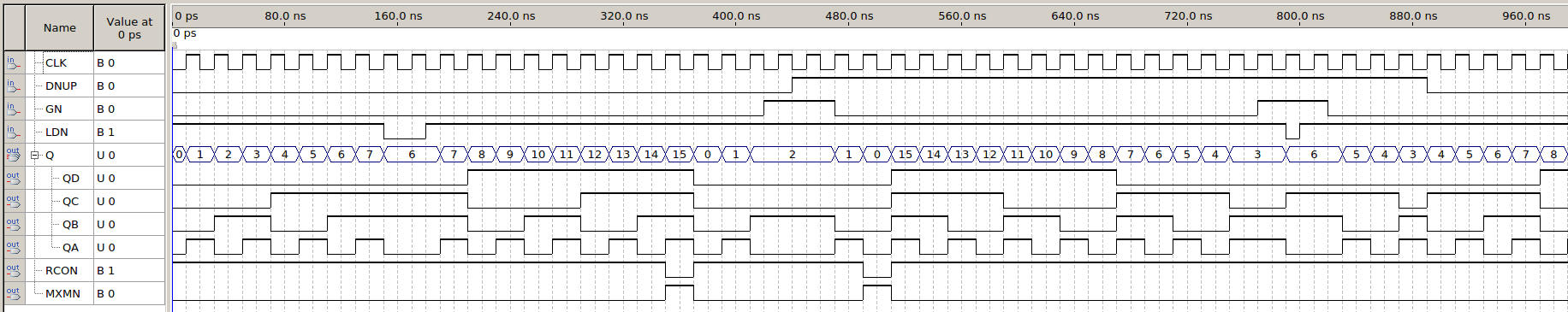

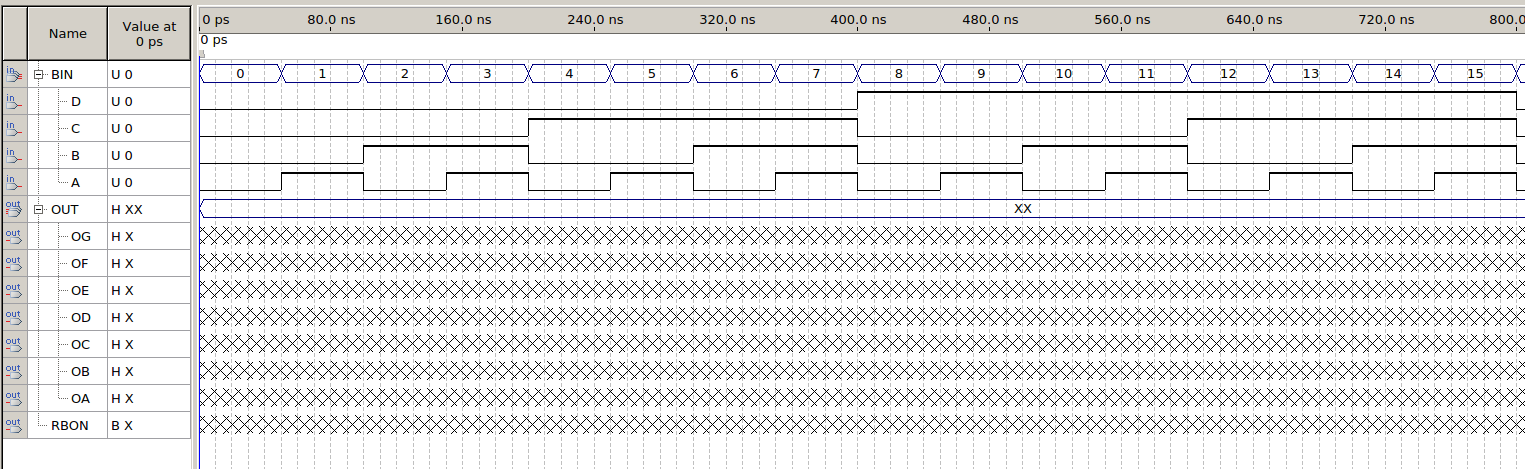

- Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome tb_CI74191.vwf.

- Verifique se o resultado obtido corresponde a respostas do circuito implementado.

- QUESTIONÁRIO

- O que é necessário para fazer o contador fazer uma contagem descendente?

- Como deve ser feita a configuração para o contador contar de 2 a 15?

- Como deve ser feita a configuração para contar de 0 a 9? e de 9 a 0?

- Como fazer para parar a contagem por um tempo mantendo o sinal de clock ligado?

Teste do módulo decodificar de 7 segmentos

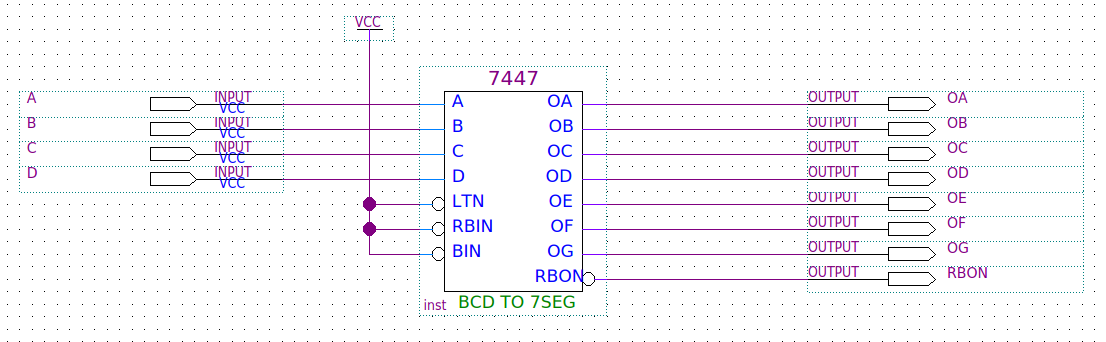

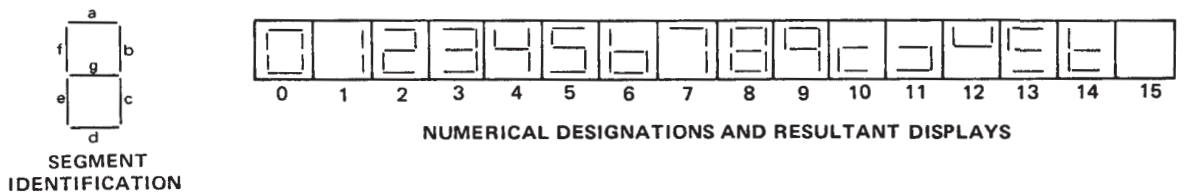

- Crie um novo diagrama esquemático no mesmo projeto para insirir o diagrama esquemático de um decodificar de 7 segmentos para display de anodo comum, conforme a figura abaixo. Se o kit em uso for o MERCURIO IV que possui display Catodo Comum, deve-se utilizar o CI7448, que possui a mesma pinagem.

- Após salvar o arquivo como CI7447.bdf na mesma pasta Exp6. Mude o Top-Level Entity para este novo esquemático. Após isso faça a Análise e Síntese do projeto.

- Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome tb_CI7447.vwf.

- Analise se o resultado está de acordo com a figura a seguir, ou a tabela verdade do datasheet do componente 74XX47.

- Se tiver dúvidas sobre o funcionamento do display consulte a página sobre o Display de 7 segmentos.

- QUESTIONÁRIO

- Neste Circuito Integrado (CI), qual é a condição para cada led do display acender?

- O que deveria ser feito caso o display fosse do tipo catodo comum?

- Qual é a função dos pinos LT, RBI, BI e RBO?

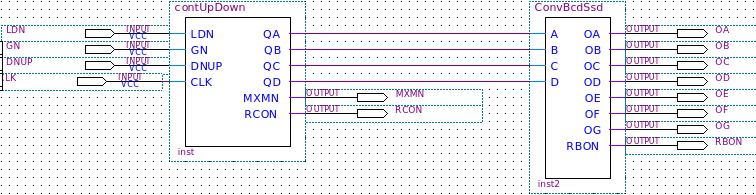

Criação do sistema completo com os módulos testados

- Selecione o diagrama esquemático do CI7447.bdf e crie um simbolo para este diagrama [File > Create/Update > Create Symbol File for Current File], [Save], [OK].

- Repita o procedimento para o CI74191.bdf.

- Crie um novo diagrama esquemático no mesmo projeto para inserir o diagrama esquemático do sistema que será composto dos dois módulos, conforme a figura abaixo. Mude o Top-Level Entity para este novo esquemático. Após isso faça a Análise e Síntese do projeto.

- Coloque o sinal de entrada para testar o circuito para verificar se os dois módulos estão funcionando corretamente. Faça o circuito contar de 0 até 15 e depois de 15 até 0.

Preparar o circuito lógico para gravação em um kit de desenvolvimento

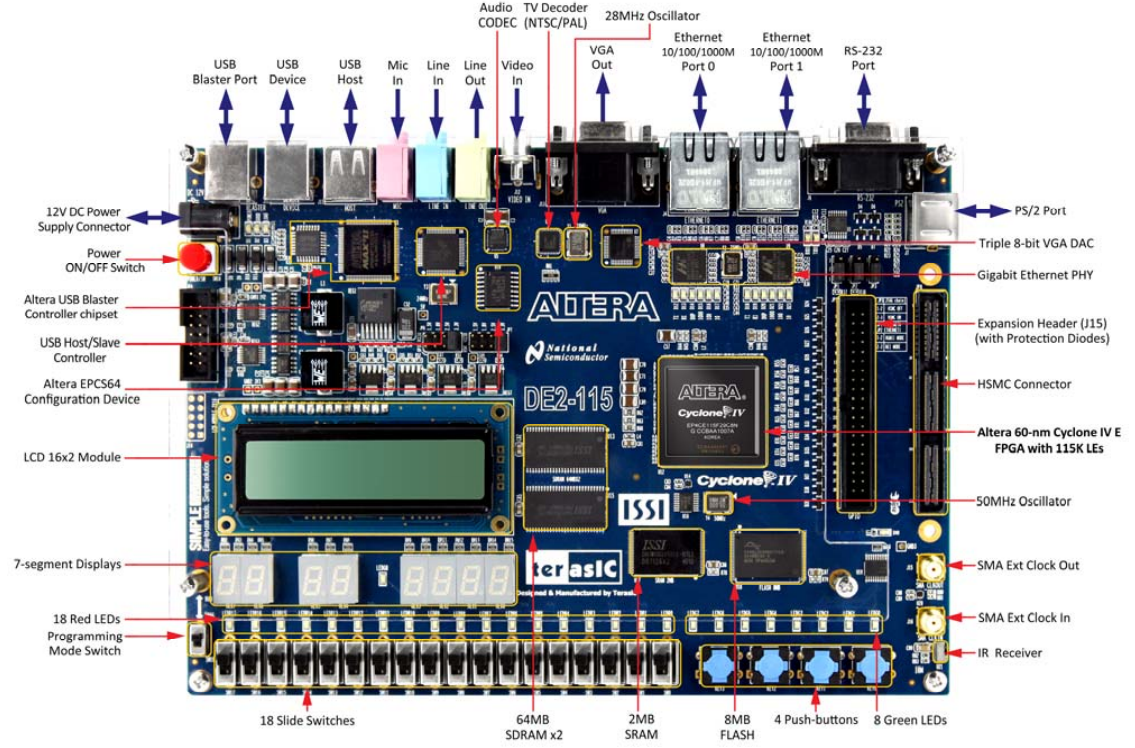

Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit DE2-115 ou Mercurio IV.

- Mude a família e dispositivo a ser usado (Assignments > Devices), [Family = Cyclone IV E] e selecione EP1C3T100A8 ou EP4CE115F29C7, e faça uma nova Análise e Síntese para que a nova pinagem do FPGA seja reconhecida pelo Quartus.

- Atribua os pinos do circuito aos pinos do FPGA utilizando o Pin Planner [Assignments > Assignment Editor].

- Para descobrir a pinagem do FPGA e sua associação com os componentes do kit consulte o Manual da DE2-115/Interfaces de entrada e saída da DE2-115 ou Pinagem_dos_dispositivos_de_entrada_e_saída_do_kit_MERCURIO_IV.

- Para facilitar a configuração dos pinos:

- Utilize o display HEX0 para mostrar a saída do decodificador de 7 segmentos, fazendo as devidas conexões.

- Utilize a chave de contato momentâneo KEY[11] para gerar o sinal de CLK.

- Utilize a chave deslizante SW[0] para o sinal DN/UP, SW[1] para o sinal G', SW[2] para o sinal LD'.

- Utilize leds para mostrar a contagem em binário QD QC QB e QA.

- Utilize leds para mostrar o estado dos sinais MXMN, RBO' e RCO'.

- Defina como alta impedância o estado dos pinos não utilizados no projeto. (Assignments > Devices), [Device and Pin Options...], escolha a (Category=Unused Pins), e selecione Reserve all unused pins: As input tri-stated. [OK].

- Compile o projeto. Note que agora a numeração dos pinos também aparece no diagrama esquemático.

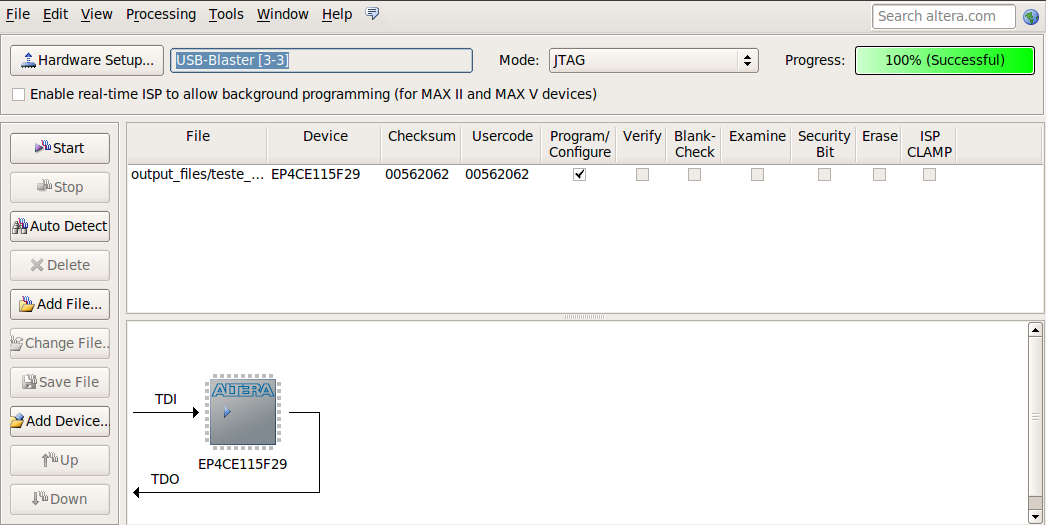

- Use a porta USB-Blaster para fazer a programação na placa DE2-115 ou MERCURIO IV;

- No Quartus vá em (Tools > Programmer) para abrir a página de programação;

- Selecione o Hardware (Hardware Setup > USB-Blaster);

- Utilize o modo JTAG e clique em Start para começar a programação;

- Normalmente uma chave apresenta os denominados repiques de sinal, ou seja, ao se alterar o estado da chave o sinal elétrico oscila várias vezes entre um nível lógico e outro, antes de estabilizar. Para evitar esse fenômeno pode-se fazer uso de um deboucer que gera um atraso entre os estados. Para usar o deboucer siga os seguintes passos:

- Tools > Megawizard Plugin Manager

- Create a new custom megafunction variation > Next.

- Aritimethic > LPM_counter > what name do you want for the outoput file?: clock1ms > Next

- 16 bits > Up only > Next

- Modulus, with a count modulus of 50000 > [Habilite a opção] Carry-out > Next.

- Next.

- Next.

- Habilite a opção Quartus II symbol file > Finish.

- Baixe o projeto deboucer Arquivo:Deboucer.qar.

- Restaure o projeto: Project > Restore Archived Project

- {procure o arquivo} Deboucer.qar > Open.

- OK

- Abra o esquemático do Debouncer_v2.

- Copie todo o arquivo: (Ctrl + a) e (Ctrl + c)

- Abra novamente o projeto do contador: File > Open Project > {informe o diretório e o nome} > Open.

- Crie um novo diagrama nesse projeto: File > New > Block Diagram/Schematic File > OK.

- Cole o diagrama copiado: (Ctrl + v).

- Salve o diagrama esquemático com o nome debouncer: (Ctrl + s) > debouncer > Save.

- Volte ao diagrama do contador e acrescente os blocos clock1ms e debouncer: Symbol Tool > Project ...

- Interligue os blocos. 1) a entrada clock do clock1ms em PIN_T1. 2) A saída cout do clock1ms em clk_1ms do debouncer. 3) A entrada sw do debouncer na chave KEY[0]. 4) A saída sw_debounced no CLK do contador.

- Compile o projeto, programe na placa e verifique o funcionamento. Perceba que agora a chave não deve mais apresentar os repiques.

- QUESTIONÁRIO

- Verifique o funcionamento da chave LD. Qual é a sua função?

- Verifique o funcionamento da chave G. Qual é a sua função?

- Verifique o funcionamento da chave UP/DN. Qual é a sua função?

- Confira se a contagem está sendo feita da forma correta e se os símbolos mostrados no display correspondem ao esperado e mostrado nos leds vermelhos. Existe algum problema na contagem?

- Analise as saídas MXMN, RBO, RCO tanto na contagem crescente como decrescente. O que estes sinais representam?