Contador Assíncrono Crescente - Roteiro para implementação e simulação com QUARTUS II(v.13), QSIM e kit DE2-115

Revisão de 12h55min de 24 de outubro de 2014 por Claudiacastro (discussão | contribs) (→Diagrama Esquemático)

Objetivos

- Inserir diagrama esquemático de um circuito lógico com o Quartus II

- Fazer a simulação funcional de um circuito com o QSIM

- Gerar formas de onda para entrada de simulação

- Fazer a simulação temporal de um circuito com o QSIM

- Preparar o circuito lógico para gravação no kit DE2-115

- Verificar os resultados obtidos.

Diagrama Esquemático

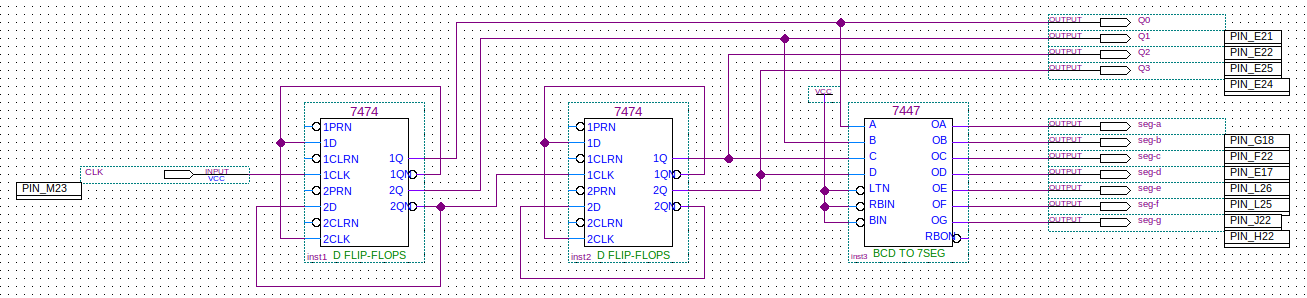

- Abra o Quartus II (versão 13.0 SE) e insira o diagrama esquemático (File > New > Block Diagram/Schematic)de um contador assíncrono crescente com 4 bits, conforme a figura abaixo.

- Clique

para selecionar os símbolos e clique

para selecionar os símbolos e clique  para inserir os pinos de entrada e saídas.

para inserir os pinos de entrada e saídas.

Salvar o arquivo como cont_up.bdf em uma pasta vazia com nome EX_1, e criar um projeto cont_up.qpf utilizando a família family=Cyclone IV E com o dispositivo device=EP4CE115F29C7. Após isso compile o projeto (Processing >.Star Compilation ou Crtl -L ou ícon correto do ambiente gráfico).

Se na compilação houver erro pela nomeação dos pinos, confira se o software não designou dois ou mais componente com o mesmo nome. Exemplo: Mais de um componente como "inst".

Simulação funcional com o QSIM

- Abra o simulador (New > University Program VWF).

- Crie as formas de onda para entrada da simulação

- Defina o tempo de simulação (Edit > Set End Time ...) = 400 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

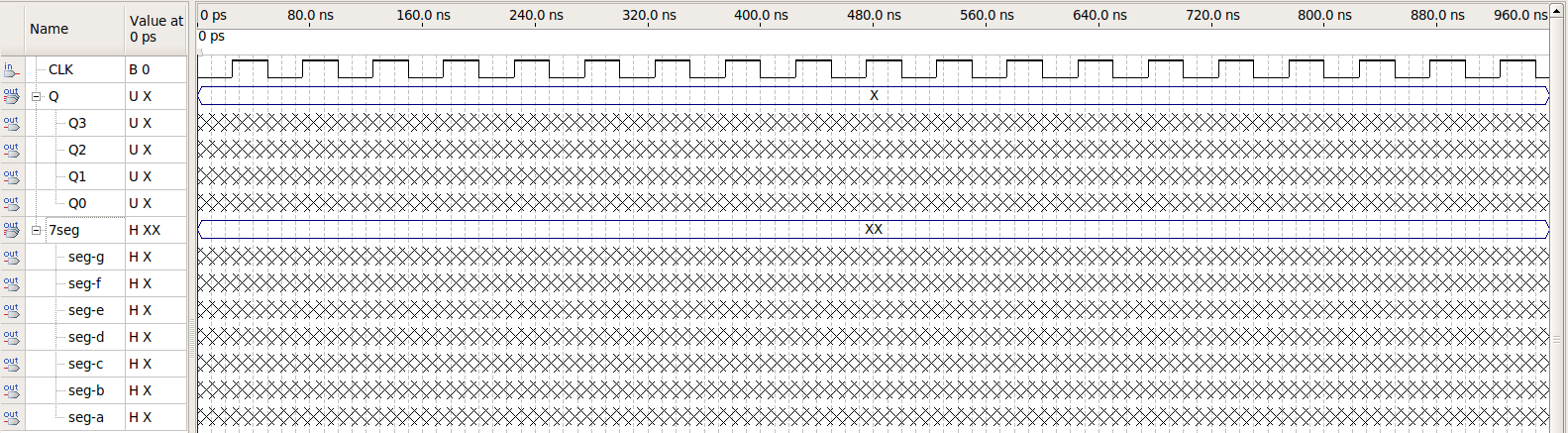

- Desenhe a forma de onda do sinal de clock de entrada selecionando a linha 'CLK' e clicando

(Clock > Period:20 ns > OK) gerando assim o sinal exibido na figura abaixo.

(Clock > Period:20 ns > OK) gerando assim o sinal exibido na figura abaixo. - Agrupe as saídas Q0, Q1, Q2 e Q3 (Grouping > Group... > Group name: Q > Radix: Unsigned Decimal > OK) e reverta a ordem dos bits(Na linha do agrupamento selecione o botão direito do mouse > Reverse Group or Bus Bit Oder).

- Repita o procedimento para o agrupamento das saídas do display 7-segmentos como mostrado na figura abaixo selecionanando a saída em Hexadecimanl (Radix: Hexadecimal > OK) e salve a simulação com o nome entrada.vwf.

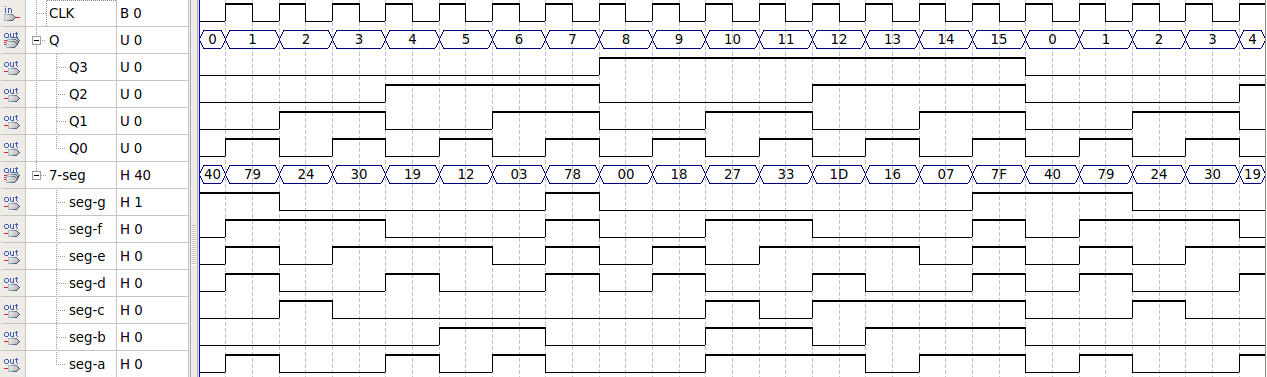

- Selecione o Quartus II como simulador (Simulation > Options > Quartus II Simulator > OK).

- Indique como a simulação será feita (Simulation > Run Functional Simulation).

- Verifique se o resultado obtido corresponde a um Contador assíncrono Crescente.

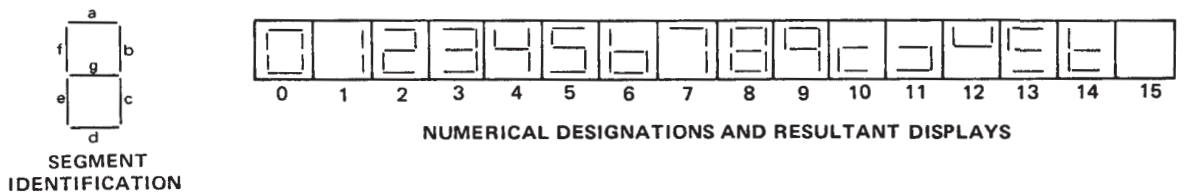

Inserindo um decodificador de 7 segmentos

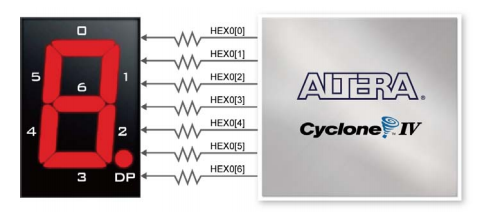

Para melhor visualizar o resultado da contagem, será usado um decodificador BCD para 7 segmentos comercial. Utilize o CI SN7447. Ligue o CI conforme indicado no diagrama esquemático. O resultado no display será uma contagem conforme a figura a seguir:

Preparando para gravar o circuito lógico no FPGA

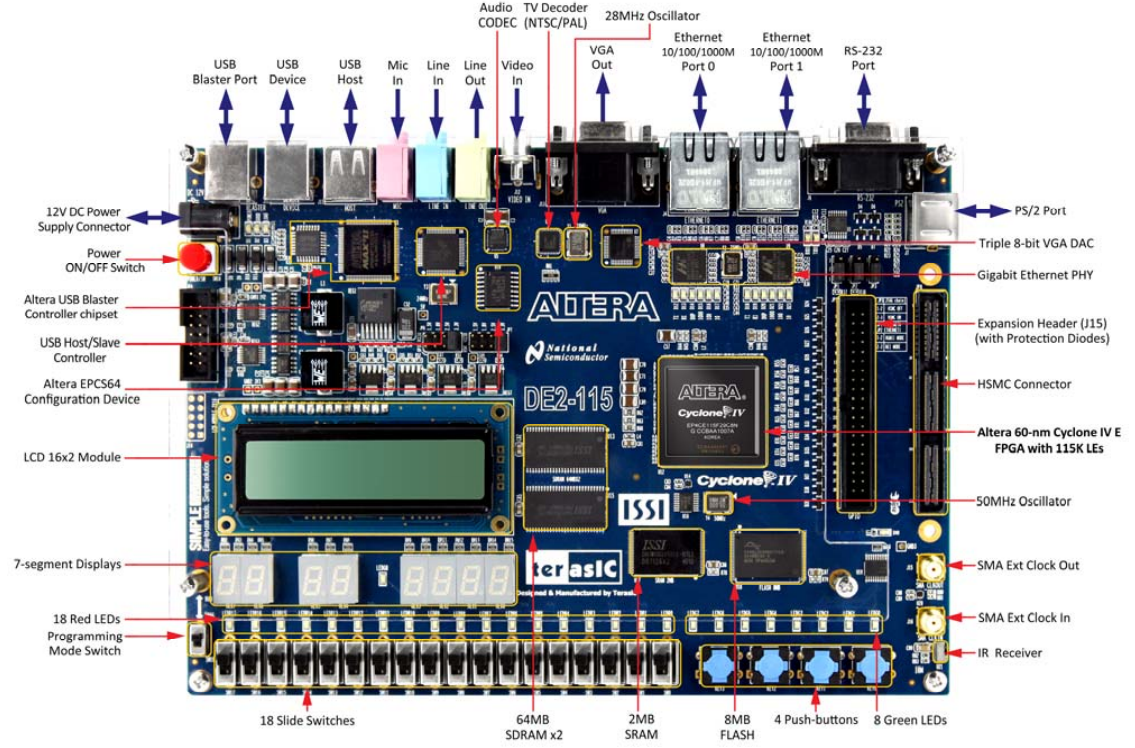

Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit DE2-115.

- Mude a família e dispositivo a ser usado (Assignments > Devices), [Family = Cyclone IV E] e selecione EP4CE115F29C7.

- Utilize o display HEX0 do kit para mostrar a contagem:

- Utilize os leds de LED0 a LED3 (verdes) para mostrar a contagem em binário.

- Utilize a chave KEY0 para gerar o sinal de CLK.

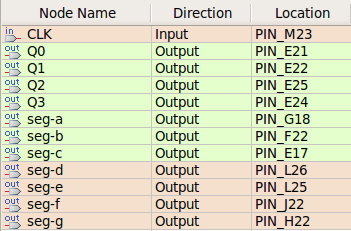

- Atribua os pinos conforme a pinagem do kit DE2-115.

- Ao final da configuração dos pinos, o Pin Planner deverá mostrar a seguinte pinagem:

- Defina como alta impedância o estado dos pinos não utilizados no projeto. (Assignments > Devices), [Device and Pin Options...], escolha a (Category=Unused Pins), e selecione Reserve all unused pins: As input tri-stated. [OK].

- Compile o projeto. Note que agora a numeração dos pinos também aparece no diagrama esquemático.

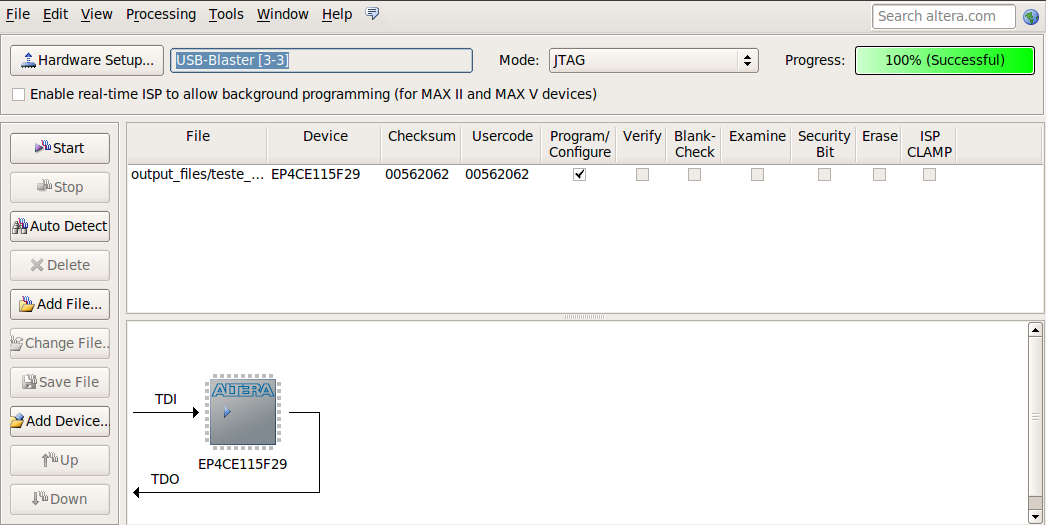

Gravando o projeto no FPGA

- Use a porta USB-Blaster para fazer a programação na placa DE2-115;

- No Quartus vá em (Tools > Programmer) para abrir a página de programação;

- Selecione o Hardware (Hardware Setup > USB-Blaster);

- Utilize o modo JTAG e clique em Start para começar a programação;