Mudanças entre as edições de "Conhecendo os dispositivos lógicos programáveis - QUARTUS II"

| (7 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

Este experimento visa conhecer a estrutura interna dos dispositivos lógicos programáveis. Será utilizado como base o software Quartus II e os dispositivos da ALTERA. | Este experimento visa conhecer a estrutura interna dos dispositivos lógicos programáveis. Será utilizado como base o software Quartus II e os dispositivos da ALTERA. | ||

| + | |||

| + | '''Atenção: Se você estiver usando a versão mais nova do Quartus veja [[Conhecendo os dispositivos lógicos programáveis - QUARTUS PRIME]].''' | ||

==Inserindo um circuito para programação== | ==Inserindo um circuito para programação== | ||

| Linha 5: | Linha 7: | ||

Abra um diagrama esquemático no Quartus II ('''File > Design Files > Block Diagram'''. Clique em [[Imagem:qsymbol.png]] para selecionar os símbolos e insira um contador "74161" (name: 74161). Em seguida clique em [[Imagem:qpin.png]] para inserir os pinos de entrada e saídas. Opcionalmente você pode usar o botão direito do mouse e inserir todos os pinos de entrada e saída selecionando '''Generate Pins for Symbol Ports'''. | Abra um diagrama esquemático no Quartus II ('''File > Design Files > Block Diagram'''. Clique em [[Imagem:qsymbol.png]] para selecionar os símbolos e insira um contador "74161" (name: 74161). Em seguida clique em [[Imagem:qpin.png]] para inserir os pinos de entrada e saídas. Opcionalmente você pode usar o botão direito do mouse e inserir todos os pinos de entrada e saída selecionando '''Generate Pins for Symbol Ports'''. | ||

| − | + | {{fig|1|Diagrama Esquemático do projeto| Imagem:Ckt74161.png| 700 px |}} | |

| − | |||

Após salvar o arquivo como "Ckt74161.bdf" em uma pasta vazia com nome AULA1, crie um projeto '''Ckt74161''' utilizando a família '''[https://www.altera.com/en_US/pdfs/literature/hb/max2/max2_mii51002.pdf MAX II]''' com o dispositivo device='''EPM240F100C4'''. | Após salvar o arquivo como "Ckt74161.bdf" em uma pasta vazia com nome AULA1, crie um projeto '''Ckt74161''' utilizando a família '''[https://www.altera.com/en_US/pdfs/literature/hb/max2/max2_mii51002.pdf MAX II]''' com o dispositivo device='''EPM240F100C4'''. | ||

| Linha 13: | Linha 14: | ||

==Observando a estrutura interna do PLD== | ==Observando a estrutura interna do PLD== | ||

| − | Após isso compile o projeto ('''Processing > Start Compilation'''). Depois de terminada a compilação, clique com o botão direito do mouse sobre o CI 74161 no diagrama esquemático e ('''Locate > Locate in Chip Planner''') o que fará abrir o '''Chip Planner''', indicando onde o 74161 está localizado. Note que várias cores são utilizada para indicar diferentes tipos de circuitos lógico e taxas de ocupação. | + | Após isso compile o projeto ('''Processing > Start Compilation'''). |

| − | + | ===Chip Planner=== | |

| − | + | Depois de terminada a compilação, clique com o botão direito do mouse sobre o CI 74161 no diagrama esquemático e ('''Locate > Locate in Chip Planner''') o que fará abrir o '''Chip Planner''', indicando onde o 74161 está localizado. Note que várias cores são utilizada para indicar diferentes tipos de circuitos lógico e taxas de ocupação. | |

| − | + | {{fig|2|Taxa de ocupação no Chip Planner| ChipPlanner_Ckt74161.png| 700 px |}} | |

| − | Na figura acima as áreas indicadas em '''marrom''' correspondem aos pinos de entrada/saída (I/O). A intensidade indica a ocupação dos pinos e do circuito correspondente a cada pino. As áreas em '''azul''' corresponde aos ''Logic Array Blocks'' (LABs), onde cada LAB contem 10 elementos lógicos | + | Na figura acima as áreas indicadas em '''marrom''' correspondem aos pinos de entrada/saída (I/O). A intensidade indica a ocupação dos pinos e do circuito correspondente a cada pino. As áreas em '''azul''' corresponde aos ''Logic Array Blocks'' (LABs), onde cada LAB contem 10 elementos lógicos. |

| − | + | ===Node Properties=== | |

| − | + | Para visualizar o interior desses circuito e sua ocupação clique sobre um desses elementos lógicos (ou sobre o pino de I/O) e observe o circuito na janela '''Node Properties'''. | |

| + | {{fig|3|Circuito do pino de I/O da família MAX II| IOCkt_MAXII.png| 700 px |}} | ||

| − | + | {{fig|4|Circuito do elemento lógico da família MAX II| LECkt_MAXII.png| 700 px |}} | |

| − | |||

Para observar os barramentos e as interconexões possíveis dentro o dispositivos, selecione na janela '''Layers Settings'''. Use o zoom para visualizar melhor a região desejada | Para observar os barramentos e as interconexões possíveis dentro o dispositivos, selecione na janela '''Layers Settings'''. Use o zoom para visualizar melhor a região desejada | ||

| Linha 31: | Linha 32: | ||

:[x] Ports | :[x] Ports | ||

| − | + | {{fig|5|Barramentos de roteamento da família MAX II| Routing_MAXII.png| 700 px |}} | |

| − | < | + | |

| + | Se quiser apenas observar os recursos que estão sendo utilizados de-selecione na janela '''Layers Settings''' [ ] Unused resources. | ||

| + | |||

| + | ==Pin Planner== | ||

| + | Para observar o leiaute dos pinos externos, e também para definir a posição de cada porta de entrada e saída do circuito é possível utilizar a interface do Pin Planner. | ||

| + | {{fig|6|Pin Planner| PinPlanner_MAXII.png| 800 px |}} | ||

| + | A parte de superior da interface mostra a posição física do pinos e sua função conforme a legenda de símbolos. Os pinos usados são destacados com cores. Na parte inferior da mesma interface é possível definir o pino que será atribuído a cada porta através da coluna '''Location''', assim como definir o tipo de interface a ser usada nos pinos de Entrada/Saída (coluna '''I/O Standard''') e também a limitação de corrente nestes pinos (coluna '''Current Strength'''). | ||

| + | Na borda esquerda da interface tem diversos icones que ativam diferentes visualizações nesta interface. | ||

| + | |||

| + | ==Relatório do tempo de processamento== | ||

| + | Para visualizar o tempo utilizado pelo Quartus para o processamento, é possível obter os valores na aba '''[Tasks]''' <!-- ou também no '''[Compilation Report > Flow Elapsed Time]''' -->. | ||

| + | {{fig|7|Tempo de processamento| Elapsed_Time.png| 400 px |}} | ||

| + | A figura mostra que foram usados 39 segundos para realizar todos as tarefas de compilação, desse tempo, 12 segundos foram para realizar a '''Análise e Síntese'''. | ||

| − | + | ==RTL Viewer== | |

| + | Para observar o circuito RTL obtido, siga o procedimento indicado em [[RTL Viewer]]. | ||

| + | {{fig|8|RTL Viewer| RTL_Ckt74161.png| 900 px |}} | ||

| − | == | + | ==Technology Map== |

| − | + | Para observar o mapeamento tecnologico realizado na sintese pelo quartus, siga o procedimento indicado em [[Technology Map Viewer]]. | |

| − | + | {{fig|9|Technology Map Viewer| TM_Ckt74161.png| 900 px |}} | |

Edição atual tal como às 15h56min de 9 de setembro de 2022

Este experimento visa conhecer a estrutura interna dos dispositivos lógicos programáveis. Será utilizado como base o software Quartus II e os dispositivos da ALTERA.

Atenção: Se você estiver usando a versão mais nova do Quartus veja Conhecendo os dispositivos lógicos programáveis - QUARTUS PRIME.

Inserindo um circuito para programação

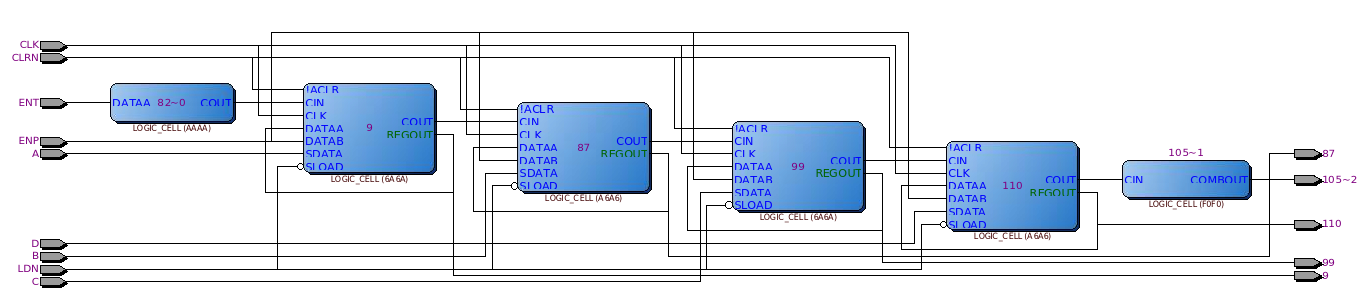

Abra um diagrama esquemático no Quartus II (File > Design Files > Block Diagram. Clique em ![]() para selecionar os símbolos e insira um contador "74161" (name: 74161). Em seguida clique em

para selecionar os símbolos e insira um contador "74161" (name: 74161). Em seguida clique em ![]() para inserir os pinos de entrada e saídas. Opcionalmente você pode usar o botão direito do mouse e inserir todos os pinos de entrada e saída selecionando Generate Pins for Symbol Ports.

para inserir os pinos de entrada e saídas. Opcionalmente você pode usar o botão direito do mouse e inserir todos os pinos de entrada e saída selecionando Generate Pins for Symbol Ports.

Figura 1 - Diagrama Esquemático do projeto

Após salvar o arquivo como "Ckt74161.bdf" em uma pasta vazia com nome AULA1, crie um projeto Ckt74161 utilizando a família MAX II com o dispositivo device=EPM240F100C4.

- Após salvar o arquivo "Ckt74161.bdf", o software oferece a opção de criar um projeto para o arquivo. Clique [Yes]. Em seguida clique [Next]. Selecione a pasta AULA1, e mantenha o nome do projeto e a top-level entity como Ckt74161, clicando [Next]. Clique novamente [Next] na tela de inclusão dos arquivos, pois o seu arquivo Ckt74161.bdf já foi incluído. No próxima tela de seleção da familia de DLPs e do número do dispositivo selecione Device Family: MAX II e Available device: EPM240F100C4, e clique em [Next], [Next] e [Finish] pois não há nenhum dado para ser alterado nestas telas de configuração.

- ATENÇÃO!!!: O Quartus não aceita caminhos de pastas com espaços, acentos ou outros caracteres exceto letras, números e "_"

Observando a estrutura interna do PLD

Após isso compile o projeto (Processing > Start Compilation).

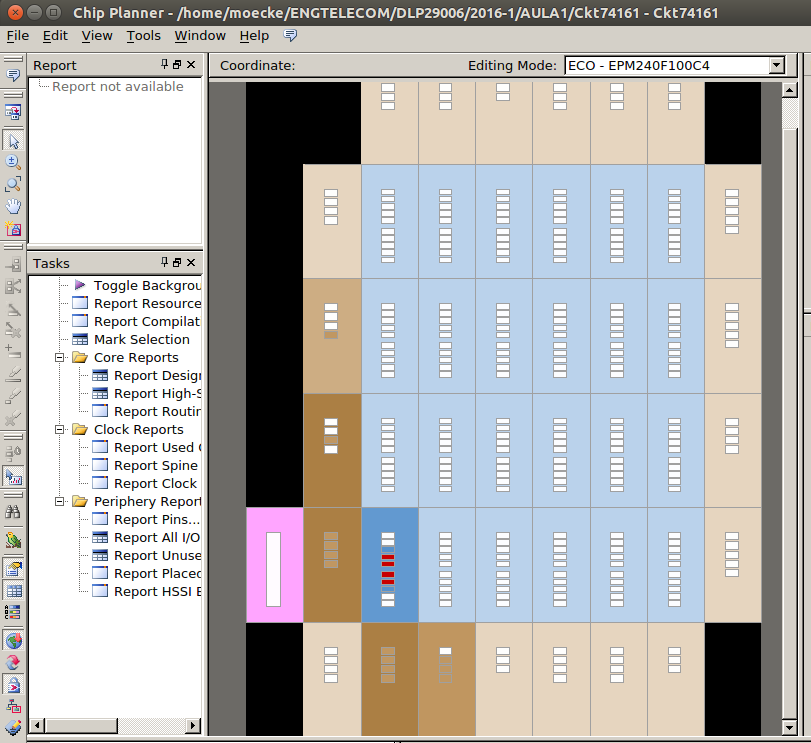

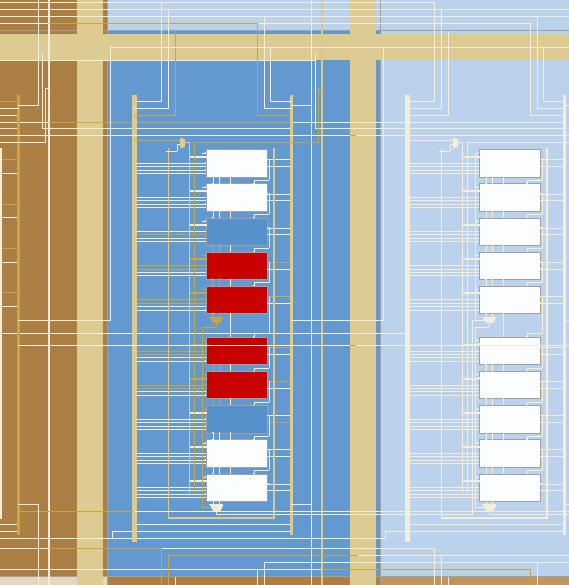

Chip Planner

Depois de terminada a compilação, clique com o botão direito do mouse sobre o CI 74161 no diagrama esquemático e (Locate > Locate in Chip Planner) o que fará abrir o Chip Planner, indicando onde o 74161 está localizado. Note que várias cores são utilizada para indicar diferentes tipos de circuitos lógico e taxas de ocupação.

Figura 2 - Taxa de ocupação no Chip Planner

Na figura acima as áreas indicadas em marrom correspondem aos pinos de entrada/saída (I/O). A intensidade indica a ocupação dos pinos e do circuito correspondente a cada pino. As áreas em azul corresponde aos Logic Array Blocks (LABs), onde cada LAB contem 10 elementos lógicos.

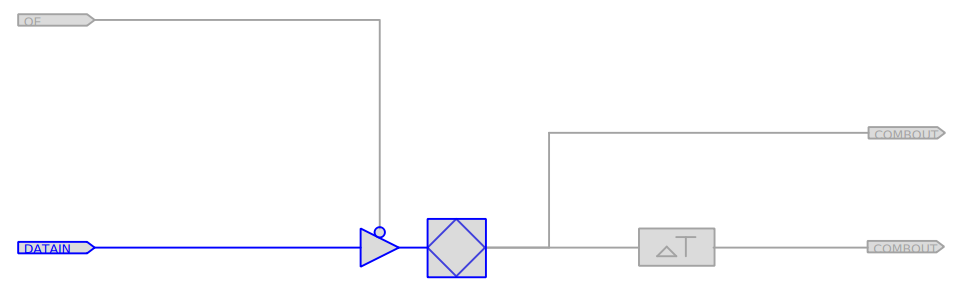

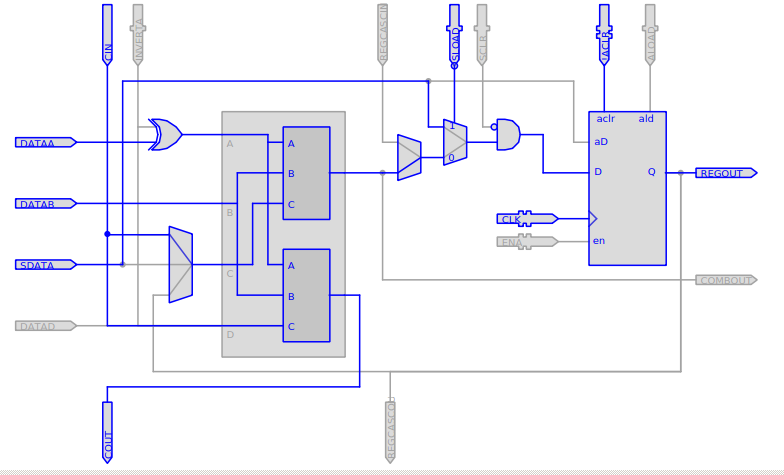

Node Properties

Para visualizar o interior desses circuito e sua ocupação clique sobre um desses elementos lógicos (ou sobre o pino de I/O) e observe o circuito na janela Node Properties.

Figura 3 - Circuito do pino de I/O da família MAX II

Figura 4 - Circuito do elemento lógico da família MAX II

Para observar os barramentos e as interconexões possíveis dentro o dispositivos, selecione na janela Layers Settings. Use o zoom para visualizar melhor a região desejada

- [x] Local Routing

- [x] Global Routing

- [x] Ports

Figura 5 - Barramentos de roteamento da família MAX II

Se quiser apenas observar os recursos que estão sendo utilizados de-selecione na janela Layers Settings [ ] Unused resources.

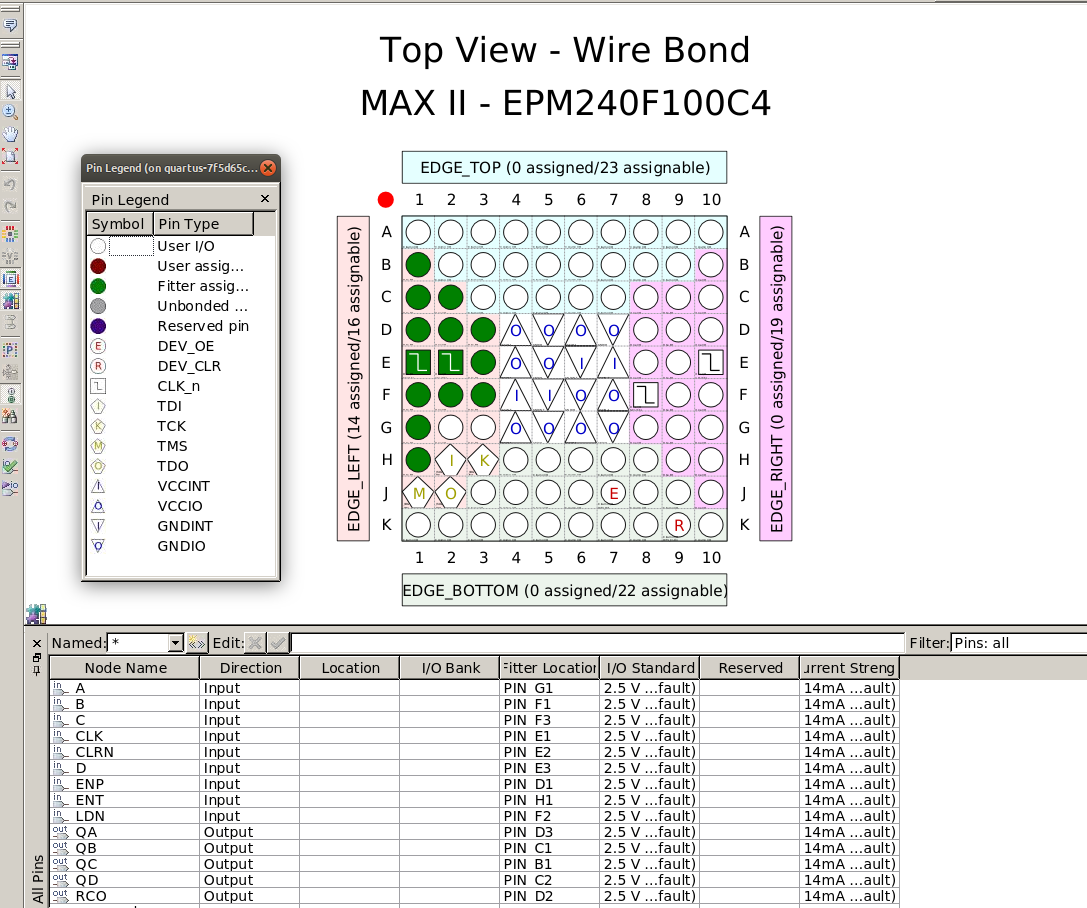

Pin Planner

Para observar o leiaute dos pinos externos, e também para definir a posição de cada porta de entrada e saída do circuito é possível utilizar a interface do Pin Planner.

Figura 6 - Pin Planner

A parte de superior da interface mostra a posição física do pinos e sua função conforme a legenda de símbolos. Os pinos usados são destacados com cores. Na parte inferior da mesma interface é possível definir o pino que será atribuído a cada porta através da coluna Location, assim como definir o tipo de interface a ser usada nos pinos de Entrada/Saída (coluna I/O Standard) e também a limitação de corrente nestes pinos (coluna Current Strength). Na borda esquerda da interface tem diversos icones que ativam diferentes visualizações nesta interface.

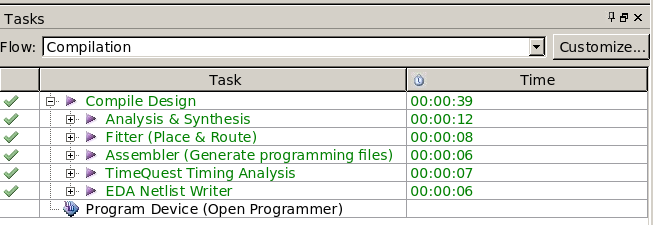

Relatório do tempo de processamento

Para visualizar o tempo utilizado pelo Quartus para o processamento, é possível obter os valores na aba [Tasks] .

Figura 7 - Tempo de processamento

A figura mostra que foram usados 39 segundos para realizar todos as tarefas de compilação, desse tempo, 12 segundos foram para realizar a Análise e Síntese.

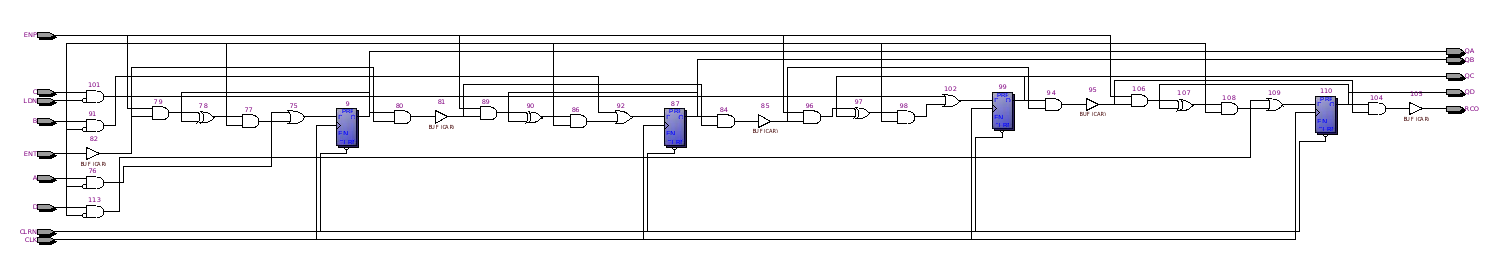

RTL Viewer

Para observar o circuito RTL obtido, siga o procedimento indicado em RTL Viewer.

Figura 8 - RTL Viewer

Technology Map

Para observar o mapeamento tecnologico realizado na sintese pelo quartus, siga o procedimento indicado em Technology Map Viewer.

Figura 9 - Technology Map Viewer