Configuração e uso do Signal Tap

Revisão de 08h17min de 16 de fevereiro de 2016 por Moecke (discussão | contribs) (→Exemplo de uso do Analisador Lógico "SignalTap II")

O software Quartus® II possui uma ferramenta de depuração a nível de sistema chamado SignalTap II que pode capturar e mostrar os sinais em qualquer FPGA em tempo real.

- Para configurar o SignalTap II, consulte o tutorial da ALTERA SIGNAL TAP II WITH VHDL DESIGNS.

- Mais informações podem ser encontradas em Design Debugging Using the SignalTap II Logic Analyzer

Resumo das dicas para uso

- 1. Antes de começar a usar o SignalTap II, faça a compilação (ou analise e sintese) do projeto para que os nomes dos objetos estejam disponíveis.

- 2. Open the SignalTap II window by selecting [File > New], which gives the window shown in Figure 3. Choose SignalTap II Logic Analyzer File and click [OK].

- 3. Save the file under the name "filename.stp". Click OK. For the dialog "Do you want to enable SignalTap II file "filename.stp" for the current project?" click Yes. The file "filename.stp" is now the SignalTap file associated with the project.

- Also, it is possible to have multiple SignalTap files for a given project, but only one of them can be enabled at a time. Having multiple SignalTap files might be useful if the project is very large and different sections of the project need to be probed.

- 4. We now need to add the nodes in the project that we wish to probe. In the Setup tab of the SignalTap II window, double-click in the area labeled Double-click to add nodes, bringing up the Node Finder window. Click on [] to show more search options. For the Filter field, select [SignalTap II:pre-synthesis]. Click [List]. This will now display all the nodes that can be probed in the project. Select the nodes you want to probe, and then click the button [>>] to add them to be probed. Then click [OK].

- 5. Before the SignalTap analyzer can work, we need to specify what clock is going to run the SignalTap module that will be instantiated within our design. To do this, in the Clock box of the Signal Configuration pane of the SignalTap window, click [...], which will again bring up the Node Finder window. Select List to display all the nodes that can be added as the clock, and then double-click 'your_clock'. Click [OK].

Exemplo de uso do Analisador Lógico "SignalTap II"

Para exemplificar o uso do SignalTap, iremos utilizar o kit Mercúrio IV da Macnica.

- 1.Baixe o arquivo [AnalogAudioLoopBack.qar", que contem o código VHDL do hardware de acesso aos conversores AD e DA, assim como um gerador de senoide.

- 2. Restaure o projeto e faça a análise e sintese.

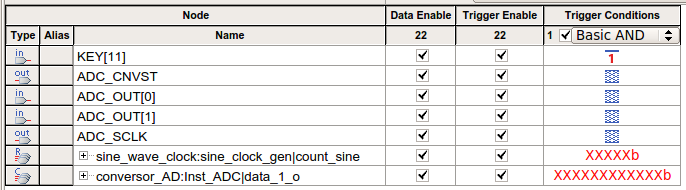

- 3. Crie um arquivo de análise para o SignalTap, incluindo os sinais conforme mostrado nas figuras abaixo. Selecione como condição de trigger o nível "1" para a KEY[11].

- 4. Use o sinal 'CLOCK_50MHz como sinal de amostragem para o SignalTap. Selecione [Sample depth = 512 (ou 16k)], [Storage qualifier Type = Continuous], [Trigger flow control = Sequencial], [Trigger position = Pré trigger position].

- 5. Salve o arquivo do SignalTap e assegure-se que ele está incluido no seu projeto. Faça a compilação completa do código e programa o FPGA.

- 6. Após programar a placa, na janela do SignalTap mude da aba [SETUP] para a aba [DATA] e execute [Processing > Run Analysis] para capturar um conjunto de dados igual a [Sample depth = 512 (ou 16k)]. Se quiser capturar continuamente os dados execute [Processing > Autorun Analysis]. Note que os dados serão adquiridos apenas enquanto a chave KEY[11] estiver acionada.