Mudanças entre as edições de "Códigos VHDL para uso nas Aulas"

Ir para navegação

Ir para pesquisar

(→Código) |

|||

| Linha 21: | Linha 21: | ||

(NOT eD AND eC AND NOT eB AND NOT eA); | (NOT eD AND eC AND NOT eB AND NOT eA); | ||

--implemente a lógica dos demais segmentos do display (0,1,2,3,4,5,6,7,8,9), sem minimização. | --implemente a lógica dos demais segmentos do display (0,1,2,3,4,5,6,7,8,9), sem minimização. | ||

| − | b <= | + | b <= (NOT eD AND eC AND NOT eB AND eA) OR |

| − | c <= | + | (NOT eD AND eC AND eB AND NOT eA); |

| − | d <= | + | c <= (NOT eD AND NOT eC AND eB AND eA); |

| − | e <= | + | d <= (NOT eD AND NOT eC AND NOT eB AND eA) OR |

| − | f <= | + | (NOT eD AND eC AND NOT eB AND NOT eA) OR |

| − | g <= | + | (NOT eD AND eC AND eB AND eA); |

| + | e <= (NOT eD AND NOT eC AND NOT eB AND eA) OR | ||

| + | (NOT eD AND NOT eC AND eB AND eA) OR | ||

| + | (NOT eD AND eC AND NOT eB AND NOT eA) OR | ||

| + | (NOT eD AND eC AND NOT eB AND eA) OR | ||

| + | (NOT eD AND eC AND eB AND eA) OR | ||

| + | ( eD AND NOT eC AND NOT eB AND eA); | ||

| + | f <= (NOT eD AND NOT eC AND NOT eB AND eA) OR | ||

| + | (NOT eD AND NOT eC AND eB AND NOT eA) OR | ||

| + | (NOT eD AND NOT eC AND eB AND eA) OR | ||

| + | (NOT eD AND eC AND eB AND eA); | ||

| + | g <= (NOT eD AND NOT eC AND NOT eB AND NOT eA) OR | ||

| + | (NOT eD AND NOT eC AND NOT eB AND eA) OR | ||

| + | (NOT eD AND eC AND eB AND eA); | ||

end discret_logic; | end discret_logic; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

Edição das 16h26min de 13 de março de 2012

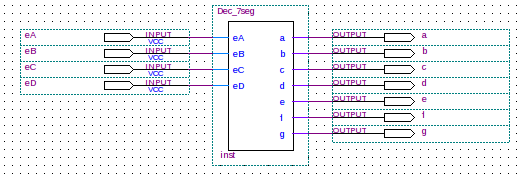

Descrever usando lógica discreta um decodificador de BCD para 7 segmentos.

Código

entity Dec_7seg is

port

(

eA,eB,eC,eD : in bit;

a,b,c,d,e,f,g : out bit

);

end Dec_7seg;

architecture discret_logic of Dec_7seg is

begin

--lógica que implementa o segmento a de um display (0,1,2,3,4,5,6,7,8,9), sem minimização.

-- 0 -> aceso (ON), 1 -> apagado (OFF)

a <= (NOT eD AND NOT eC AND NOT eB AND eA) OR

(NOT eD AND eC AND NOT eB AND NOT eA);

--implemente a lógica dos demais segmentos do display (0,1,2,3,4,5,6,7,8,9), sem minimização.

b <= (NOT eD AND eC AND NOT eB AND eA) OR

(NOT eD AND eC AND eB AND NOT eA);

c <= (NOT eD AND NOT eC AND eB AND eA);

d <= (NOT eD AND NOT eC AND NOT eB AND eA) OR

(NOT eD AND eC AND NOT eB AND NOT eA) OR

(NOT eD AND eC AND eB AND eA);

e <= (NOT eD AND NOT eC AND NOT eB AND eA) OR

(NOT eD AND NOT eC AND eB AND eA) OR

(NOT eD AND eC AND NOT eB AND NOT eA) OR

(NOT eD AND eC AND NOT eB AND eA) OR

(NOT eD AND eC AND eB AND eA) OR

( eD AND NOT eC AND NOT eB AND eA);

f <= (NOT eD AND NOT eC AND NOT eB AND eA) OR

(NOT eD AND NOT eC AND eB AND NOT eA) OR

(NOT eD AND NOT eC AND eB AND eA) OR

(NOT eD AND eC AND eB AND eA);

g <= (NOT eD AND NOT eC AND NOT eB AND NOT eA) OR

(NOT eD AND NOT eC AND NOT eB AND eA) OR

(NOT eD AND eC AND eB AND eA);

end discret_logic;