Mudanças entre as edições de "Avaliação 2 - SST"

Ir para navegação

Ir para pesquisar

(Criou página com 'TESTE') |

|||

| Linha 1: | Linha 1: | ||

| − | + | =Temporizador= | |

| + | |||

| + | [[Arquivo:temporizador.jpg]] | ||

| + | |||

| + | O sistema é composto por três seções: contador, drivers do display e display de sete segmentos. | ||

| + | |||

| + | * O contador é a parte sequencial do sistema. Ele deve contar segundos de 00 a 60, iniciando sempre que a entrada de habilitação (enable, ena) for alta e parando sempre que chegar a 60 ou quando enable for abaixada. | ||

| + | |||

| + | * O contador tem uma entrada reset (rst) assíncrona, que zera o sistema sempre que acionada. | ||

| + | |||

| + | * Ao alcançar 60, além do contador parar, a saída full_count deve ser acionada. | ||

| + | |||

| + | * O driver de SSD é a parte combinacional do sistema. Ele deve converter as saídas dos contadores (count1, count2) em sinais de 7 bits (dig1, dig2) para alimentar o mostrador de dois dígitos. | ||

| + | |||

| + | ;:<syntaxhighlight lang=vhdl> | ||

| + | |||

| + | library ieee; | ||

| + | use ieee.std_logic_1164.all; | ||

| + | |||

| + | entity timer is | ||

| + | generic (fclk : INTEGER :=2) ; --clock frequency | ||

| + | port (clk, rst, ena: IN std_logic; | ||

| + | full_count : OUT std_logic; | ||

| + | dig1, dig2: OUT std_logic_vector (6 downto 0)); --7 bits, display de 7 segmentos | ||

| + | end timer | ||

| + | |||

| + | architecture timer of timer is | ||

| + | begin | ||

| + | process(clk, rst, ena) | ||

| + | variable count0: INTEGER RANGE 0 to fclk; --para 1HZ | ||

| + | variable count1: INTEGER RANGE 0 to 10; --para dig1 | ||

| + | variable count2: INTEGER RANGE 0 to 7; – para dig2 | ||

| + | begin | ||

| + | |||

| + | --counters | ||

| + | if (rst='1') then | ||

| + | count0 := 0; | ||

| + | count1 := 0; | ||

| + | count2 := 0; | ||

| + | full_count <= '0'; | ||

| + | elseif (count1=0 and count2=6) then | ||

| + | full_count <='1'; | ||

| + | elseif (clk'EVENT and clk='1') then | ||

| + | if (ena='1') then | ||

| + | count0 := count0 + 1; | ||

| + | if (count0=fclk) then | ||

| + | count0 := 0; | ||

| + | count1 := count1 + 1; | ||

| + | if (count1=10) then | ||

| + | count1 := 0; | ||

| + | count2 := count2 + 1; | ||

| + | end if; | ||

| + | end if; | ||

| + | end if; | ||

| + | end if | ||

| + | |||

| + | --ssd drivers | ||

| + | case count1 is | ||

| + | when 0 => dig1 <= “1111110”; --126 | ||

| + | when 1 => dig1 <= “0110000”; --48 | ||

| + | when 2 => dig1 <= “1101101”; --109 | ||

| + | when 3 => dig1 <= “1111001”; --121 | ||

| + | when 4 => dig1 <= “0110011”; --51 | ||

| + | when 5 => dig1 <= “1011011”; --91 | ||

| + | when 6 => dig1 <= “1011111”; --95 | ||

| + | when 7 => dig1 <= “1110000”;--112 | ||

| + | when 8 => dig1 <= “1111111”; --127 | ||

| + | when 9 => dig1 <= “1111011”;--123 | ||

| + | when others => dig1 <= “1001111”; --79 (“E”) | ||

| + | end case; | ||

| + | case count2 is | ||

| + | when 0 => dig2 <= “1111110”; --126 | ||

| + | when 1 => dig2 <= “0110000”; --48 | ||

| + | when 2 => dig2 <= “1101101”; --109 | ||

| + | when 3 => dig2 <= “1111001”; --121 | ||

| + | when 4 => dig2 <= “0110011”; --51 | ||

| + | when 5 => dig2 <= “1011011”; --91 | ||

| + | when 6 => dig2 <= “1011111”; --95 | ||

| + | when others => dig2 <= “1001111”; --79 (“E”) | ||

| + | end case; | ||

| + | end process; | ||

| + | end timer; | ||

| + | |||

| + | </syntaxhighlight> | ||

Edição das 19h19min de 15 de abril de 2015

Temporizador

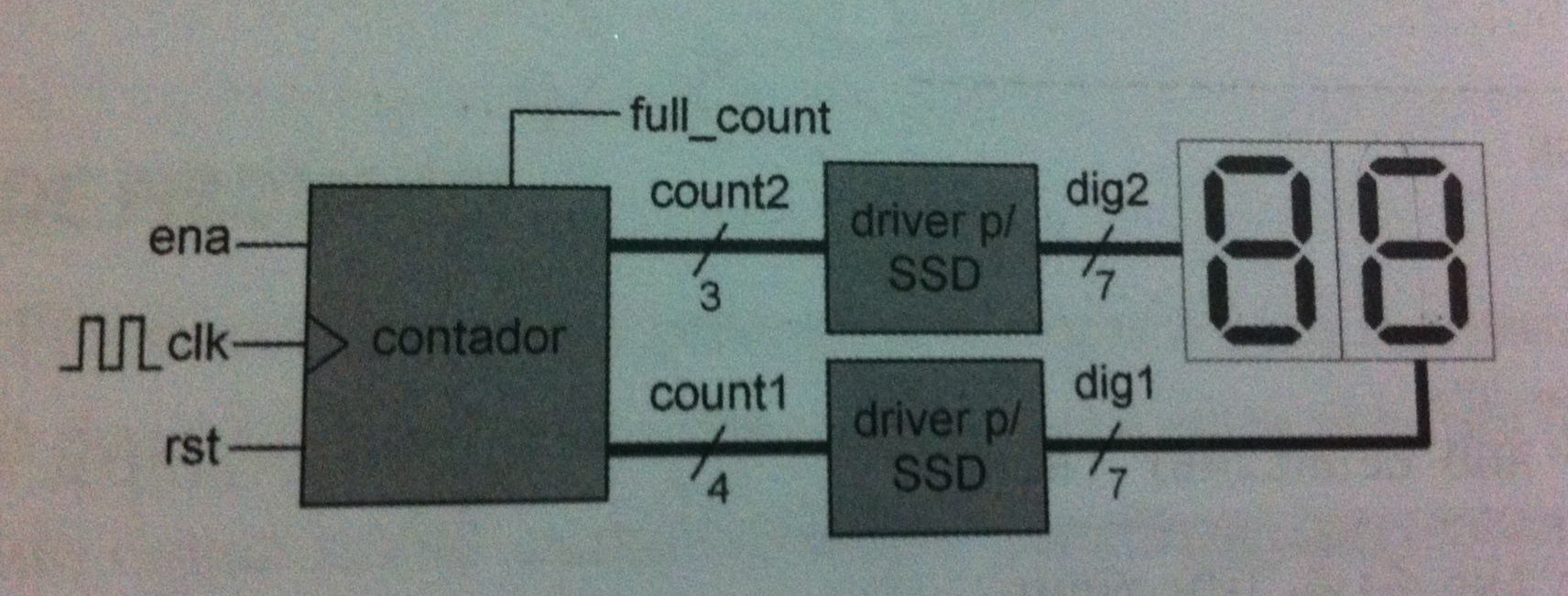

O sistema é composto por três seções: contador, drivers do display e display de sete segmentos.

- O contador é a parte sequencial do sistema. Ele deve contar segundos de 00 a 60, iniciando sempre que a entrada de habilitação (enable, ena) for alta e parando sempre que chegar a 60 ou quando enable for abaixada.

- O contador tem uma entrada reset (rst) assíncrona, que zera o sistema sempre que acionada.

- Ao alcançar 60, além do contador parar, a saída full_count deve ser acionada.

- O driver de SSD é a parte combinacional do sistema. Ele deve converter as saídas dos contadores (count1, count2) em sinais de 7 bits (dig1, dig2) para alimentar o mostrador de dois dígitos.

library ieee; use ieee.std_logic_1164.all; entity timer is generic (fclk : INTEGER :=2) ; --clock frequency port (clk, rst, ena: IN std_logic; full_count : OUT std_logic; dig1, dig2: OUT std_logic_vector (6 downto 0)); --7 bits, display de 7 segmentos end timer architecture timer of timer is begin process(clk, rst, ena) variable count0: INTEGER RANGE 0 to fclk; --para 1HZ variable count1: INTEGER RANGE 0 to 10; --para dig1 variable count2: INTEGER RANGE 0 to 7; – para dig2 begin --counters if (rst='1') then count0 := 0; count1 := 0; count2 := 0; full_count <= '0'; elseif (count1=0 and count2=6) then full_count <='1'; elseif (clk'EVENT and clk='1') then if (ena='1') then count0 := count0 + 1; if (count0=fclk) then count0 := 0; count1 := count1 + 1; if (count1=10) then count1 := 0; count2 := count2 + 1; end if; end if; end if; end if --ssd drivers case count1 is when 0 => dig1 <= “1111110”; --126 when 1 => dig1 <= “0110000”; --48 when 2 => dig1 <= “1101101”; --109 when 3 => dig1 <= “1111001”; --121 when 4 => dig1 <= “0110011”; --51 when 5 => dig1 <= “1011011”; --91 when 6 => dig1 <= “1011111”; --95 when 7 => dig1 <= “1110000”;--112 when 8 => dig1 <= “1111111”; --127 when 9 => dig1 <= “1111011”;--123 when others => dig1 <= “1001111”; --79 (“E”) end case; case count2 is when 0 => dig2 <= “1111110”; --126 when 1 => dig2 <= “0110000”; --48 when 2 => dig2 <= “1101101”; --109 when 3 => dig2 <= “1111001”; --121 when 4 => dig2 <= “0110011”; --51 when 5 => dig2 <= “1011011”; --91 when 6 => dig2 <= “1011111”; --95 when others => dig2 <= “1001111”; --79 (“E”) end case; end process; end timer;