Mudanças entre as edições de "ADM-EngTel Página da Disciplina"

Ir para navegação

Ir para pesquisar

| Linha 125: | Linha 125: | ||

Projeto didático em Proteus parte 6: | Projeto didático em Proteus parte 6: | ||

*I/O mapeado em memória | *I/O mapeado em memória | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

Edição das 00h56min de 20 de março de 2016

Informações Gerais

- Professor: Clayrton Monteiro Henrique

e-mail: clayrton.henrique@ifsc.edu.br

Plano de Ensino

Recursos

Aulas

Aula 01 - Dia 29/7/2015

- Apresentação inicial;

- Visão geral do funcionamento de um sistema microprocessado

Aula 02 - Dia 05/10/2015

Objetivos

- reapresentar os objetivos da disciplina

- trabalhar memórias na forma de diagrama em blocos

- apresentar barramentos de endereço/dados/controle

- diferenciar conteúdo de endereço de memória;

- apresentar o procedimento de acesso para escrita e para a leitura;

- apresentar um diagrama de tempo simplificado de acesso a memória;

- apresentar a CPU/microcontrolador como a "entidade" que acessa a memória;

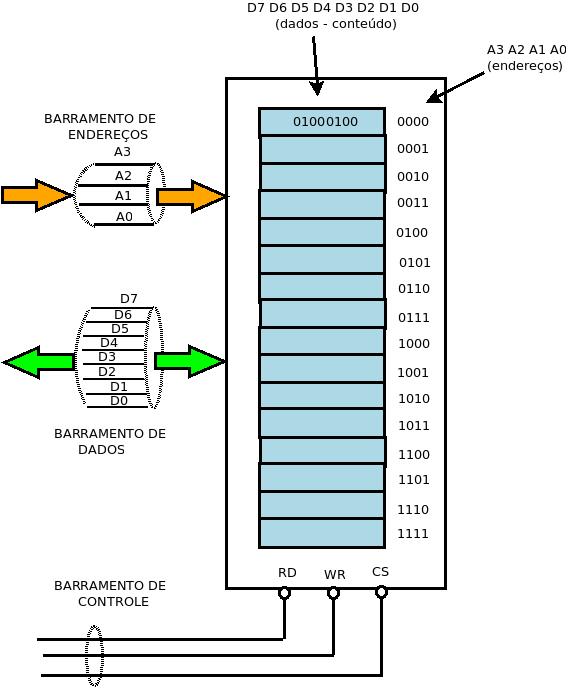

Diagrama em blocos da memória e barramentos

No diagrama abaixo está representado um bloco de memória primária de 16x8 (dezesseis endereços por 8 bits).

- Note que uma posição de memória pode ser vista como uma caixa que possue um endereço e um conteúdo.

- O conteúdo associado a posição de memória é uma palavra binária e, neste caso, possui 8 bits;

Para que us dispositivo externo possa "acessar" a memória para leitura ou escrita, ele deve se utilizar de um conjunto de fios que chamamos de barramentos.

Barramento de Endereços

Este barramento permite determinar o endereço de uma posição a ser acessada na memória. Um barramento de 4 linhas de endereço é designado por A3,A2,A1 e A0.

Diagrama de Tempo - Acesso para escrita

Tarefa

- Ler apostila de memória

Aula 03 - Dia 14/10/2015

- Memórias - Tipos e características construtivas

Aula 04 - Dia 17/10/2015

- Introdução ao Proteus

Aula 05 - Dia 19/10/2015

- Exercícios de associação de memória usando Proteus

Aula 06 - Dia 21/10/2015

- Arquitetura de processadores - Harvard vs. von Neumann

Aula 07 - Dia 26/10/2015

Projeto didático em Proteus parte 1:

- Mapeamento de memórias ROM e RAM em um mesmo barramento

Aula 08 - Dia 28/10/2015

- BIP - Basic Instruction Processor

Aula 09 - Dia 04/11/2015

- Instruções BIP 2

Aula 10 - Dia 09/11/2015

Projeto didático em Proteus parte 2:

- Registradores especiais mapeados em memória

Aula 11 - Dia 11/11/2015

- Exercícios com ASM BIP: laços de repetição

Aula 12 - Dia 16/11/2015

Projeto didático em Proteus parte 3:

- Acumulador mapeado em memória

Aula 13 - Dia 18/11/2015

- Conceito de pilha do Program Counter

Aula 14 - Dia 23/11/2015

Projeto didático em Proteus parte 4:

- Unidade lógica-aritmética

Baixar o arquivo contendo partes do processador didático, para os próximos passos.

Aula 15 - Dia 25/11/2015

- Arquitetura de microcontroladores comerciais

Aula 16 - Dia 30/11/2015

Projeto didático em Proteus parte 5:

- Contador de programa

Aula 17 - Dia 02/12/2015

- Sistemas de entrada e saída - periféricos

Aula 18 - Dia 07/12/2015

Projeto didático em Proteus parte 6:

- I/O mapeado em memória