Circuitos Lógicos Aritméticos

Revisão de 18h42min de 5 de junho de 2014 por Moecke (discussão | contribs) (→Simulação funcional com o QSIM)

Objetivos

- Construir testar um circuito somador completo (FA -full adder) a partir de portas lógicas usando o diagrama esquemático do QUARTUS II.

- Fazer a simulação funcional do circuito com o QSIM

- Construir um somador de 4 bits usando os FA como subcircuito.

- Construir um multiplicador de 4 bits usando os FA como subcircuito

- Preparar o circuito para gravação e realização no kit DE2-115

Diagrama Esquemático

Abra o Quartus II (versão 13.0) e insira o diagrama esquemático do somador completo, conforme a figura abaixo.

Após salvar o arquivo como FullAdder.bdf em uma pasta vazia com nome PROJ2, e crie um projeto FullAdder.qpf utilizando a família family=Cyclone com o dispositivo device=EP1C3T100A8. Após isso faça a Análise e Sintese do projeto.

Simulação funcional com o QSIM

- Abra o editor de forma de onda do simulador QSIM (File > New > University Programa VWF) (versão 13.0 e 13.1).

- Defina o tempo de simulação (Edit > Set End Time ...) = 200 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

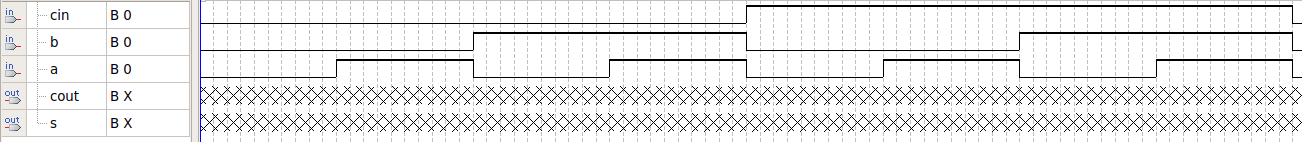

- Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome teste1.vwf.

- Indique como a simulação será feita (Assign > Simulation Settings ...). Escolha o arquivo de forma de onda de entrada que você criou (teste1.vwf) e selecione a tipo de simulação [x] Functional.

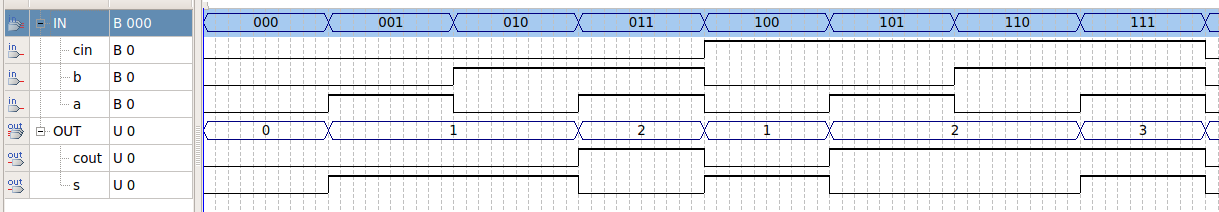

- Faça a simulação do circuito lógico usando o sinal criado (Processing > Start Simulation)

- Abra o arquivo resultado da simulação (File > Open Simulation Output File). E verifique se o resultado obtido corresponde a um Registrador de Deslocamento. Salve o sinal de saída como resultadoF1.vwf.

- Note que a entrada de SET e RESET não estão sincronizadas com o relógio (CLK). Os sinais de saída dos DFF são todos sincronizados com a borda de subida do CLK.

- Meça a duração dos pulsos ALTOS após o tempo de 120 ns do sinal D, Q1, Q2, Q3 e Q4. Explique o motivo da diferença de duração.

- Inverta o CLK e repita a simulação. Salve a entrada como teste2.vwf e o sinal de saída como resultadoF2.vwf.

- Entre 120ns e 150ns mude o sinal de SET para '1' e repita a simulação. Salve a entrada como teste3.vwf e o sinal de saída como resultadoF3.vwf.

Simulação temporal com o QSIM

- Indique como a simulação será feita (Assign > Simulation Settings ...). Escolha o arquivo de forma de onda de entrada que você criou (teste1.vwf) e selecione a tipo de simulação [x] Timing.

- Faça a simulação do circuito lógico. Abra o arquivo resultado da simulação. Verifique as mudanças que ocorreram nos sinais de saída Q1, Q2, Q3 e Q4. Salve o sinal de saída como resultadoT1.vwf.

- Meça os atrasos dos sinais Q1, Q2, Q3 e Q4 em relação ao sinal RESET.

- Meça os atrasos dos sinais Q1, Q2, Q3 e Q4 em relação ao sinal CLK.

- Qual é a conclusão que você pode chegar em relação ao tempo de propagação e ?

- Como você poderia medir o tempo de atraso dos sinais Q1, Q2, Q3 e Q4 em relação ao sinal SET?

- Meça a duração dos pulsos ALTOS após o tempo de 120 ns do sinal D, Q1, Q2, Q3 e Q4. Explique o motivo da diferença de duração.

Preparando para gravar o circuito lógico no FPGA

Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit DE0-Nano.

- Mude a família e dispositivo a ser usado (Assignments > Devices), [Family = Cyclone IV E] e selecione EP4CE22F17C6

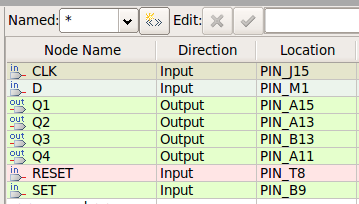

- Atribua os pinos conforme a pinagem do kit DE0-Nano, utilizando como entradas a chave KEY[0] como CLK, DIPswitch[0] como D, DIPswitch[1] como RESET e DIPswitch[2] como SET. Como saída utilizaremos os leds verdes e Q1 a Q4 como LED[0] a LED[3].

- Defina como alta impedância o estado dos pinos não utilizados no projeto. (Assignments > Devices), [Device and Pin Options...], escolha a (Category=Unused Pins), e selecione Reserve all unused pins: As input tri-stated. [OK].

- Compile o projeto. Note que agora a numeração dos pinos aparece no diagrama esquemático.