Códigos VHDL para uso nas Aulas 2011-1

Revisão de 06h19min de 19 de agosto de 2010 por Moecke (discussão | contribs) (→Descrição do hardware de um registrador com 4 Latch tipo D)

Descrição do hardware de uma porta E

entity PortaE is

port

(

-- Input ports

A,B : in bit;

-- Output ports

C : out bit

);

end entity PortaE;

architecture v1 of PortaE is

begin

C <= A and B;

end architecture v1;

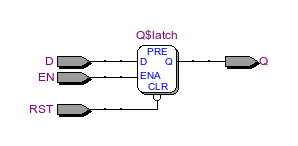

Descrição do hardware de um Latch tipo D

O circuito descrito é ativo a entrada alto a entrada EN e ativo ao reset baixo RST

library IEEE;

use IEEE.std_logic_1164.all;

entity LAD is

port(

D, EN, RST: in std_logic;

Q: out std_logic

);

end entity LAD;

architecture v1 of LAD is

begin

process (D,EN,RST)

begin

if (RST = '0') then

Q <= '0'; -- reset ocorre quando RST=0

elsif (EN = '1') then

Q <= D; -- O valor de D passa para Q quando EN=1

-- note que a falta do uso de um else indica que nada deve ser feito caso contrário,

-- portanto o valor anterior de D permanece inalterado -> armazenamento (storage state)

end if;

end process;

end architecture v1;

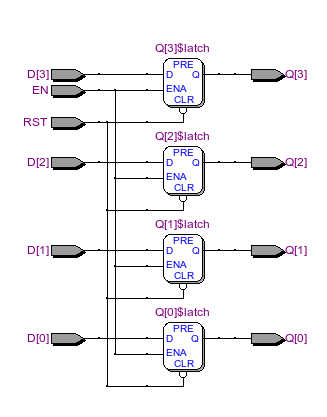

Descrição do hardware de um registrador com 4 Latch tipo D

O circuito descrito é ativo a entrada alto a entrada EN e ativo ao reset baixo RST

library IEEE;

use IEEE.std_logic_1164.all;

entity REGD4 is

port(

EN, RST: in std_logic;

D: in std_logic_vector (3 downto 0);

Q: out std_logic_vector (3 downto 0)

);

end entity REG;

architecture v1 of REGD4 is

begin

process (D,EN,RST)

begin

if (RST = '0') then

Q <= "0000"; -- reset ocorre quando RST=0

elsif (EN = '1') then

Q <= D; -- O valor de D passa para Q quando EN=1

end if

end process;

end architecture v1;

Descrição do hardware de um registrador com N Latch tipo D

O circuito descrito é ativo a entrada alto a entrada EN e ativo ao reset baixo RST Note neste exemplo o poder do VHDL de parametrizar o tamanho do registrador através do generic

library IEEE;

use IEEE.std_logic_1164.all;

entity REGDN is

generic (N: integer := 4)

port(EN, RST: in std_logic;

D: in std_logic_vector (N-1 downto 0);

Q: out std_logic_vector (N-1 downto 0));

end entity REGDN ;

architecture v2 of REGDN is

begin

process (D,EN,RST)

begin

if (RST = '0') then

Q <= (others => '0'); -- reset todos os bits Q quando RST=0

elsif (EN = '1') then

Q <= D; -- passa todos os valores de D para as saídas Q correspondentes

end if;

end process;

end architecture v2;