DIG222802 2018 2 AULA06

Apresentação

Olá Estudante,

Até agora aprendemos sobre os flip-flop e contadores assíncronos e síncronos, crescente, decrescente, modulares, com carga inicial e tudo mais. Aprendemos também a compreender as formas de onda expressas nos diagramas de funcionamento e agora vamos aprender sobre um das aplicações muito apreciadas com flip-flops, que são os registradores.

Bons Estudos!

Prof. Douglas A.

Registradores

Uma das formas mais comuns de utilização dos flip-flop (FF) é no armazenamento e transferência de informações (bits). Cada FF possui a capacidade de armazenar um bit. Vários FFs podem ser configurados para formar um registrador no qual pode-se armazenar uma palavra binária. São necessários tantos FF quantos forem os bits da palavra. Os registradores armazenam bits e têm a capacidade de transferir esses bits para outros registradores seja de forma simultânea ou uma a uma.

Registradores do tipo porta paralela

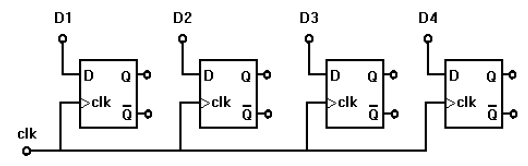

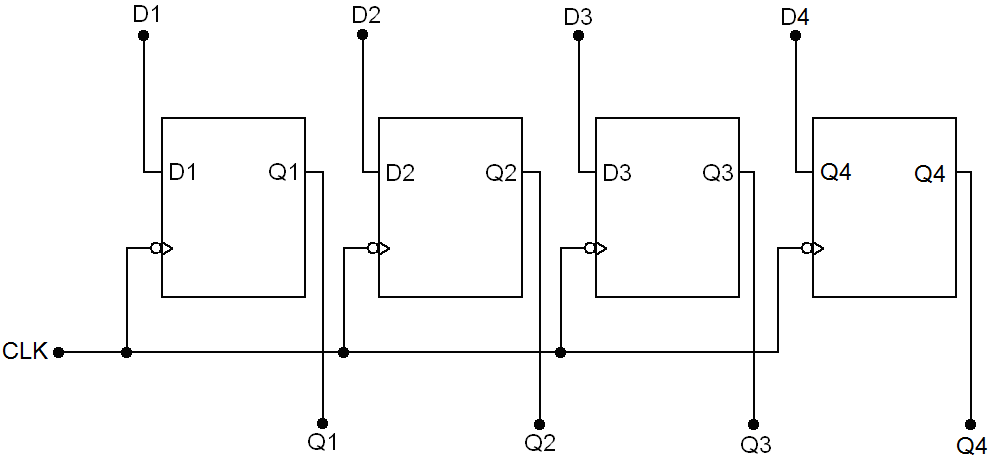

Neste registrador todos os bits são armazenados simultaneamente. Ele é constituído de FF com as entradas de clock ligadas em comum. Quando ocorre a transição positiva do clock, os dados de D1 a D4 são armazenados nas saídas Q1 a Q4. A Figura 1 mostra um circuito registrador do tipo porta paralela.

Figura 1 - Registrador do tipo "Porta Paralela".

| Clock | D1 | D2 | D3 | D4 | Q1 | Q2 | Q3 | Q4 |

|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 0 | 1 | 0 | ? | ? | ? | ? |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | |

| 0 | X | X | X | X | 1 | 0 | 1 | 0 |

Registradores deste tipo são também conhecidos por LATCHES ou FLIP-FLOP do tipo D. Existem disponíveis comercialmente registradores de diversos tamanhos como mostrado anteriormente.

Registradores de deslocamento

É um registrador no qual os FF são conectados de forma a permitir, além da inserção a operação de deslocamento dos bits da palavra binária. A importância das operações de deslocamento dos bits está no fato destas viabilizarem, entre outras, a realização de um grande número de operações lógicas e aritméticas em um sistema digital. Os bits de uma registrador podem ser transmitidos de duas maneiras:

Em série: os bits da palavra são transferidos em sequência (um após o outro) por um único fio. Este formato economiza circuitos.

Em paralelo: os bits da palavra são transferidos simultaneamente por um número de fios igual ao número de bits. Este formato economiza tempo. Assim, levando-se em consideração as formas possíveis para se transmitir uma palavra, pode-se inserir e retirar os bits em um registrador de maneira serial ou paralela. Desta forma, é possível a implementação de 4 tipos básicos de registradores:

- Entrada e saída serial;

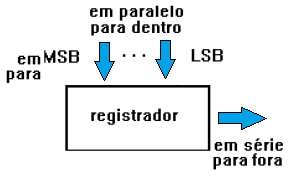

- Entrada paralela e saída serial;

- Entrada serial e saída paralela;

- Entrada e saída paralela.

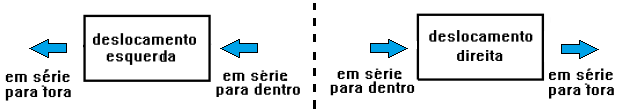

Entrada e saída serial

Suponha que voce deseja armazenar no registrador o dado de 4 bits "1010". Como o registrador desloca os dados da esquerda para a direita o primeiro bit a entrar é 0 da direita, chamado de LSB (Least Significant Bit). São necessários 4 transições negativas do clock para que o dado entre no registrador. O último bit a entrar é o 1 da esquerda, chamado de MSB (Most Significant Bit). A Figura 2 apresenta o diagrama de blocos para esse tipo de registrador.

Figura 2 - Diagrama de blocos do registrador entrada e saída serial.

Considerando-se o sentido de movimento dos dados pode-se ter:

- Deslocamento para a direita;

- Deslocamneto para a esquerda;

- Bidirecional.

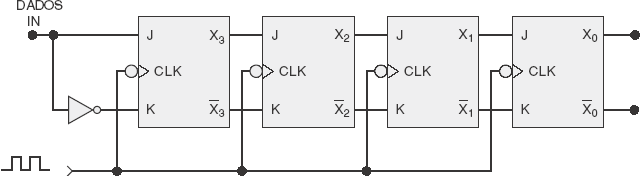

A Figura 3 mostra um registrador de deslocamento de 4 bits e na Figura 4

é apresentado o seu diagrama de tempo da entrada serial dos dados. A cada

pulso de clock, o valor contido nas entradas J e K dos FF é transferido para a

saída. Essa saída está conectada na entrada do próximo FF. Após 4 transições

de descida de clock, o valor das 4 últimas entradas de DADOS, é transferido serialmente para os FF, estando armazenado no registrador nos FF Q, R, S e T.

Figura 3 - Registrador de deslocamento serial para direita.

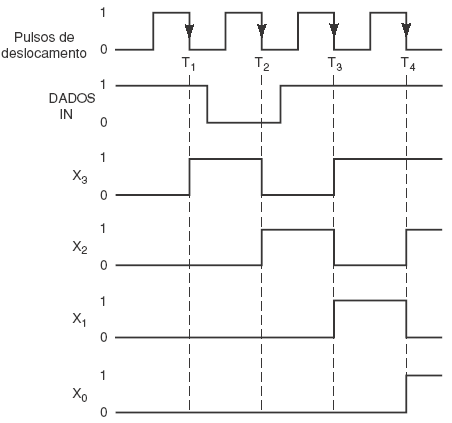

Figura 4 - Diagrama de tempo para o registrador entrada série com deslocamento para a direita.

Para manter estes dados armazenados basta que o sinal de clock seja desativado

(0). Caso se deseje retirar os dados do registrador utiliza-se 4 transições

negativas do clock. A saída dos dados ocorre de forma serial no ultimo

FF (T) conforme mostrado na Fig. 6-9. OBS: Para facilitar o acompanhamento

da saída destes dados (1010) a entrada de dados foi mantida em zero.

(propor construir o registrador de deslocamento utilizando FF tipo D)

Entrada serial com saída paralela

A Figura 5 apresenta o diagrama de blocos deste tipo de registrador. Neste caso, os dados são deslocados em série para dentro (como já mostrado). Para se ter os dados em paralelo basta ter acesso a todas as saídas dos FF do registrador de deslocamento.

Figura 5 - Diagrama em blocos para o registrador entrada série com saída paralela.

Entrada paralela e saída serial

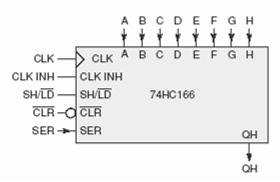

Para este tipo de registrador são incorporadas habilidades para entrada em paralelo e deslocamento dos dados. A análise será feita a partir do 74LS166 que possui entrada serial e paralela e saída serial. A Figura 6 mostra o diagrama de blocos deste registrador. Os diagramas lógicos e tabela funcional é mostrados na Figura 7 e 8. Para realizar a entrada paralela dos dados, altera-se a entrada LOAD (carregar) para 0, e na transição positiva do clock os FF têm suas saídas simultaneamente alteradas de acordo com as entradas A a H. Quando a entrada LOAD está em 1 (SHIFT), o registrador funciona como um registrador de deslocamento. A entrada CLEAR permite zerar todas as saídas dos FF imediatamente (sem o clock).

Figura 6 - Diagrama em blocos para o registrador entrada paralela e saída serial.

Figura 7 - Diagrama lógico do 74166.

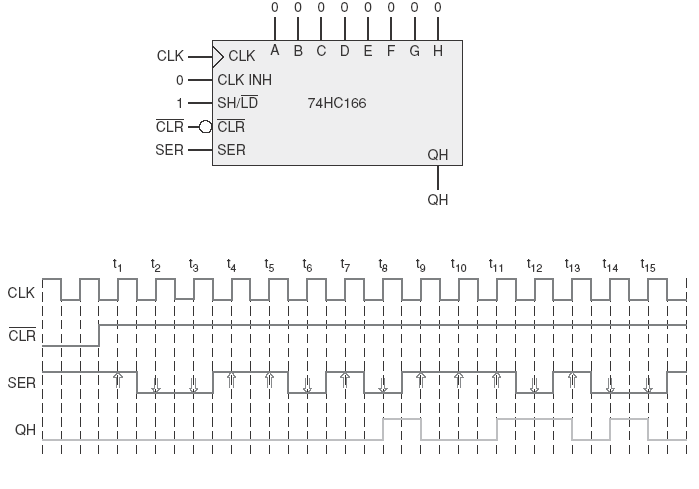

Exemplo: 74ALS166 e 74HC166

- Apenas a saída serial QH é disponível.

- Dados seriais entram no pino SER.

- Dados paralelos podem ser carregados de forma síncrona.

- Funcionamento serial se SH/LD' = 1

- Carga paralela de dados se SH/LD' = 0

- Deslocamento síncrono e carga paralela desabilitados se CLK INH = 1 (clock-inhibit) – FFs mantêm estado anterior.

Figura 8 - Diagrama lógico do 74166.

O primeiro bit aparece em QH em t8, 8 pulsos de relógio após CLR' ter ido para o nível baixo.

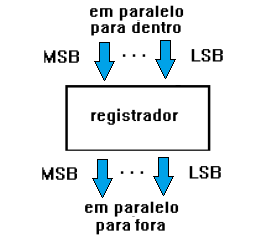

Entrada paralela e saída paralela

A Figura 9 mostra o diagrama de blocos para o registrador do tipo entrada paralela e saída paralela.

Figura 9 - Diagrama de blocos.

Este tipo de registrador pode ser implementado conforme mostrado na Figura 10, porém não é considerado propriamente um registrador de deslocamento. Entretanto, em algumas aplicações é necessário que o registrador seja de deslocamento. Por isso, existem CIs comerciais que são registradores de deslocamento com entradas e saídas paralelas. O CIs 74LS195 é um registrador de deslocamento de 4 bit com entradas paralela e serial e saídas paralela e serial.

Figura 10 - Registrador tipo porta paralela.

Como o CI 74195 é possível realizar as seguintes operações:

- Manutenção do estado interno do registrador;

- CLEAR da saída paralela;

- Entrada paralela e saída paralela;

- Entrada série e saída série para a direita;

- Entrada série e saída paralela (com desabilitação do clock após a quarta transição positiva do clock);

- Entrada paralela e saída série a direita.

Aplicações com registradores

Porta paralela

A Figura 10 mostra o uso de uma porta paralela de dados para a a transferência dos dados da entrada D1 a D4 para as saídas Q1 a Q4. A função desse circuito é armazenar um estado de um circuito, até que um novo estado esteja disponível ou seja desejável. A transferência é controlada pelo clock. Na transição negativa do clock os dados são armazenados no registrador X. A transferência ocorre simultaneamente em todos os bits.

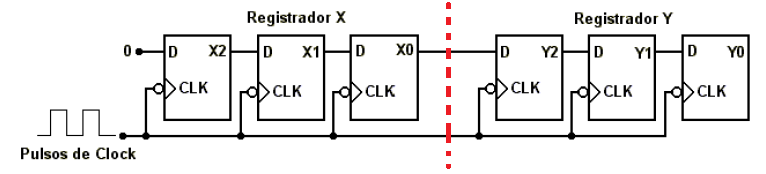

Porta serial

A Figura 11 apresenta a conexão entre dois registradores de deslocamento X e Y para a transferência serial de dados. O clock desses registradores é único, e faz com que a cada transição negativa do clock, o conteúdo do terceiro FF do registrador X é transferido para o primeiro FF do registrador Y, a mesmo tempo que internamente o conteúdo dos FF é deslocado. Após 3 transições negativas do clock, o conteúdo inicial do registrador X é todo transferido para o registrador Y, conforme mostra a Tabela XX.

Figura 11 - Transferência serial entre registradores.

| Clock | Registrador X | Registrador Y | ||||

|---|---|---|---|---|---|---|

| X1 | X2 | X3 | Y1 | Y2 | Y3 | |

| 0 | 1 | 0 | 1 | ? | ? | ? |

| 1 | 0 | 1 | 0 | 1 | ? | ? |

| 2 | 0 | 0 | 1 | 0 | 1 | ? |

| 3 | 0 | 0 | 0 | 1 | 0 | 1 |

Contador em anel

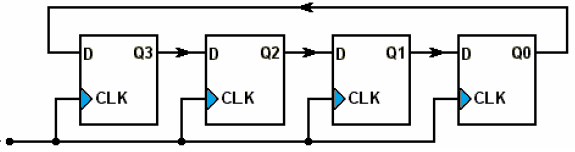

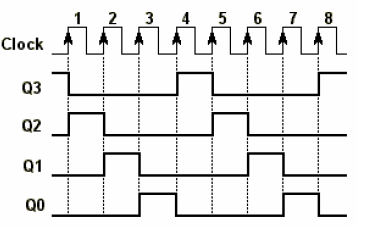

Para o funcionamento deste tipo de contador, um dos FF deve ter inicialmente o valor 1 e os outros 0. Isso pode ser feito através das entradas assíncronas PRESET e CLEAR. Por ser um registrador de deslocamento, o 1 é transferido para o próximo FF a cada clock e da mesma forma os 0s. Os estados se repetem ciclicamente porque a saída do último FF está conectado a entrada do primeiro FF. A Figura 12 mostra um contador em anel e a Figura 13 apresenta a sequência da contagem considerando inicialmente a saída Q3=1 e as outras Q2=Q1=Q0=0.

Figura 12 - Contador em Anel.

Figura 13 - Diagrama de tempo do contador em anel.

Contador Johnson

O contador Johnson é um contador em anel no qual a saída do último FF está conectado a entrada D do primeiro FF, conforme mostrado na Figura 14. Neste tipo de contador todos os FF deve ter inicialmente o valor 0, o que pode ser feito através da entrada assíncronas CLEAR.

Figura 14 - Contador Johnson.

- Exercício

Desenhe o diagrama de tempo correspondente ao funcionamento do Contador Johnson.

Terceiro estado de uma saída (tristate)

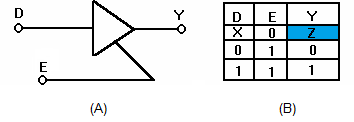

As saídas que podem apenas assumir os estados 0 e 1 são chamadas de Totem-Pole. Diversos circuitos possuem saídas que podem assumir, além dos estados 0 e 1, o estado de alta impedância (tristate) o qual é equivalente a um circuito aberto. As saídas em tristate permitem assim que os computadores sejam organizados em barramentos, conectando diversas saídas de componentes sem provocar a danificação dos mesmos desde que somente um componente seja acionado de cada vez. As saídas dos componentes comportam-se de forma similar a uma chave de três estados. A Figura 15 mostra a simbologia (A) e a tabela verdade (B) para a chave de três estados.

Figura 15 - Simbologia (A) e tabela verdade (B) da chave tristate.

Notem que quando E=0 (enable) a saída Y fica em Z (alta impedância) independente do valor da entrada D.

Circuitos Integrados de Registradores

A seguir são mostrados os diagramas lógicos, pinagens e tabelas funcionais de alguns registradores.

- 74164 – Registrador de deslocamento de 8 bits com entrada serial e saída paralela.

- 74165 – Registrador de deslocamento de 8 bits com entrada serial/paralela e saída serial.

- 74166 – Registrador de deslocamento de 8 bits com entrada serial/paralela e saída serial, com CLEAR assíncrono.

- 74173 – Registrador porta FF de 4 bits com entrada paralela e saída paralela em tristate

- 74194 – Registrador de deslocamento bidirecional universal de 4 bits com entrada paralela e saída paralela

- 74195 – Registrador de deslocamento de 4 bits com entrada paralela e saída paralela

- 74273 – Registrador porta FF de oito bits de entrada paralela e saída paralela.

- 74373 – Registrador porta LATCH de oito bits de entrada paralela e saída paralela em tristate.

- 74374 – Registrador porta FF de oito bits de entrada paralela e saída paralela em tristate.

- 74543 – Transceptor com registradores de oito bits com saídas em tristate.

Lista de Exercícios

Download Exercícios - Registradores

Organização das próximas aulas

Até agora, apresentamos os conceitos relacionados a contadores e registradores. Na próxima aula vamos ter o Laboratório 2 onde iremos montar um relógio digital, a partir de um oscilador com 555 e dois dígitos. Na outra semana vamos começar a falar sobre codificadores e decodificadores, passando por tipos de códigos utilizados como: binário, BCD, Johnson e Gray.

Estudem!

Prof. Douglas A.

Correção da AT1 - 2018-2

Em sala de aula!!!

Estatísticas

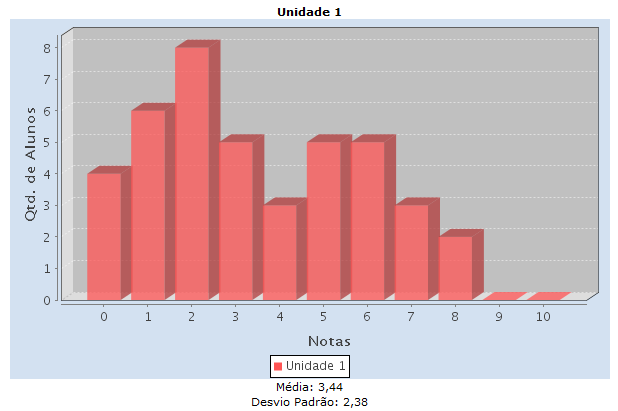

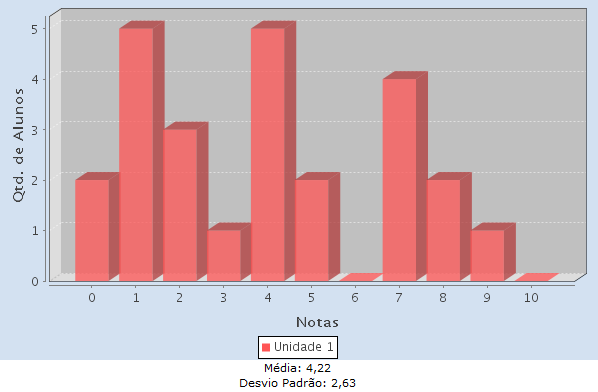

- Interpretação do histograma

- O histograma mostra as notas de 0 a 10 e quantos alunos tiraram essas notas (arredondando os valores). Abaixo dos gráficos, é possível ver a média e desvio padrão de cada unidade.

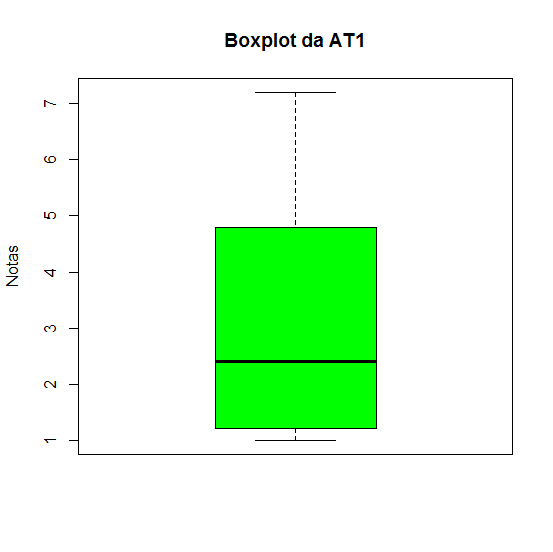

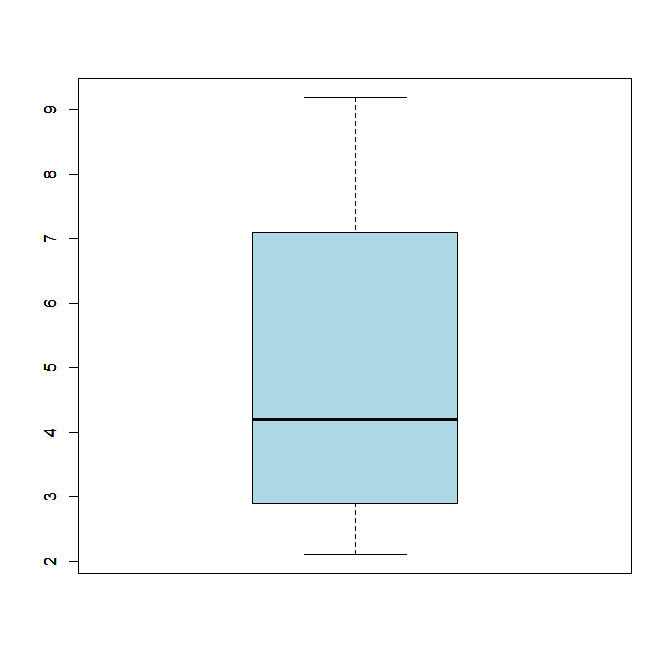

- Interpretação do Box Plot

- O centro da distribuição é indicado pela linha da mediana. A dispersão é representada pela altura do retângulo (Q3 – Q1). O retângulo contém 50% dos valores do conjunto de dados.

2018-2

A Figura abaixo mostra o resultado para este semestre num gráfico de histograma que é obtido a partir do próprio SIGAA, e apresenta os resultados por número de ocorrências de notas. Em relação às avaliações AT1 de semestre anteriores, podemos perceber que a média geral da turma é menor que semestres anteriores. Notas 0 (zero) são alunos que não fizeram a prova. A maior ocorrência foi com a nota 2 (dois) e a maior nota foi 8 (oito).

Histograma da Avaliação Teórica 1 (AT1) - 2018/2

2018-1

A Figura abaixo mostra o resultado deste semestre num gráfico um pouco diferente dos demais semestres. Esse gráfico de histograma é retirado do próprio SIGAA, e apresenta os resultados por número de ocorrências de notas. Em relação às avaliações AT1 de semestre anteriores, podemos perceber que a média geral da turma é maior que a do semestre 2017-2, porém, mais baixa que os demais semestres registrados. Vale lembrar que a legenda do gráfico (unidade 1) se refere a Avaliação Teórica 1.

Histograma da Avaliação Teórica 1 (AT1) - 2018/1

| Semestres anteriores |

|---|

|

2017-2A Figura abaixo mostra o desempenho deste semestre em comparação com os semestres passados. É possível ver no gráfico que as notas foram as mais baixas dos 3 últimos semestres. Talvez a aula de revisão antes da avaliação, com resolução de outras exercícios, pode ter impactado no resultado. Isso aconteceu por causa do SEPEI. De qualquer forma, os exercícios estavam lá e nenhuma aluno me procurou para tirar dúvidas. Vocês estão na engenharia, não é mais ensino médio. Tem que estudar. Boxplot da Avaliação Teórica 1 (AT1) - 2017/2

Min. :1.00 1st Qu.:1.20 Median :2.40 Mean :3.31 3rd Qu.:4.80 Max. :7.20 2017-1A Figura 3 mostra o desempenho deste último semestre em comparação ao semestre passado. É possível ver no gráfico que as notas ficaram mais concentradas, porém com média mais baixa que semestre passado nesta mesma avaliação. Talvez isso signifique que a turma é mais homogênea, embora não tenha alcançado a média para aprovação. Longe disso.

Figura 3 - Boxplot da Avaliação Teórica 1 (AT1) - 2017/1

Min. :1.000 1st Qu.:2.800 Median :3.600 Mean :4.531 3rd Qu.:6.400 Max. :8.400 2016-2Figura 4 - Boxplot da Avaliação Teórica 1 (AT1) - 2016/2

Min. :2.100 1st Qu.:2.900 Median :4.200 Mean :4.805 3rd Qu.:7.100 Max. :9.200 |

Referências

[1] http://www.ufjf.br/fabricio_campos/files/2011/03/cap07_parte_2.pdf