Avaliação 1 - SST

Revisão de 21h56min de 16 de abril de 2015 por Rogerio.j (discussão | contribs) (→Registrador de deslocamento com data-load)

- Avaliação 2 - SST

- Alunos

- Kamila, Leonardo Oliveira e Rogerio.

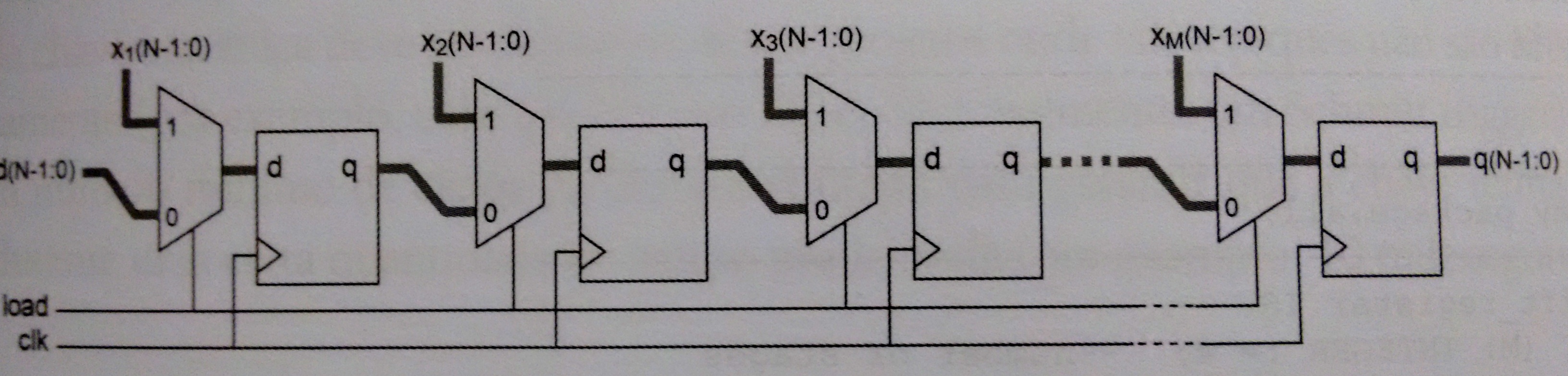

Registrador de deslocamento com data-load

- Um registrador de deslocamento é uma ou mais cadeias de FLIP FLOPS D ligados em serie com o funcionamento de manipulação e armazenamento de dados.

- Um registrador de deslocamento com data load são inseridos multiplexadores apresentando um registrador de deslocamento com capacidade de carregamento do valor inicial.

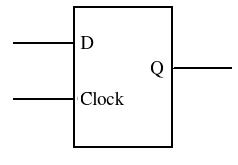

- Flip Flop D

O flip-flop D ("data" ou dado, pois armazena o bit de entrada) possui uma entrada, que é ligada diretamente à saída quando o clock é mudado.

- Código

----- ff_bank (another component) ------ ENTITY ff_bank IS GENERIC (bits: POSITIVE); PORT (d: IN BIT_VECTOR(bits-1 DOWTO 0); clk: IN BIT; q: OUT BIT_VECTOR(bits-1 DOWTO 0)); END ff_bank ---------------------------------------------------- ARCHITECTURE ff_bank OF ff_bank IS BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk='1') THEN q <= d; END IF; END PROCESS; END ff_bank; --------------------------------------

O armazenamento de informação no Flip Flop é feito através das seguintes características no código:

- Sendo o processo sensível apenas à CLK, a informação de entrada será avaliada apenas em casos de alteração nesse sinal.

- A condição CLK = '1' certifica que o corpo da instrução IF será executado apenas na borda de subida do clock(Ou seja a entrada d só terá influencia na saída durante a borda de subida do clock).

- FUNCIONAMENTO

- Quando load = '1', o vetor x é carregado no SR na próxima borda ascendente do clock.

- Quando load = '0' o circuito opera como um SR regular.

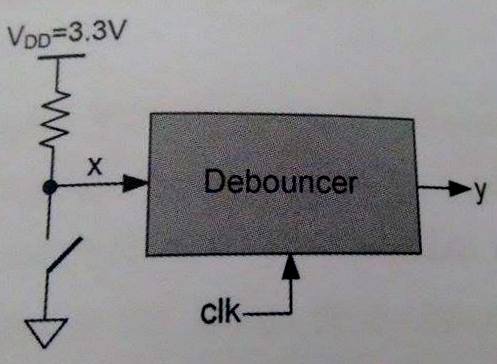

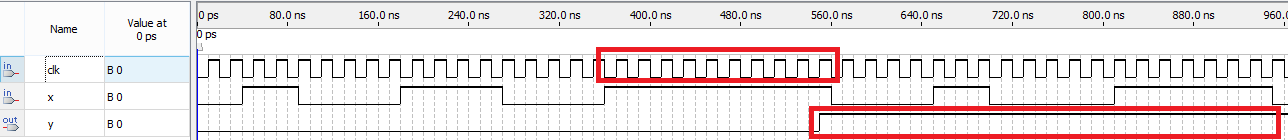

Debouncer para Chave

- FUNCIONAMENTO

- Chave fechada (y='0') : x deve permanecer baixo por no mínimo 10ms sem interrupção.

- Chave aberta (y='1') : x deve permanecer alto por no mínimo 10ms sem interrupção.

- PARÂMETROS

- fclk: inteiro = 1. Define a frequência do clock (kHz);

- twindow: inteiro = 10. Define a janela de tempo (ms);

- x: Valor de entrada (std_logic);

- clk: Valor de clock (std_logic);

- y: Buffer, neste caso variável de saída (std_logic);

- Constant max: Definida por um inteiro resultado da multiplicação das variáveis de entrada [fclk * twindow = (1kHz * 10ms = 10 bordas positivas de clock)].

- Process é sensível a borda de subida do clock;

- Count: Afim de verificar em quantos períodos de clock a entrada x ficou alta/baixa.

- CÓDIGO

library ieee; use ieee.std_logic_1164.all; entity debouncer is generic( fclk: integer := 1; --clock freq in kHz twindow: integer := 10); --time window in ms port( x: in std_logic; clk: in std_logic; y : buffer std_logic); end entity; architecture key of debouncer is constant max: integer := fclk * twindow; begin process(clk) variable count : integer range 0 to max; begin if(clk'event and clk='1') then if(y /= x) then count := count + 1; if(count = max) then y <= x; count := 0; end if; else count := 0; end if; end if; end process; end architecture;

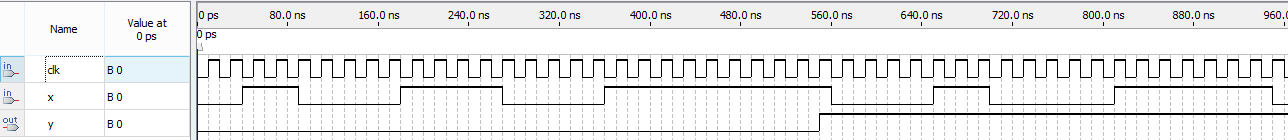

- FORMA DE ONDA