Mudanças entre as edições de "Códigos VHDL para uso nas Aulas"

Ir para navegação

Ir para pesquisar

| Linha 1: | Linha 1: | ||

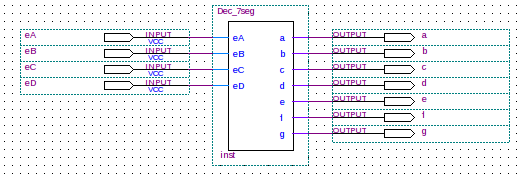

| + | Descrever usando lógica discreta um decodificador de BCD para 7 segmentos. | ||

| + | [[Arquivo:Dec_7seg.png]] | ||

| + | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

entity Dec_7seg is | entity Dec_7seg is | ||

| Linha 14: | Linha 17: | ||

a <= (NOT eD AND NOT eC AND NOT eB AND eA) OR | a <= (NOT eD AND NOT eC AND NOT eB AND eA) OR | ||

(NOT eD AND eC AND NOT eB AND NOT eA); | (NOT eD AND eC AND NOT eB AND NOT eA); | ||

| + | b <= | ||

| + | c <= | ||

| + | d <= | ||

| + | e <= | ||

| + | f <= | ||

| + | g <= | ||

| + | |||

end discret_logic; | end discret_logic; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

Edição das 15h44min de 12 de março de 2012

Descrever usando lógica discreta um decodificador de BCD para 7 segmentos.

entity Dec_7seg is

port

(

eA,eB,eC,eD : in bit;

a,b,c,d,e,f,g : out bit

);

end Dec_7seg;

architecture discret_logic of Dec_7seg is

begin

a <= (NOT eD AND NOT eC AND NOT eB AND eA) OR

(NOT eD AND eC AND NOT eB AND NOT eA);

b <=

c <=

d <=

e <=

f <=

g <=

end discret_logic;